現(xiàn)有的外設(shè)接口的優(yōu)缺點(diǎn):

電路連接都是有VCC,GND兩根電源線的,后面不再贅述了。應(yīng)用的外設(shè)都局限在板載的一些低速低通信量芯片或模塊,高性能或特殊需求的外設(shè)接口和此文無(wú)關(guān)。

單線總線(1-wire)

如18B20,硬件鏈接只需一根數(shù)據(jù)線,非常簡(jiǎn)單,但在編程和CPU效率上卻很不理想,沒有中斷通知,通訊速率很低,而且在一個(gè)完整訪問(wèn)周期內(nèi)不允許被中斷。

I2C總線

I2C 接口的EEprom,只需要I2C兩根接線,cpu主動(dòng)讀寫數(shù)據(jù)。

I2C 接口的 溫濕度傳感器芯片,只需要I2C兩根接線,需要cpu主動(dòng)查詢。

I2C 接口的多軸重力加速度傳感器,除了I2C兩根接線外還需要一根中斷線通知CPU狀態(tài)有變化。

I2C 接口的觸摸屏,除了I2C兩根接線外還需要一根中斷線,一根復(fù)位/喚醒線。

通信速率較低,可以掛接多個(gè)從設(shè)備。總的來(lái)講I2C接口還是比較簡(jiǎn)潔的,編程也不太復(fù)雜。

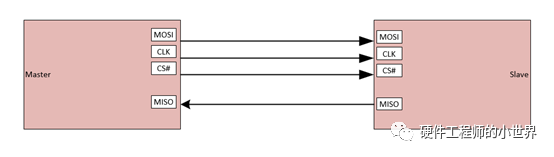

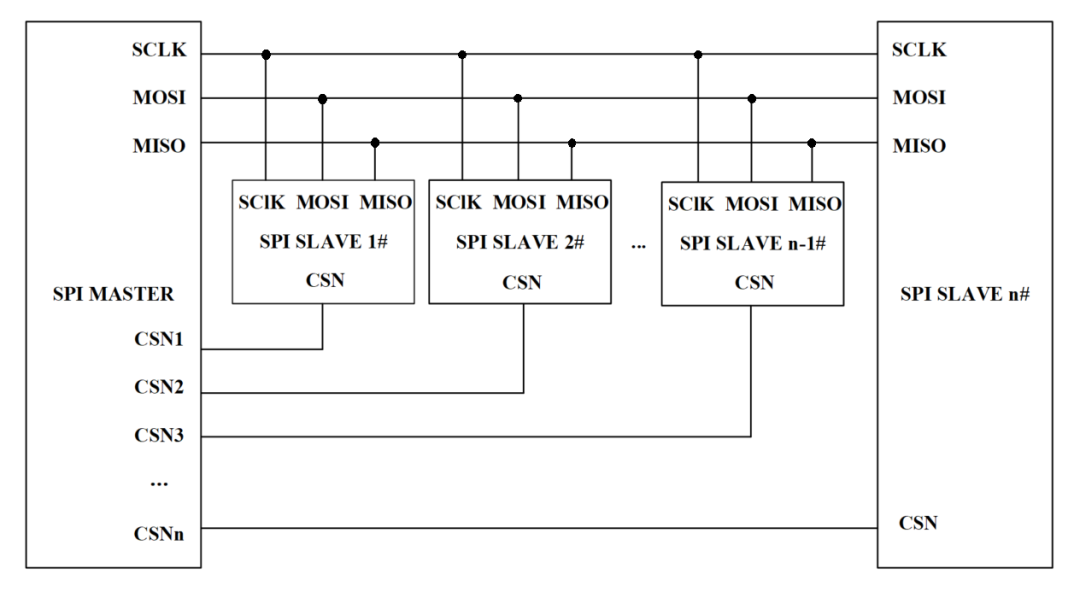

SPI總線

SPI接口的無(wú)線模塊,SPI 4根線,一根中斷線,一根復(fù)位/喚醒線,共計(jì)6根線。

SPI接口通信速率較高,但鏈接線數(shù)較多,尤其在掛接多個(gè)從設(shè)備時(shí),每多一個(gè)設(shè)備都要多一條片選線和中斷線。另外SPI接口雖然是全雙工接口,可到目前為止我還從來(lái)沒見過(guò)使用全雙工的情況。

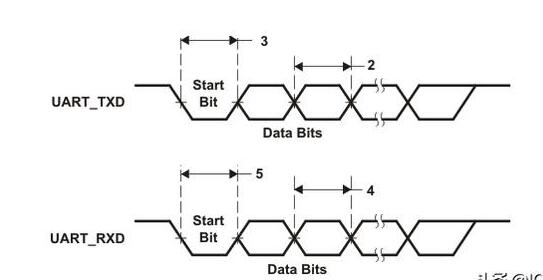

串口

Uart接口的從器件,自帶收發(fā)中斷,一般就收發(fā)兩根線,為異步通信,通信速率低距離較短,為兩主機(jī)對(duì)話模式,作為從機(jī)接口的話,編程相對(duì)復(fù)雜。

USB總線

差分兩線鏈接,硬件鏈接很簡(jiǎn)單,速率高,距離遠(yuǎn),但芯片實(shí)現(xiàn)復(fù)雜,軟件協(xié)議也很復(fù)雜,不適用于板載的低成本低功耗低復(fù)雜度從屬器件。

雖然I2C,SPI總線都是可掛接多個(gè)從設(shè)備,但實(shí)際開發(fā)中大多數(shù)都是只掛一個(gè)從設(shè)備;即使真得要掛接多個(gè)從設(shè)備,在軟硬件設(shè)計(jì)上也要多加小心,系統(tǒng)魯棒性不是很好。另外實(shí)現(xiàn)中斷通知,復(fù)位喚醒還需要借助額外的gpio引腳連接和中斷響應(yīng)處理,不夠簡(jiǎn)潔。

而且有SPI,Uart還有多種硬件鏈接上的擴(kuò)展或變體,使得軟硬件設(shè)計(jì)不好統(tǒng)一處理。

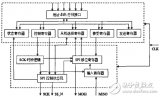

基于以上情況,個(gè)人構(gòu)想(不著邊際,胡思亂想)這樣一種從設(shè)備總線,適用于通信量不是很大(幾字節(jié)到幾K字節(jié)),速率要求不高(100K~100Mbps),距離不是很遠(yuǎn)(1~100cm),有中斷通知,休眠喚醒,硬件復(fù)位等操作需求的情況。主要是在I2C總線基礎(chǔ)上實(shí)現(xiàn),命名為

TWI(tow wire interface)

特性如下:

1. 只需兩根線,3.3V TTL電平,不需要額外擴(kuò)展硬件線路,鏈接簡(jiǎn)單易實(shí)現(xiàn)。簡(jiǎn)潔統(tǒng)一的電路接口,標(biāo)準(zhǔn)易擴(kuò)展的報(bào)文協(xié)議。

2. 只接一個(gè)從設(shè)備,免去了片選信號(hào)或地址字段,消除了總線競(jìng)爭(zhēng)會(huì)引發(fā)的各種異常,因而大幅簡(jiǎn)化了芯片和軟件復(fù)雜度。

3. 為同步傳輸方式,類似I2C總線,一根時(shí)鐘線,一根數(shù)據(jù)線。相比于異步傳輸抗干擾強(qiáng),通信速率高。即便用gpio模擬該總線,在通信中因CPU中斷響應(yīng)而拉長(zhǎng)比特位也不影響傳輸準(zhǔn)確性。

4. 時(shí)鐘線由主機(jī)推挽輸出,從機(jī)為輸入端,空閑時(shí)為高電平,如果芯片處于休眠狀態(tài),時(shí)鐘線置低能喚醒從機(jī)。

數(shù)據(jù)線為半雙工方式,主從都可為輸入模式,或開漏輸出模式,需要外部電阻上拉,所以空閑時(shí)也為高電平。在空閑狀態(tài)下,如果從器件有消息通知主機(jī),可以發(fā)送一個(gè)低電平脈沖,這時(shí)主機(jī)中斷響應(yīng),待數(shù)據(jù)線被從機(jī)釋放恢復(fù)高電平后,主機(jī)方可發(fā)送數(shù)據(jù)。

在通信過(guò)程中如果從機(jī)出現(xiàn)忙碌,故障等問(wèn)題也可一直保持?jǐn)?shù)據(jù)線拉低,主機(jī)則一直等到從機(jī)釋放數(shù)據(jù)線后,才可繼續(xù)通信,查詢從機(jī)狀態(tài)。

5. 通信以字節(jié)為單位,每字節(jié)8位,高位先出。每次通信必須為一個(gè)完整報(bào)文,報(bào)文格式固定但長(zhǎng)度不定。

通信中每發(fā)一字節(jié)不需要有應(yīng)答過(guò)程,I2C每收發(fā)一字節(jié)都有一個(gè)應(yīng)答過(guò)程,這會(huì)使得芯片電路和軟件實(shí)現(xiàn)變得復(fù)雜,同時(shí)也影響通信速率。SPI就沒有校驗(yàn)位,校驗(yàn)可以在報(bào)文收發(fā)完成后整體校驗(yàn)。

6.每個(gè)從機(jī)都有一個(gè)最多128字節(jié)的寄存器組,報(bào)文通信就是讀取或改寫這一組寄存器值。電路上通過(guò)移位寄存器便可以實(shí)現(xiàn)。

對(duì)于一般的傳感器或控制器,這最大的128個(gè)字節(jié)足夠一個(gè)報(bào)文就傳輸足夠多的信息。對(duì)于加大數(shù)據(jù)訪問(wèn)量的芯片則需要通過(guò)寄存器間接訪問(wèn)了。如對(duì)于存儲(chǔ)類芯片則不夠,可以先一個(gè)短報(bào)文設(shè)定內(nèi)存訪問(wèn)地址,后一個(gè)起始地址設(shè)為127,讓首字節(jié)自后的數(shù)據(jù)訪問(wèn)內(nèi)存。SPI接口的無(wú)線模塊很多就是類似這樣的方式。

7.報(bào)文的首字節(jié)高7位為寄存器地址(0~127),最低位為讀寫控制位(0為寫1為讀),表明第二字節(jié)從哪一個(gè)寄存器開始讀寫。

如果報(bào)文首字節(jié)為0,即表示要從0寄存器開始寫,從機(jī)要忽略后面的數(shù)據(jù),當(dāng)數(shù)據(jù)長(zhǎng)度大于等于4字節(jié)時(shí),從機(jī)要進(jìn)行硬件復(fù)位,復(fù)位后處于接收模式,等待主機(jī)命令。所以從機(jī)的0號(hào)寄存器應(yīng)當(dāng)不分配其他功能位。

與I2C相比是

去掉了起始位,停止位處理

去掉應(yīng)答

去掉多主機(jī)多從機(jī)情況

去掉報(bào)文10位設(shè)備地址的情況

增加寄存器地址段

增加硬件喚醒復(fù)位功能

增加中斷觸發(fā)功能

與SPI相比是

去掉了片選信號(hào)

將收發(fā)兩線合并成一線

SPI的4種電平相位模式統(tǒng)一為一種

增加硬件喚醒復(fù)位功能

增加中斷觸發(fā)功能

可以看做是I2C與SPI總線的結(jié)合體變種,電路連接類似于I2C,而字節(jié)傳輸協(xié)議和芯片實(shí)現(xiàn)方式類似于SPI,但軟硬件實(shí)現(xiàn)起來(lái)都更簡(jiǎn)潔。

-

USB總線

+關(guān)注

關(guān)注

1文章

70瀏覽量

37062 -

SPI總線

+關(guān)注

關(guān)注

4文章

104瀏覽量

27666 -

I2C總線

+關(guān)注

關(guān)注

8文章

406瀏覽量

61167 -

TWI總線

+關(guān)注

關(guān)注

0文章

5瀏覽量

9571 -

外設(shè)接口

+關(guān)注

關(guān)注

0文章

9瀏覽量

8208

原文標(biāo)題:一種新型外設(shè)接口的構(gòu)想

文章出處:【微信號(hào):changxuemcu,微信公眾號(hào):暢學(xué)單片機(jī)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

SPI接口的概念,數(shù)據(jù)傳輸, 時(shí)鐘極性、時(shí)鐘相位以及優(yōu)缺點(diǎn)解析

一種新型外設(shè)接口的構(gòu)想

XILINX MIG(DDR3) IP的AXI接口與APP接口的區(qū)別以及優(yōu)缺點(diǎn)對(duì)比

SPI串行外設(shè)接口的優(yōu)缺點(diǎn)是什么

高速DSP串行外設(shè)接口設(shè)計(jì)

理解ATE SPI (串行外設(shè)接口)

正投、背投、吊裝以及桌面安裝的優(yōu)缺點(diǎn)解析

一文讀懂SPI串行外設(shè)接口

基于DSP的串行外設(shè)接口設(shè)計(jì)方案解析

ofdm技術(shù)的優(yōu)缺點(diǎn)解析,ofdm技術(shù)原理介紹

芯片外設(shè)接口的功能

風(fēng)力發(fā)電的優(yōu)缺點(diǎn)以及技術(shù)原理的解析

SPI串行外設(shè)接口的特點(diǎn)概述

SPI串行外設(shè)接口設(shè)計(jì)實(shí)現(xiàn)

現(xiàn)有的外設(shè)接口的優(yōu)缺點(diǎn)解析以及一種新型外設(shè)接口的構(gòu)想

現(xiàn)有的外設(shè)接口的優(yōu)缺點(diǎn)解析以及一種新型外設(shè)接口的構(gòu)想

評(píng)論