第二代串行RapaidIO logicore IP 端點解決方案,符合 RapidIO Gen 2.1 規(guī)范要求,其包含一個高度靈活且優(yōu)化的串行 RapidIO 物理層內(nèi)核和一個邏輯 (I/O) 與傳輸層內(nèi)核。此 IP 解決方案將以網(wǎng)表的形式為示例設(shè)計代碼提供支持。Gen 2 IP 支持 1 倍、2 倍和 4 倍的信道寬度。其配套提供可配置的緩存設(shè)計、參考時鐘模塊、復位模塊以及配置結(jié)構(gòu)參考設(shè)計,為特定應用選擇所需的功能模塊提供了高度的靈活性。該解決方案提供 Verilog 設(shè)計環(huán)境支持。此 IP 核將為數(shù)據(jù)路徑提供 AXI-4Streaming 接口,并為配置(維護)事務處理提供 AXI-4 Lite 接口。設(shè)計此內(nèi)核的目的是為了確保時序的可預測性,從而可大幅降低工程設(shè)計時間的投入,并將資源主要應用于用戶特定的應用邏輯中。

如需了解 Serial RapidIO Gen 1.3(是對 Gen 2.5G 線速的擴展)Xilinx LogiCORE IP 核,請訪問Serial RapidIO LogiCORE IP

主要性能和優(yōu)勢

1 倍、2 倍和 4 倍寬度的串行物理層 - 支持 Artix-7、Kintex-7、Zynq-7000、Virtex-7 和 Virtex-6 FPGA

1 倍、2 倍和 4 倍寬度的串行物理層 - 支持 1.25、2.5、3.125、5.0 和 6.25 Gpbs 線速

支持 IDLE1 和 IDLE2 序列

支持數(shù)據(jù)包重試、stomp、傳輸錯誤恢復、基于節(jié)流閥的流量控制和 CRC

為所有外發(fā)的數(shù)據(jù)包提供 8/16 位器件 ID、可編程源 ID 支持

支持基于優(yōu)先級的重新發(fā)送抑制

提供獨立的、可配置 8/16/32 數(shù)據(jù)包 TX 和 RX 緩沖深度

為數(shù)據(jù)路徑提供 AXI4-Stream 接口,并為配置提供 AXI4-Lite 接口

特色技術(shù)文檔

Vivado 發(fā)布說明

工具和器件支持器件系列支持:

Virtex UltraScale+

Kintex UltraScale+

Zynq UltraScale+ MPSoC

Virtex UltraScale

Kintex UltraScale

Zynq-7000

Virtex-7

Kintex-7

Artix-7

Virtex-6

設(shè)計工具支持:

Vivado Design Suite

ISE Design Suite

支持的工具版本

-

RapidIO

+關(guān)注

關(guān)注

1文章

39瀏覽量

20841

發(fā)布評論請先 登錄

相關(guān)推薦

第二代可穿戴設(shè)備背后的傳感器技術(shù)

中國第二代導航衛(wèi)星系統(tǒng)發(fā)展到了什么程度?

RTC的主要性能指標有哪些

性能超ARM A76!國產(chǎn)第二代“香山”RISC-V開源處理器最快6月流片

白皮書 | 第二代ClearClock?三次泛音晶體振蕩器

黑莓Tour第二代定名9650 即將發(fā)布

燧原科技正式發(fā)布第二代推理產(chǎn)品“云燧i20”

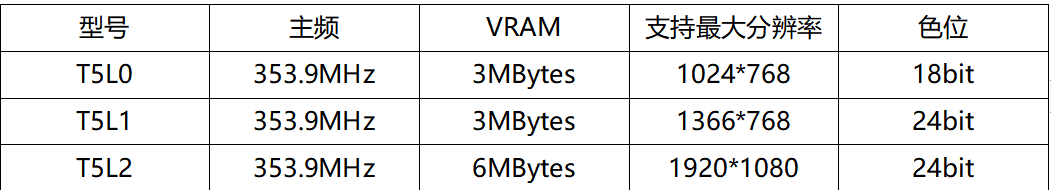

使用迪文第二代DGUS軟件實現(xiàn)突出的GUI性能

第二代串行RapaidIO logicore IP的主要性能及優(yōu)勢

第二代串行RapaidIO logicore IP的主要性能及優(yōu)勢

評論