以下文章來源于ICPMS冷知識(shí),作者gz07apple

集成電路(IC)是由數(shù)億甚至數(shù)十億個(gè)晶體管組成,這些晶體管在硅晶圓上并行工作。但是這些晶體管若不能相互導(dǎo)通,它們就不能實(shí)現(xiàn)指定功能。而這些金屬互連(Metal Interconnect)電路像是血管,確保電子信號(hào)在不同組件之間的順利傳輸。金屬互連中介質(zhì)層(Dielectric layer)的作用,是防止不同金屬層間的電子遷移,將不同金屬層相互隔離,避免物質(zhì)之間的擴(kuò)散或滲透等。

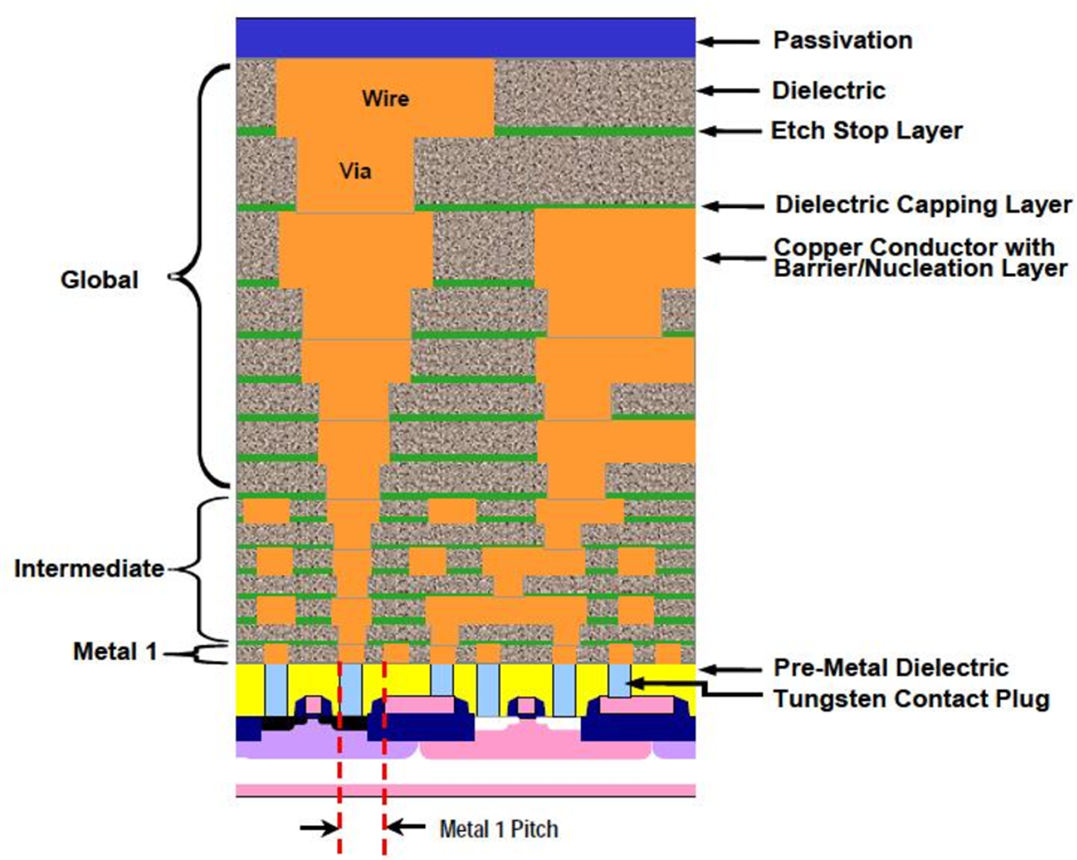

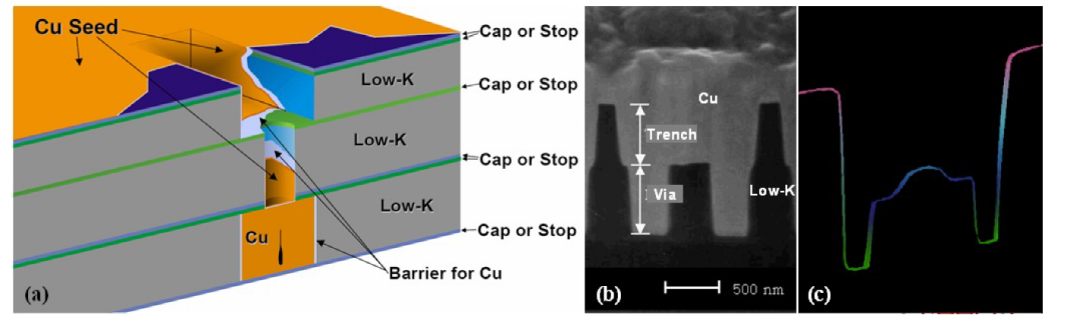

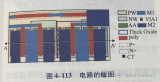

先來看一張金屬互連剖面圖:

一、金屬前介質(zhì)層

剖面圖中黃色區(qū)域?yàn)榻饘偾敖橘|(zhì)層,即PMD(Pre-MetalDielectric)。它位于襯底與第一金屬層(Metal 1)之間,是保護(hù)有源區(qū)免受雜質(zhì)粒子污染的絕緣介質(zhì)層,其沉積效果的好壞直接影響器件的性能。

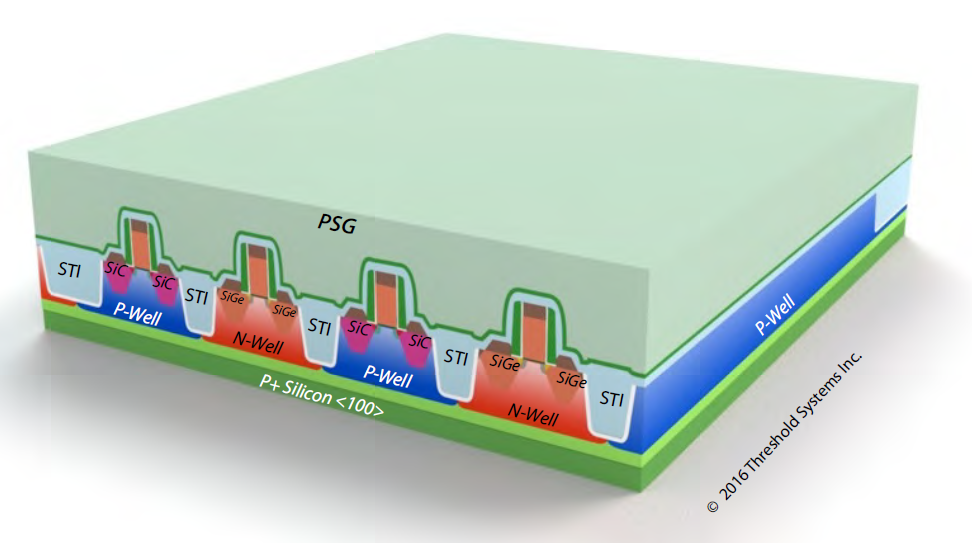

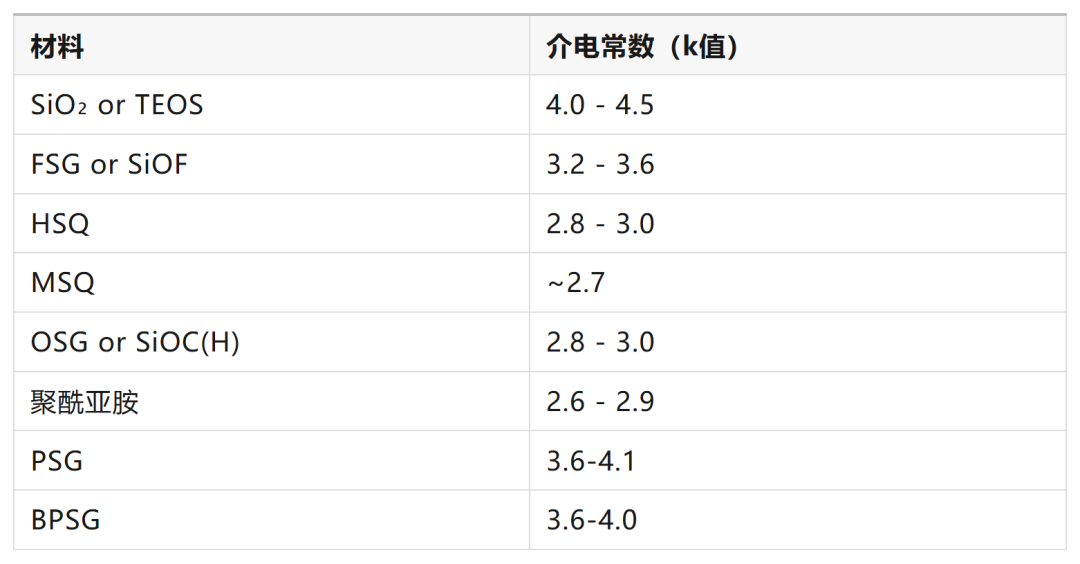

隨著半導(dǎo)體器件尺寸的逐漸減小,沉積金屬前介質(zhì)層時(shí)所要填充的線縫寬度也越來越小,深寬比越來越大,填孔能力成為沉積工藝優(yōu)化的首要目標(biāo)。工藝通常選擇TEOS(正硅酸乙酯)、PSG(磷硅玻璃)或BPSG(硼磷硅玻璃)等材料進(jìn)行填充,利用高密度等離子體化學(xué)氣相沉積(HDPCVD)或次大氣壓化學(xué)氣相沉積(SACVD)工藝來制備金屬前介質(zhì)層。

二、金屬間介質(zhì)層

剖面圖中灰色區(qū)域?yàn)榻饘匍g介質(zhì)層,即IMD(Inter MetalDielectric)。注意,無論金屬前介質(zhì)層還是金屬間介質(zhì)層,都屬于層間介質(zhì)層,即ILD(Inter Layer Dielectric)。兩者區(qū)分在于,金屬前介質(zhì)層位于襯底和第一層金屬之間,而金屬間介質(zhì)層則是位于兩層金屬之間。

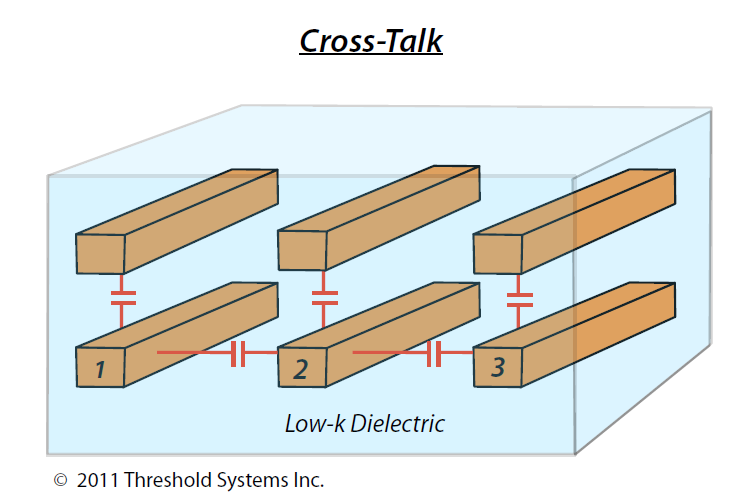

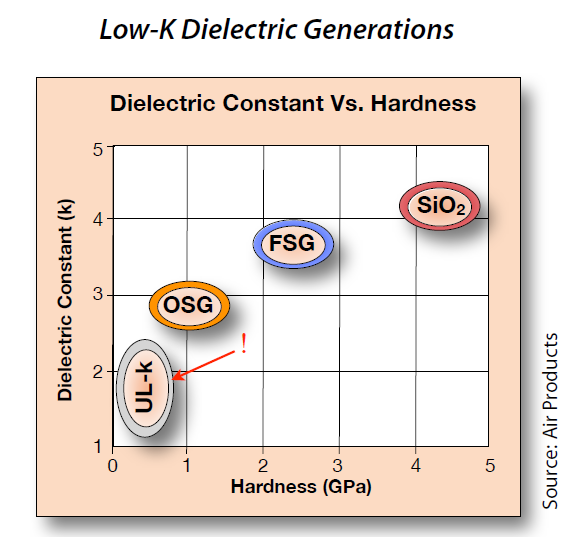

金屬間介質(zhì)層能夠確保每個(gè)金屬互聯(lián)結(jié)構(gòu)的相互獨(dú)立,防止串?dāng)_(Cross-Talk)。工藝通常選擇采用二氧化硅或其它低 k 材料,如FSG(氟硅玻璃)、OSG(有機(jī)硅玻璃)等進(jìn)行填充。比如將硅基前驅(qū)體OMCTS(八甲基環(huán)四硅氧烷)送入等離子體增強(qiáng)化學(xué)氣相沉積(PECVD)反應(yīng)腔,與氧氣反應(yīng)制備SiCO(H)低 k 材料薄膜。

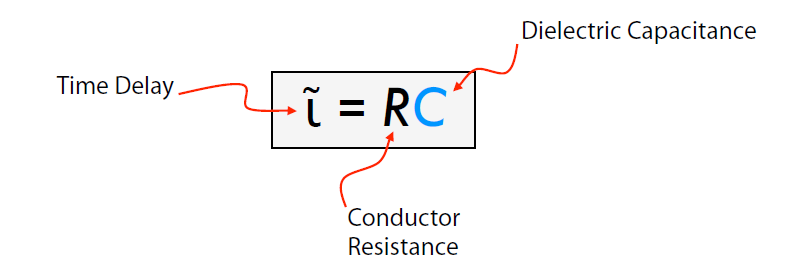

電路導(dǎo)線電阻用R表示,寄生電容用C表示,由于R與導(dǎo)體的橫截面積呈反比,C與電容極板的距離呈反比,因此隨著制程微縮,布線之間的距離減小,電容與電阻均變大,產(chǎn)生RC延遲造成信號(hào)失真,影響芯片工作速度。

降低R與C,R=ρL/S,ρ是電阻率,L是導(dǎo)線長度,S是橫截面積,由于增大導(dǎo)體橫截面積不利于制程微縮,因此降低R的辦法是選取電阻率更低的導(dǎo)體,比如用銅替換鋁,然而在采用銅布線之后,短時(shí)間很難選擇其他導(dǎo)體完全取代銅來繼續(xù)降低電阻。

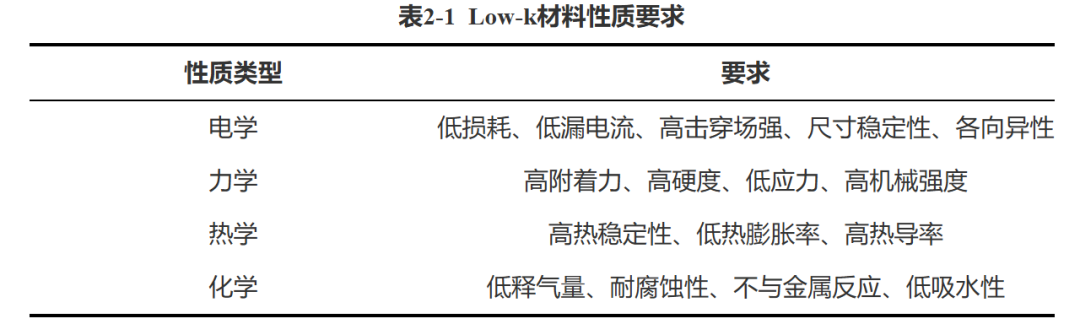

C=kA/d,A是橫截面積,d是介質(zhì)層厚度,降低橫截面積會(huì)導(dǎo)致電阻R增加,增加介質(zhì)層厚度會(huì)導(dǎo)致間隙填充更加困難,因此降低C的辦法通常是降低k值,采用低k 材料替代SiO2。低k材料的工藝壁壘在于保證薄膜較薄同時(shí)實(shí)現(xiàn)足夠的機(jī)械強(qiáng)度、高均勻性等。

三、刻蝕停止層

銅互連工藝需采用大馬士革結(jié)構(gòu)與化學(xué)機(jī)械拋光(CMP)技術(shù),通過刻蝕低k材料獲得溝槽和通孔來完成雙大馬士革圖形化工藝。為了對(duì)RC延遲的影響縮至最小,除了前面提到金屬間介質(zhì)層采用低 k 材料外,刻蝕停止層(Etch Stop Layer,ESL)材料的k 值也應(yīng)盡可能的低,從而降低金屬互連的整體介電常數(shù)值。刻蝕停止層還可作為其下方金屬導(dǎo)線的覆蓋層(Capping Layer),也是金屬擴(kuò)散的阻擋層(Barrier Layer)。

過去刻蝕停止層材料通常選擇Si3N4(k值約為7~8),其厚度必須盡可能薄。近年來也有采用SiCN(k值約為4~5)作為刻蝕停止層。SiCN(硅碳氮)是兼具寬禁帶半導(dǎo)體SiC和絕緣體Si3N4兩者優(yōu)點(diǎn)的新型材料,不僅具有高熱導(dǎo)率、高熱穩(wěn)定性、抗壓、抗輻射等特點(diǎn),而且表面致密,對(duì)硅和二氧化硅都具有很好的附著性。SiCN薄膜通常使用 4MS(四甲基硅烷)作為硅源、氨氣作為氮源,通過 PECVD 工藝制備。

-

集成電路

+關(guān)注

關(guān)注

5392文章

11623瀏覽量

363186 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27711瀏覽量

222650 -

晶體管

+關(guān)注

關(guān)注

77文章

9746瀏覽量

138900

原文標(biāo)題:【推薦】一文了解金屬互連中介質(zhì)層

文章出處:【微信號(hào):深圳市賽姆烯金科技有限公司,微信公眾號(hào):深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

互連中的信號(hào)畸變(信號(hào)完整性揭秘)

光互連技術(shù)發(fā)展面臨的難點(diǎn)

光互連技術(shù)的展望

【我是電子發(fā)燒友】了解以太網(wǎng)術(shù)語 – 數(shù)據(jù)速率、互連介質(zhì)和物理層

片式疊層陶瓷介質(zhì)電容器基礎(chǔ)介紹

車載互連中的TI技術(shù)

電子封裝微互連中的電遷移

電子連接器互連中產(chǎn)生微動(dòng)腐蝕的影響

電子連接器互連中產(chǎn)生微動(dòng)腐蝕的影響

芯片金屬互連中電鍍添加劑的理論與實(shí)驗(yàn)研究

快速串行接口(FSI)在多芯片互連中的應(yīng)用

一文了解金屬互連中阻擋層

詳解金屬互連中介質(zhì)層

詳解金屬互連中介質(zhì)層

評(píng)論