Chiplet封裝的興起

由于受光刻機(jī)工作窗口,以及掩模板材料對光線解析度的限制,芯片的大小被限制在了一個很小的面積上,也就是平常所見的一片郵票大小(約800平方毫米)。

雖然有類似英特爾這種企業(yè),在研發(fā)不計成本的超算CPU芯片時,曾經(jīng)突破過這個尺寸一點點,制造出了“大芯片”(約1200平方毫米),但是并沒有在市場上真正的流行起來。

算力在多線程CPU和超線程GPU的需求下,每個線程的內(nèi)核數(shù)量不斷的堆積,最終把芯片的一些周邊功能元件給擠出了芯片面積有限的裸Die,這些周邊的元器件不得不通過專用的數(shù)據(jù)交換與傳輸器件,在裸Die外與主芯片裸Die進(jìn)行集成,這就是Chiplet封裝集成工藝,由選配進(jìn)入到強(qiáng)需求的原因。

而且隨著主芯片裸Die的內(nèi)核集成規(guī)模越來越大,不但周邊配套的功能元件如緩存、內(nèi)存、數(shù)據(jù)交換與傳輸?shù)龋惨S之功能越來越強(qiáng)大,集成的功能越來越多,成為獨立裸Die趁勢也越來越明顯;而且受芯片有限面積的限制,主芯片裸Die也開始裝不下那么多內(nèi)核,要分拆開來制造,再通過類Chiplet封裝集成工藝,把多個主芯片裸Die給縫制成一顆主芯片模組。

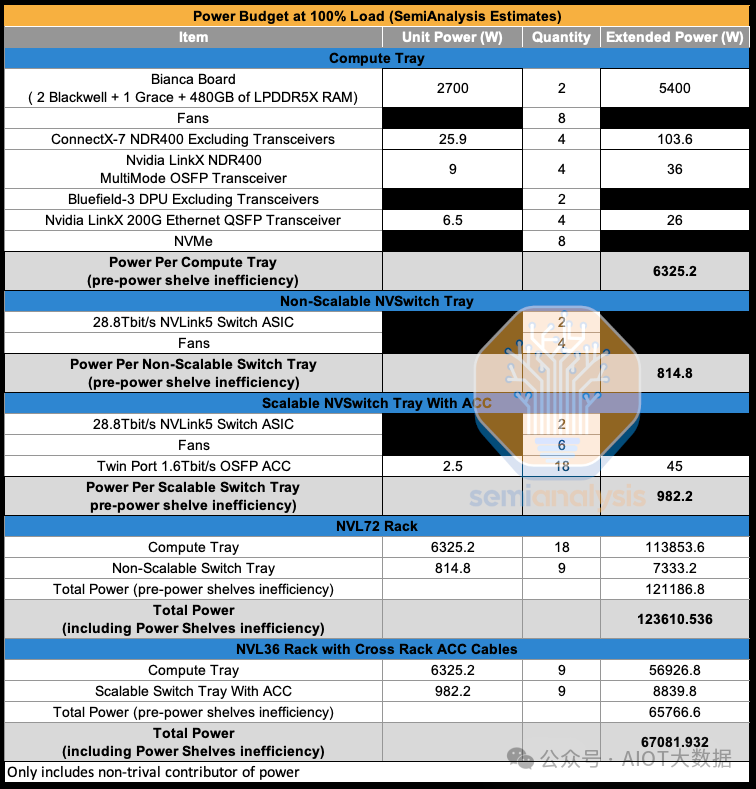

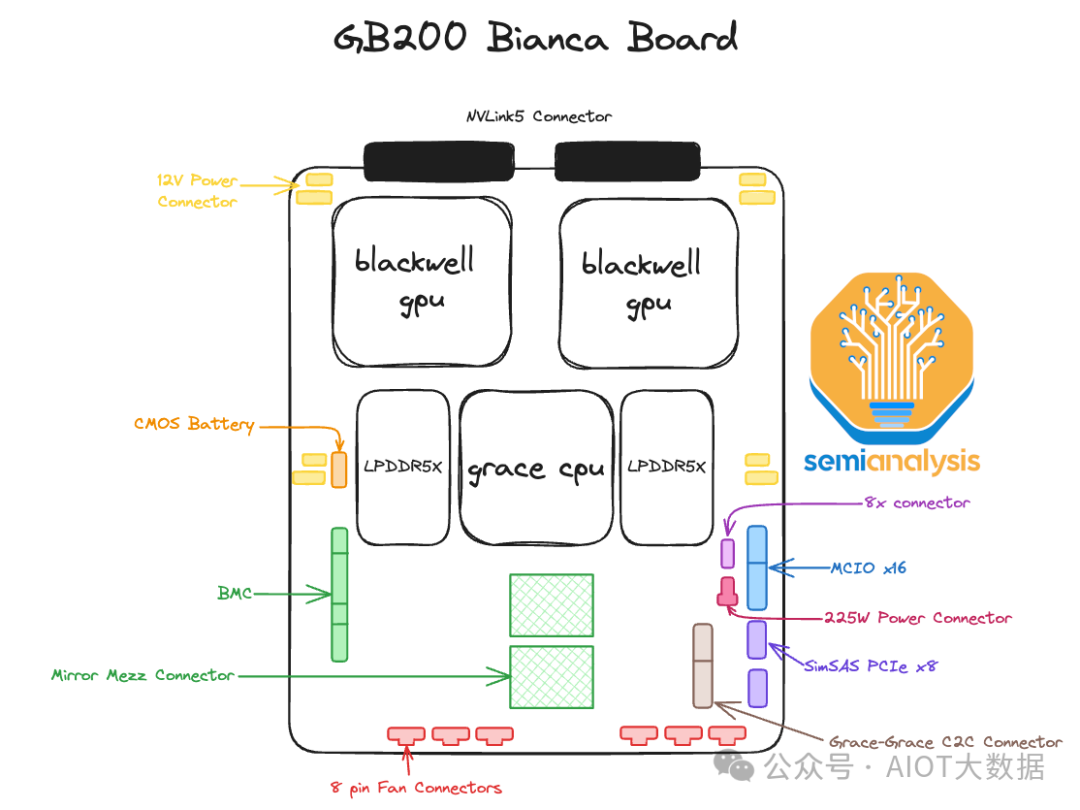

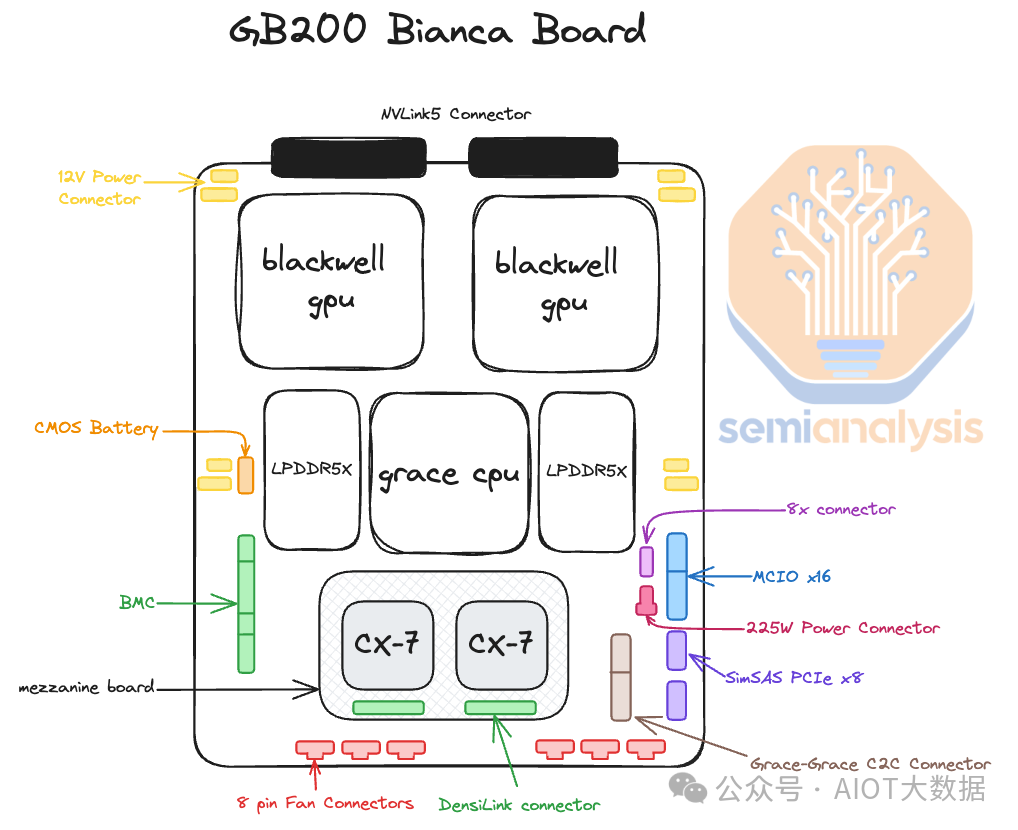

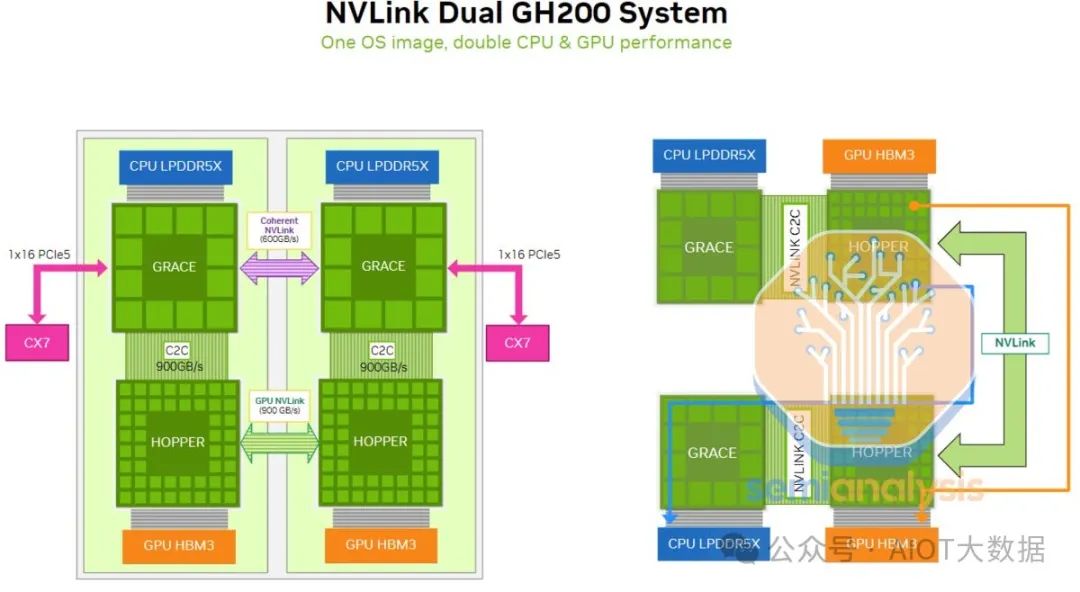

行業(yè)里,除了英特爾、谷歌縫制過類似的超算力芯片外,目前行業(yè)里最火的,就是各大科技公司紛紛爭搶市場配額的英偉達(dá)GB200超級AI GPU芯片組。Nvidia基于Blackwell架構(gòu)的GB200 GPU,其核心是Bianca板,它包含兩個Blackwell B200 GPU和一個Grace CPU,再通過配備兩個28.8Tb/s的NVSwitch5 ASIC 的NVSwitch托盤給連接成不同的單集成柜,目前有GB200 NVL72,GB200 NVL36x2,GB200 NVL36x2(Ariel)和x86 B200 NVL72/NVL36x2四種形態(tài)。

Source:SemiAnalysis GB200 Component & Supply Chain Model

Source: SemiAnalysis

在同一個計算托盤中,有一個高速一致性NVLink連接,可實現(xiàn)高達(dá)600Gb/s雙向帶寬(300Gb/s單向),這個連接速度極快,允許CPU共享資源和內(nèi)存。

Source: SemiAnalysis

另外英偉達(dá)宣稱,GB200 NVLink可以將576個Blackwell GPU連接在一起,行業(yè)分板英偉達(dá)可能會將使用288個L1 NVSwitch5 ASIC (144個1U交換機(jī)托盤),并將使用144個L2 NVSwitch ASIC (72個2U交換機(jī)托盤)位于專用NV Switch托盤上。與NVL36x2類似,因為距離很近,GPU與L1 NVSwitch將使用相同的銅背板相連。

Source: Nvidia

英偉達(dá)這樣做的原因,主要就是Blackwell的硅面積(約1600平方毫米,擁有2080億個晶體管)是之前單裸Die芯片Hopper的兩倍(約800平方毫米,擁有800億個晶體管)。由于摩爾定律的放緩和3納米問題,Nvidia必須在沒有真正工藝節(jié)點縮小的情況下提供一代又一代的性能。通過使用DTCO(Design-Technology Co-Optimization)和輕微的6%光學(xué)工藝縮小,Blackwell仍然能夠提供Hopper兩倍的性能。

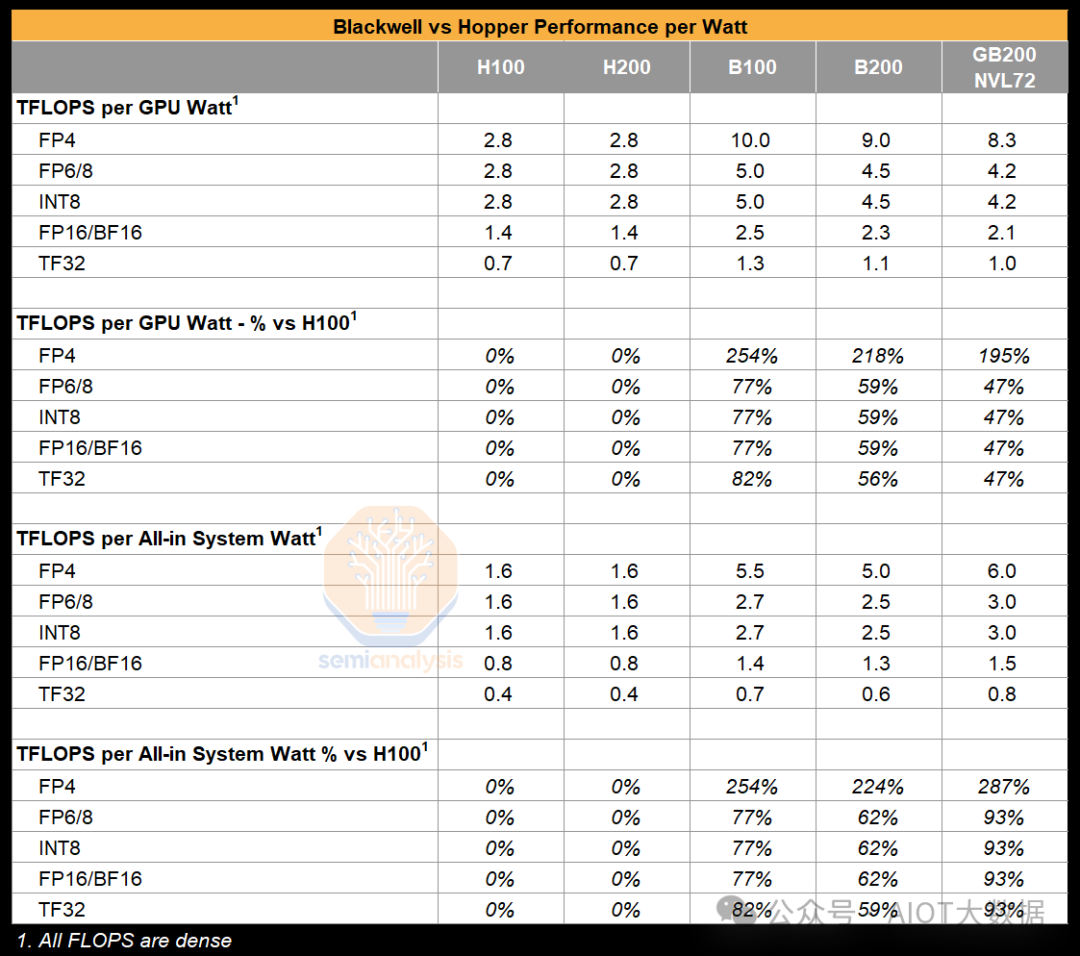

當(dāng)以每平方毫米硅面積的原始TFLOPS來衡量,即與邏輯制造成本進(jìn)行對比時,B100實際上提供了更低的性能,F(xiàn)LOPS提高了77%,而硅面積增長了約100%。這是因為為了迅速上市,需要將時鐘降低以適應(yīng)現(xiàn)有的700瓦平臺,而且只有在B200和GB200 NVL72上才能看到每平方毫米硅面積的改進(jìn)。

通過硅面積增益進(jìn)行歸一化,使用空氣冷卻的B200每平方毫米硅面積只提供了14%的FP16 FLOPS改進(jìn) - 這與一個全新架構(gòu)的預(yù)期相去甚遠(yuǎn)。因為大部分性能增益只是通過增加更多的硅面積和量化來實現(xiàn)的。人們需要了解微擴(kuò)展(microscaling)的工作原理,并解決使用Blackwell架構(gòu)進(jìn)行FP8、FP6和FP4訓(xùn)練的問題。考慮到兩倍的硅面積應(yīng)該需要兩倍的功率,分析等功率性能增益是很重要的,即每瓦特功率GPU所實現(xiàn)的FLOPS:

從圖中可以看出,GB200每瓦特的TFLOPS比H100提高了47%。

因此在同等工藝制程約束下,芯片的面積越大,晶體管的數(shù)量就越多。為了做出地球上最大的芯片,英偉達(dá)的Blackwell芯片尺寸是一整塊wafer(晶圓)在光刻機(jī)曝光極限下所能支持的最大面積:800平方毫米。英偉達(dá)表示,做的再大一點,那么整塊晶圓估計都會因為物理極限而斷裂。

事實上從上面的每瓦特TFLOPS功率效率來看,即便是晶圓在普通情況下,不會因為物理極限而斷裂,也會因為工作時候的熱量聚集而出現(xiàn)物理損壞或功能紊亂問題。臺積電為GB200加工的第一批芯片組Bianca板,就曾經(jīng)因為每瓦特TFLOPS功率太高,造成的熱量聚集不均,出現(xiàn)了傳輸速率不一致,造成運算紊亂,不得不調(diào)低運算速度的BUG,最后英偉達(dá)重新設(shè)計了Bianca板的基板上,RDL再布線中介層線路與觸點,才解決了這個問題。

GB200采用臺積電的CoWoS封裝,先將半導(dǎo)體芯片(CPU、GPU、存儲器等)通過Chip on Wafer(CoW)的封裝制程一起連接至中介層(Interposer)上,再通過Wafer on Substrate(WoS)的封裝制程將硅中介層連接至底層基板上。

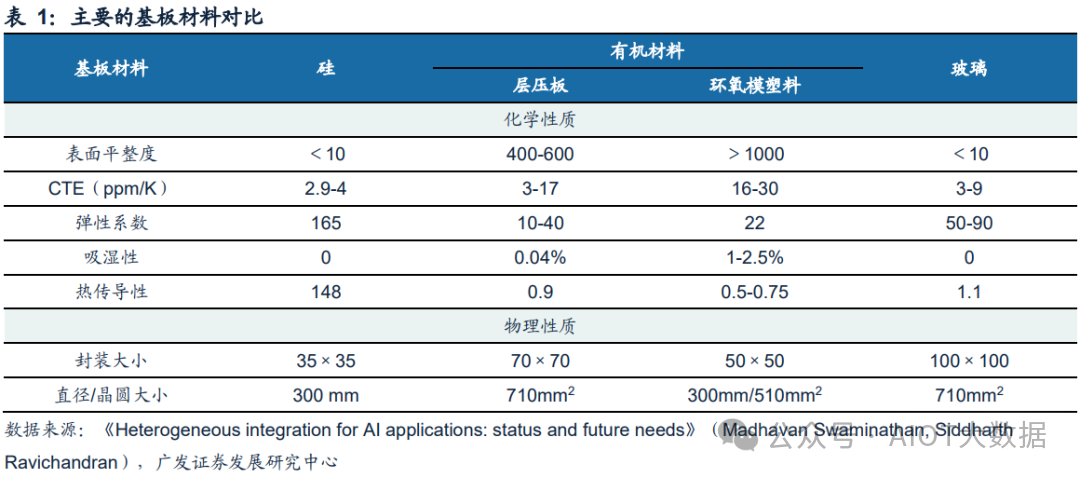

其中,中介層(interposer)一般選用硅(COWOS-S)、有機(jī)物(COWOS-R)或者是硅和有機(jī)物的結(jié)合(COWOS-L)。

GB200芯片組Bianca板在工作時,英偉達(dá)推薦的是把Bianca板整面貼在水冷板上進(jìn)行冷卻工作,以提高散熱性能和降低每瓦特TFLOPS的功耗,提升算力的輸出能力。

玻璃基板的應(yīng)用

在射頻和高功率半導(dǎo)體領(lǐng)域,由于對每瓦功率的散熱要求,以及高頻數(shù)據(jù)傳輸處理的穩(wěn)定性要求,芯片封裝基板從有機(jī)板到金屬板,再到陶瓷板與玻璃基板,不斷的優(yōu)化中。其中玻璃基板由于有著下面這些優(yōu)勢,成為了高功率、高頻率芯片組設(shè)計的主要方向:

(1)低成本:受益于大尺寸超薄面板玻璃易于獲取,以及不需要沉積絕緣層,玻璃轉(zhuǎn)接板的制作成本大約只有硅基轉(zhuǎn)接板的1/8;

(2)優(yōu)良的高頻電學(xué)特性:玻璃材料是一種絕緣體材料,介電常數(shù)只有硅材料的1/3左右,損耗因子比硅材料低 2~3 個數(shù)量級,使得襯底損耗和寄生效應(yīng)大大減小,可以有效提高傳輸信號的完整性;

(3)大尺寸超薄玻璃襯底易于獲取:康寧、旭硝子以及肖特等玻璃廠商可以量產(chǎn)超大尺寸(大于2 m×2 m)和超薄(小于50μm)的面板玻璃以及超薄柔性玻璃材料;

(4)工藝流程簡單:不需要在襯底表面及TGV內(nèi)壁沉積絕緣層,且超薄轉(zhuǎn)接板不需要二次減薄;

(5)機(jī)械穩(wěn)定性強(qiáng):當(dāng)轉(zhuǎn)接板厚度小于100μm時,翹曲依然較小;

(6)應(yīng)用領(lǐng)域廣泛:除了在高頻領(lǐng)域有良好應(yīng)用前景之外,透明、氣密性好、耐腐蝕等性能優(yōu)點使玻璃通孔在光電系統(tǒng)集成領(lǐng)域、MEMS封裝領(lǐng)域有巨大的應(yīng)用前景。

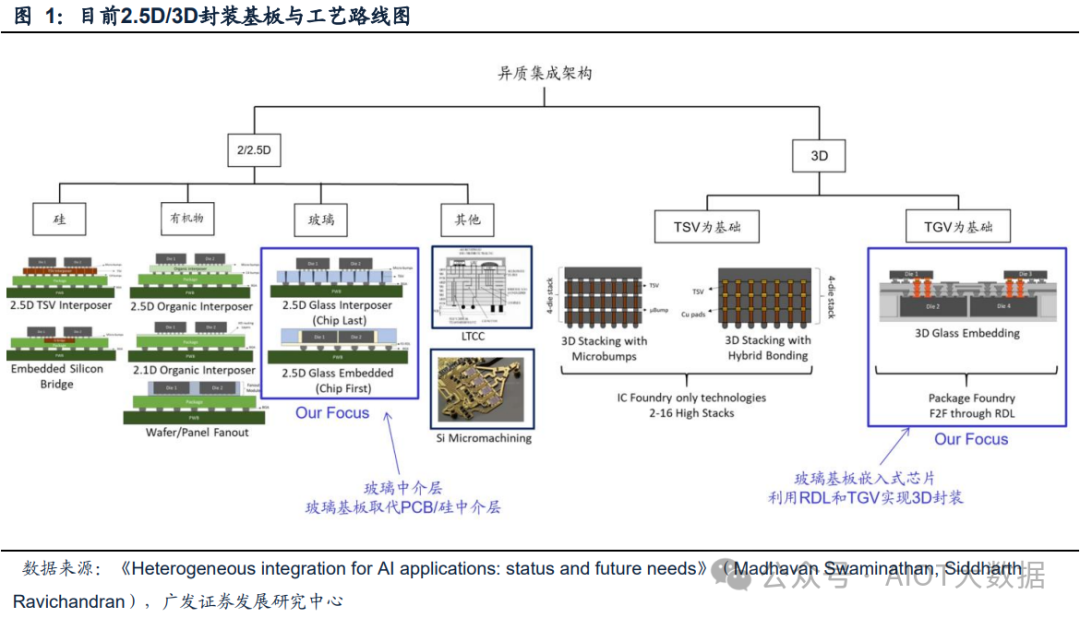

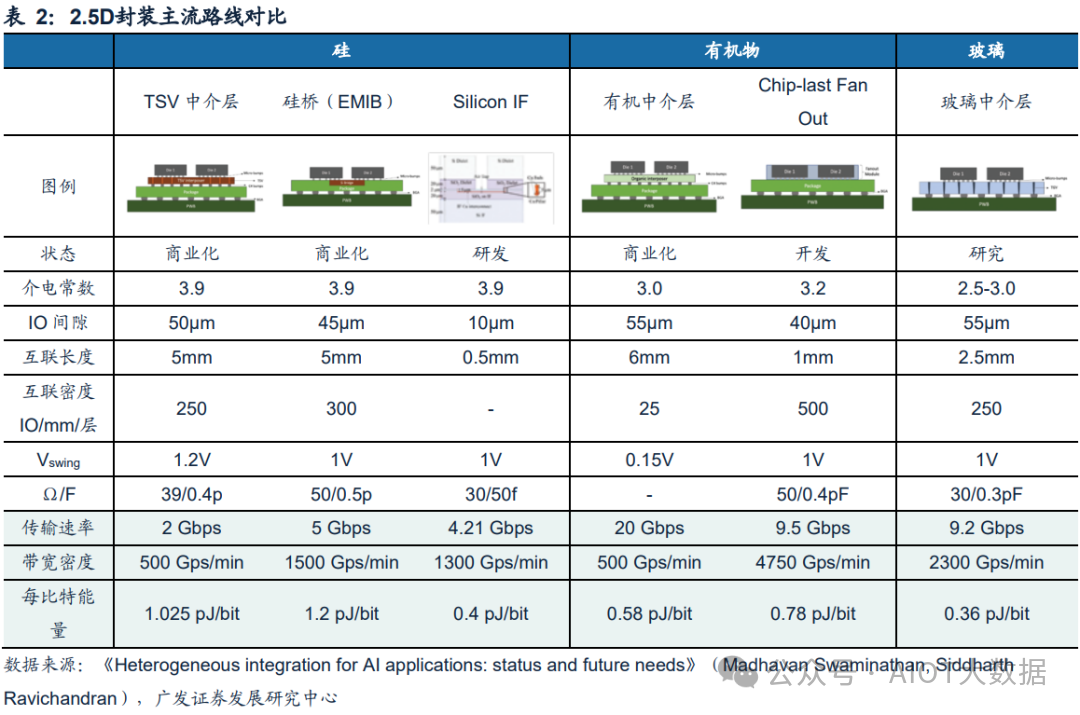

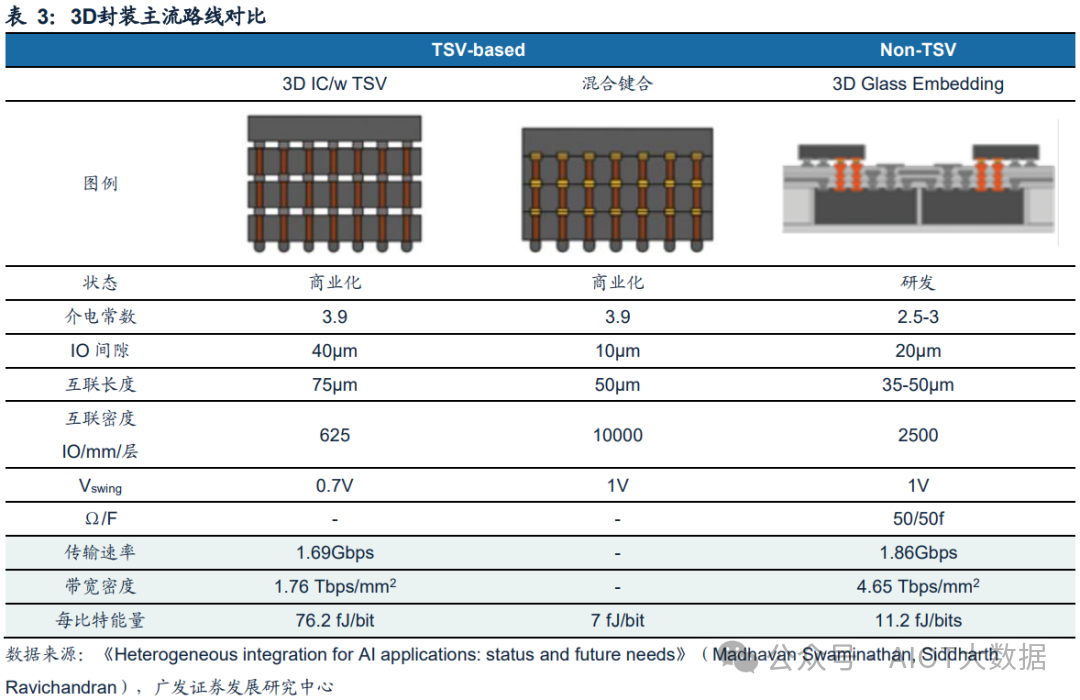

根據(jù)《Heterogeneous integration for AI applications: status and future needs》,可以看到玻璃中介層對比硅中介層,擁有更低的介電常數(shù)、更短的互聯(lián)長度和更高的傳輸速率(約提高3.5倍)以及帶寬密度(提高約3倍),同時能耗可以有效降低約2倍,玻璃中介層的優(yōu)勢較為明顯。

對于單面線路玻璃基板而言,產(chǎn)品的生產(chǎn)主要采用簡單的加成法就能完成。加法制造工藝采用導(dǎo)電金屬漿料直接在裸基材上印刷出電路圖形并高溫?zé)停牧侠寐矢撸a(chǎn)流程便捷、效率高,產(chǎn)品加工成本低、周期短。電路圖形是導(dǎo)電金屬漿料經(jīng)過高溫?zé)Y(jié)成型,剝離強(qiáng)度可達(dá)3N/mm以上,比傳統(tǒng)覆銅板更可靠。

加成法制作還解決了傳統(tǒng)PCB制程工藝中化學(xué)沉銅(或真空鍍膜)、黃光成像、電鍍銅、蝕刻銅等高成本、高能耗、重污染的問題,真正實現(xiàn)節(jié)能減排,綠色生產(chǎn)。

玻璃基板加法制造印刷電路的加工能力:

1.基板線路銅厚范圍:10~35μm;

2.基板厚度加工范圍:min 0.3mm;

3.基板有效加工尺寸:max 300*450mm [注:現(xiàn)有設(shè)備尺寸限制,可按需升級大尺寸];

4.印刷最小線路能力:量產(chǎn)100μm,打樣75μm。

玻璃基板加法制造電路銅的可靠性:

1.耐常規(guī)化學(xué)腐蝕,耐熱應(yīng)力,可焊性良好;

2.可正常進(jìn)行化學(xué)蝕刻、表面處理等再加工制程且穩(wěn)定可靠;

3.線路表面粗糙度低:Ra<0.5μm;

4.線路與基板附著力高:>3N/mm;

5.通過300℃熱沖擊測試,1000次熱循環(huán)后無失效,附著力依舊穩(wěn)定。

異構(gòu)集成的Chiplet 3D為嵌入式玻璃扇出(eGFO)封裝

對于異構(gòu)集成的Chiplet 3D封裝方面:玻璃基板TGV工藝可以在玻璃上制作空腔,進(jìn)而為芯片的封裝提供一種名為嵌入式玻璃扇出(eGFO)的新方案。根據(jù)《Heterogeneous integration for AI applications: status and future needs》,這種架構(gòu)不需要邏輯芯片中的TSV來建立較短的互連長度,因此可以提高信號完整性,減少昂貴芯片的占用空間,并降低整體系統(tǒng)成本。

該解決方案由多個嵌入式芯片和使用RDL連接的組裝芯片(玻璃制成)組成,目前這種封裝的IO間距可以做到20μm,L/S為2/2μm,并擁有三個金屬層,在傳輸效率、帶寬密度、能耗上均有明顯優(yōu)勢。

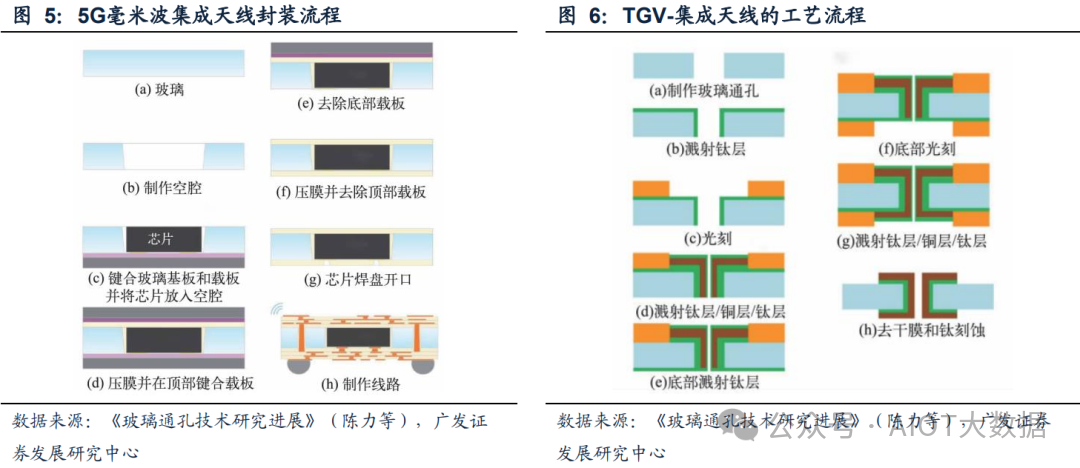

據(jù)《玻璃通孔技術(shù)研究進(jìn)展》(陳力等),2013年LEE等人利用玻璃通孔技術(shù)實現(xiàn)射頻MEMS器件的晶圓級封裝,采用電鍍方案實現(xiàn)通孔的完全填充,通過該方案制作的射頻MEMS器件在20 GHz時具有0.197 dB的低插入損耗和20.032 dB的高返回?fù)p耗,在40 GHz以內(nèi)具有穩(wěn)定的射頻性能;在5G毫米波集成天線封裝方面,2020年喬治亞理工的Tummala首次在100 μm的玻璃基板上實現(xiàn)了在n257頻段(26.5~29.5 GHz)的芯片嵌入毫米波天線集成模塊,該方案相比于倒裝芯片嵌入技術(shù)具有更低的信號損耗。

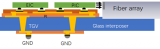

同樣的,使用TGV工藝制成的TGV-集成天線,可以應(yīng)用于3D系統(tǒng)封裝(SiP)中,能夠?qū)崿F(xiàn)更緊湊、高功率、高效的V波段(40~75 GHz)無線平面內(nèi)芯片到芯片(C2C)通信。

算力芯片領(lǐng)域,巨頭積極投入研發(fā)。目前人工智能對數(shù)據(jù)中心和傳輸效率提出了更高的要求,尤其是對低功耗、高帶寬的光模塊的需求更加迫切,而高算力Chiplet芯片離不開Cowos、FOEB等先進(jìn)封裝平臺。因此,隨著AI芯片尺寸/封裝基板越來越大,玻璃基封裝被各大公司提上日程,期望玻璃基板能夠構(gòu)建更高性能的多芯片系統(tǒng)級封裝(SiP)。

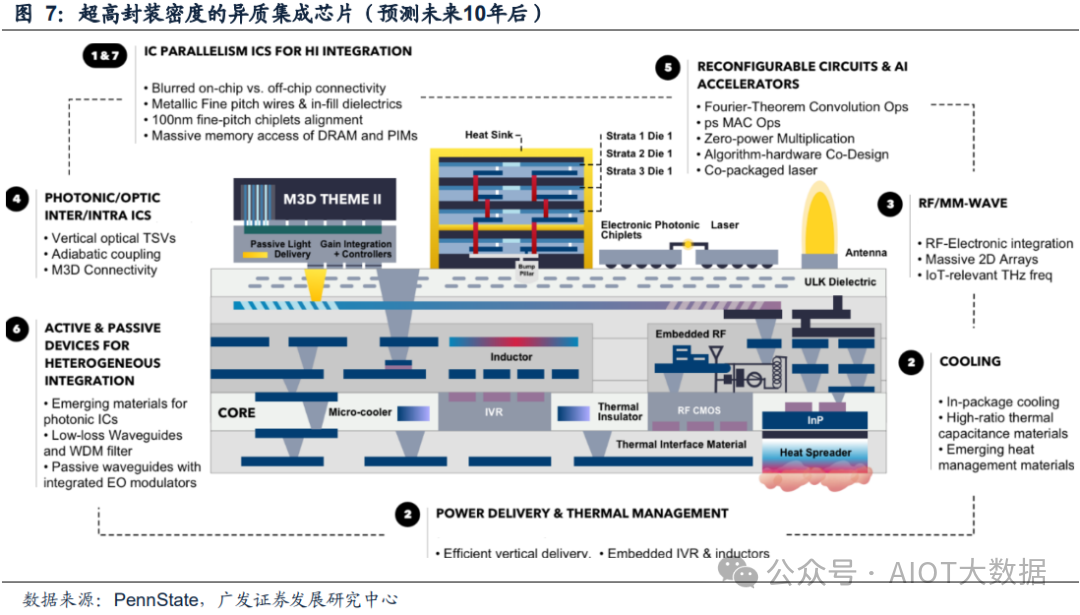

根據(jù)賓夕法尼亞大學(xué)的預(yù)測,未來隨著封裝工藝的演進(jìn)異質(zhì)集成將成為芯片發(fā)展的主流路徑,參考其給出的未來10年后的超高封裝密度集成芯片結(jié)構(gòu),可以看出如果需要將各模組都集成在同一芯片中,對組件小型化、基板材質(zhì)都提出了很高的要求。玻璃基板翹曲低、電學(xué)性能優(yōu)異的特點將使其成為下一代核心基板材料的不二之選,而玻璃通孔TGV工藝也將成為高效實現(xiàn)各模塊互聯(lián)的重要工藝。

目前三星、英特爾、谷歌、博通等,都有試作玻璃基板異構(gòu)3D封裝集成Chiplet芯片的產(chǎn)品,并在測試過程中,也證明了相關(guān)的電學(xué)性能和負(fù)載性能穩(wěn)定性,要比目前行業(yè)大批量量產(chǎn)的

而GB200在臺積電首批量產(chǎn)出現(xiàn)不穩(wěn)定現(xiàn)象時,行業(yè)與英偉達(dá)都深入討論過利用玻璃基板進(jìn)行封裝的可能性。隨后臺積電先后購買了兩座面板工廠來準(zhǔn)備玻璃基板封裝產(chǎn)能,也基本上確定是未來英偉達(dá)的GPU AI算力芯片,會采用新型的玻璃基板封裝。

嵌入式玻璃基板扇出(eGFO)封裝關(guān)鍵工藝——TGV和嵌入 (GPE)封裝

AI 應(yīng)用通常需要更大的中介層和非常高密度的互連以實現(xiàn)高帶寬。這些嚴(yán)格的要求加上可靠性和性能,要求開發(fā)和實施先進(jìn)的封裝技術(shù)來構(gòu)建大型封裝。

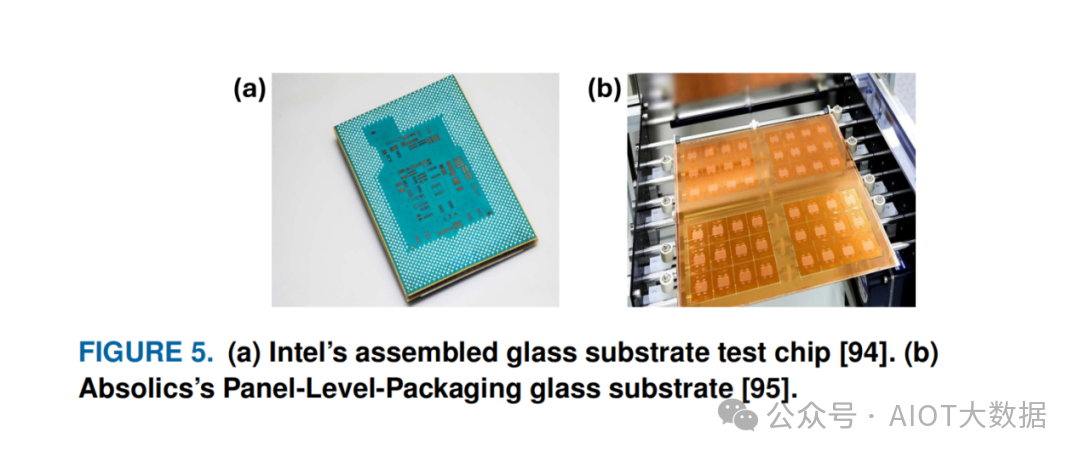

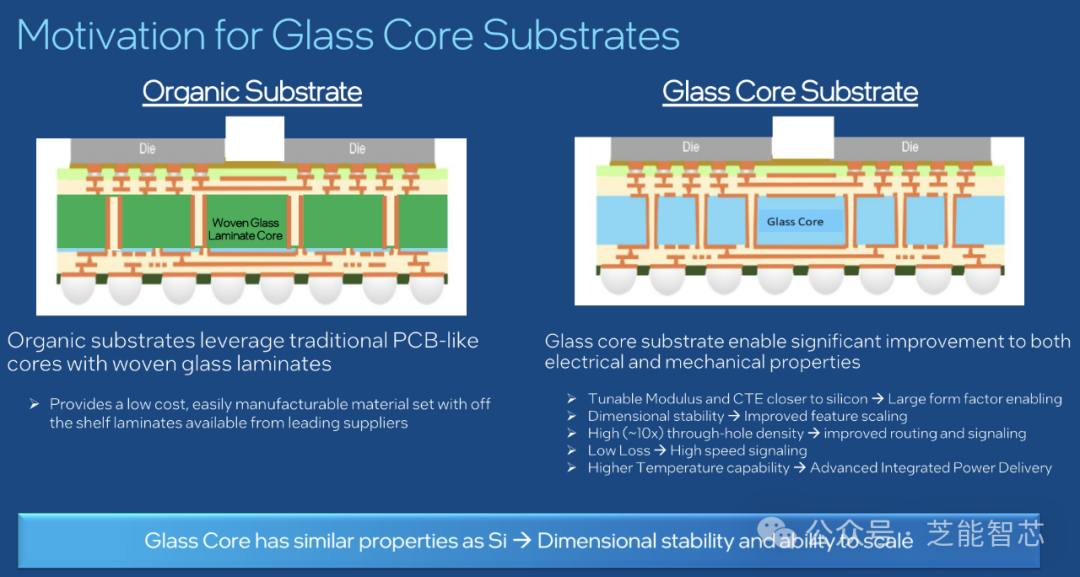

隨著對適用于 AI 和 HPC 應(yīng)用的更先進(jìn)封裝技術(shù)的需求,利用玻璃作為核心基板因其眾多優(yōu)勢而最近引起了極大關(guān)注 。英特爾最近展示了他們的第一款玻璃基板測試芯片,并宣布了他們朝著玻璃封裝發(fā)展的軌跡,以滿足對更強(qiáng)大計算的需求。(圖 5(a))韓國 SKC 的子公司 Absolics Inc. 也已開始準(zhǔn)備小批量制造(SVM)其玻璃基板(圖 5(b)),旨在以亞馬遜、Meta 和微軟等超大規(guī)模企業(yè)為潛在客戶。

Chiplet異構(gòu)3D集成玻璃芯封裝的優(yōu)勢

基于玻璃的中介層通過提高信號完整性、支持高密度互連、集成光通信、優(yōu)化熱管理以及確保可靠性和可擴(kuò)展性,增強(qiáng)了用于 AI 應(yīng)用的半導(dǎo)體封裝的帶寬能力。這些特性使玻璃中介層成為實現(xiàn)高性能計算和實現(xiàn)高級 AI 功能的重要組件。玻璃表面光滑/表面粗糙度極低,可以實現(xiàn)細(xì)線和空間的縮放,這對于實現(xiàn)非常高密度的互連至關(guān)重要。

此外,玻璃由 Si-O 鍵組成的表面結(jié)構(gòu)有助于粘附各種聚合物材料,用作介電樹脂和感光樹脂。將玻璃的低介電常數(shù)與多層中介層結(jié)構(gòu)的低介電常數(shù)累積層相結(jié)合,可以顯著降低系統(tǒng)的延遲。這一特性在最小化信號傳播延遲和減少相鄰互連之間的串?dāng)_方面起著至關(guān)重要的作用,尤其有利于高速電子設(shè)備和共封裝光學(xué)器件。

此外,玻璃基板降低了互連之間的電容,從而實現(xiàn)了更快的信號傳輸并提高了整體系統(tǒng)性能。在數(shù)據(jù)中心、電信和高性能計算等速度至關(guān)重要的關(guān)鍵應(yīng)用中,采用玻璃基板可以大大提高系統(tǒng)效率并增加數(shù)據(jù)吞吐量。

玻璃的低介電常數(shù)還支持卓越的阻抗控制,這對于保持整個電路的信號完整性至關(guān)重要。這一特性在射頻應(yīng)用中尤其有利,因為精確的阻抗匹配對于優(yōu)化功率傳輸和最大限度地減少信號損失至關(guān)重要。玻璃基板確保整個基板表面的電氣特性一致,從而能夠設(shè)計和生產(chǎn)具有更高可靠性和性能的高頻電路。

與有機(jī)封裝相比,玻璃具有出色的尺寸穩(wěn)定性,有助于提高層間精度,這是在多層玻璃中介層中實現(xiàn)非常高的互連密度的關(guān)鍵。這不僅有助于減小焊盤尺寸,還有助于將細(xì)線和走線縮小到<1μm,從而增加多層中介層中每個再分布層中的IO數(shù)量。此外,玻璃基板的熱膨脹系數(shù)(CTE)在3-12 ppm /℃范圍內(nèi)。這可以減輕玻璃與硅(CTE=3 ppm/℃)芯片以及玻璃與印刷線路板(CTE=17 ppm/℃)之間的 CTE 不匹配問題,能夠構(gòu)造玻璃是封裝和中介層應(yīng)用玻璃芯基板的另一個優(yōu)勢。

玻璃構(gòu)造可以是以下任何一種類型:(a) 玻璃通孔 (TGV:Through Glass Vias),(b) 盲玻璃腔 (BGC:Blind Glass Cavities),或 (c) 玻璃腔 (TGC:Through Glass Cavities)。

TGV 可以通過激光誘導(dǎo)深蝕刻 (LIDE:Laser Induced Deep Etching) 形成,首先對玻璃進(jìn)行局部激光修改,然后進(jìn)行濕化學(xué)蝕刻工藝,以最大限度地減少制造過程中微裂紋的積累。BGC 和 TGC 可以通過激光加工輕松形成,必要時可以進(jìn)行濕蝕刻工藝。

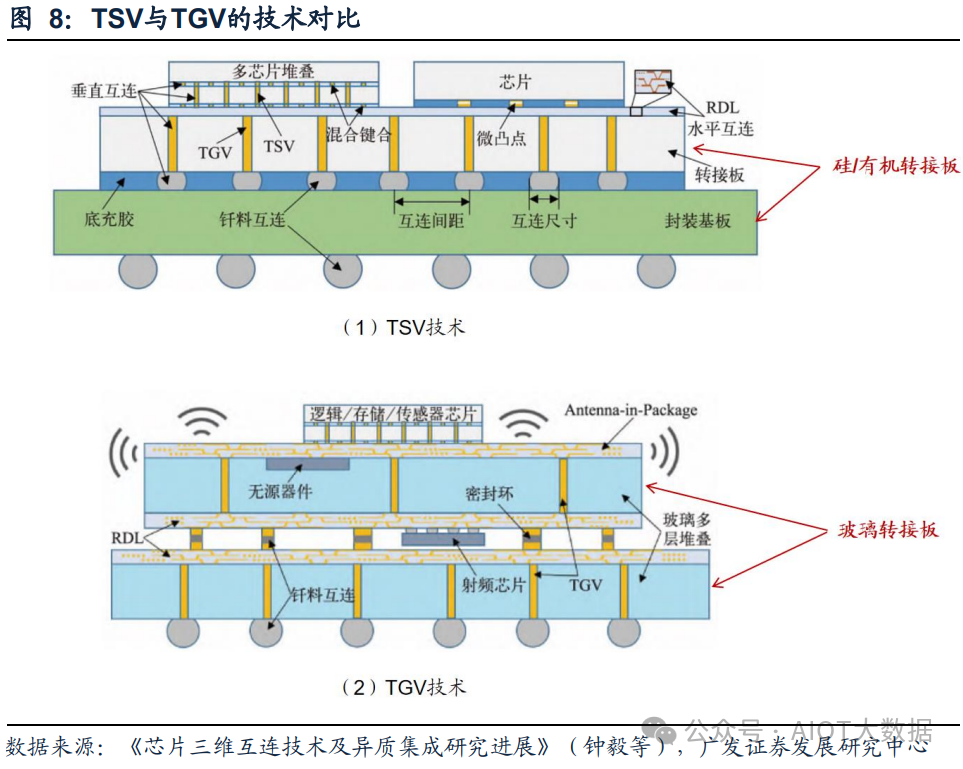

TGV技術(shù)是TSV技術(shù)的延續(xù),主要區(qū)別在于引入了基板種類的變化。

TSV(Through Silicon Via)是指通過在硅中介層打孔的方式實現(xiàn)實現(xiàn)垂直互聯(lián),而與之對應(yīng)的TGV(Through Glass Via,玻璃通孔)是指穿過玻璃基板的垂直電氣互連,它們都通過在中介層打孔并進(jìn)行電鍍填充來實現(xiàn)垂直方向的電氣互聯(lián),以此來降低信號傳輸?shù)木嚯x,增加帶寬和實現(xiàn)封裝的小型化。

而與TSV不同的是,TGV的中介層基板使用的是高品質(zhì)硼硅玻璃、石英玻璃,以此來取得比硅中介層更好的封裝表現(xiàn),被認(rèn)為是下一代三維集成的關(guān)鍵技術(shù)。

TGV作為TSV的低成本替代方案,逐漸受到廣泛關(guān)注。根據(jù)《玻璃通孔技術(shù)研究進(jìn)展》(陳力等),硅基轉(zhuǎn)接板2.5D/3D集成技術(shù)作為先進(jìn)系統(tǒng)集成技術(shù),近年來得到了迅猛的發(fā)展,但硅基轉(zhuǎn)接板存在兩個主要問題:

(1)成本高,硅通孔(TSV)的制作采用硅刻蝕工藝,隨后硅通孔需要氧化絕緣層、薄晶圓的拿持等技術(shù),步驟復(fù)雜且流程較長;

(2)電學(xué)性能差,硅材料屬于半導(dǎo)體材料,傳輸線在傳輸信號時,信號與襯底材料有較強(qiáng)的電磁耦合效應(yīng),襯底中產(chǎn)生渦流現(xiàn)象,造成信號完整性較差(插損、串?dāng)_等)。

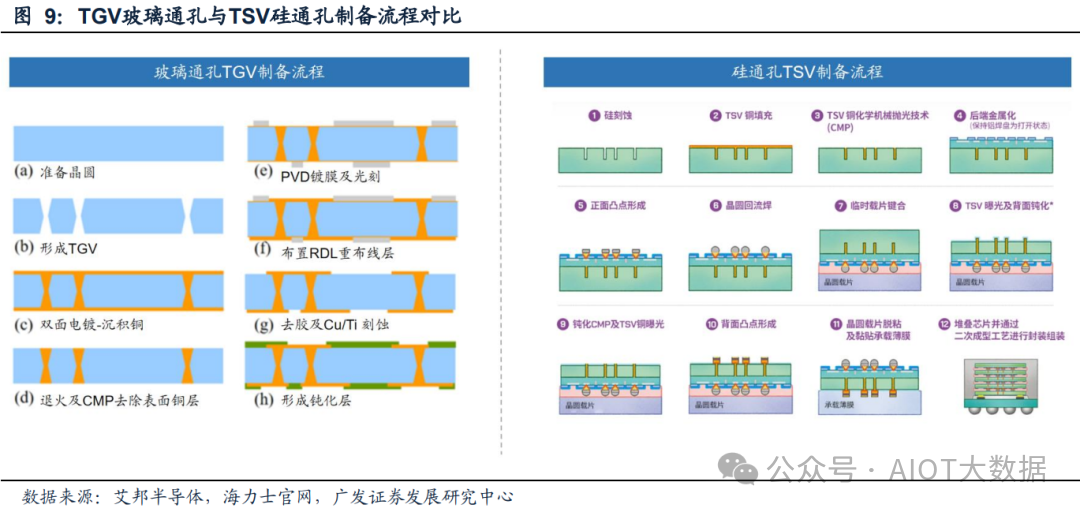

TGV省去了沉積隔離層、絕緣層的過程。TGV的制備流程包括,先玻璃基板上進(jìn)行打孔,然后采用電鍍的方法將Cu沉積在基板通孔和正反面已實現(xiàn)電氣連接,然后采用CMP的方法將表面Cu層去掉,最后采用PVD鍍膜光刻方法制備RDL重布線層,去膠后最終形成鈍化層。與TSV的制備流程對比,TGV省去了在襯底表面及TGV內(nèi)壁沉積絕緣層的步驟(由于銅可以與硅發(fā)生反應(yīng),因此需要沉積絕緣層、隔離層),并由于玻璃基板本身就可以做的很薄,還可以省去二次減薄的過程。

由于TSV技術(shù)目前相對比較成熟,已經(jīng)大規(guī)模應(yīng)用在高帶寬存儲器HBM的生產(chǎn)中,因此TGV與TSV相同的制備步驟(d)~(h)可以借鑒TSV的成功經(jīng)驗,技術(shù)成熟度相對比較高。根據(jù)《玻璃通孔三維互連鍍銅填充技術(shù)發(fā)展現(xiàn)狀》(紀(jì)執(zhí)敬等),目前TGV中介層面臨的挑戰(zhàn)主要集中在TGV的通孔成孔工藝以及TGV的高質(zhì)量填充兩方面。

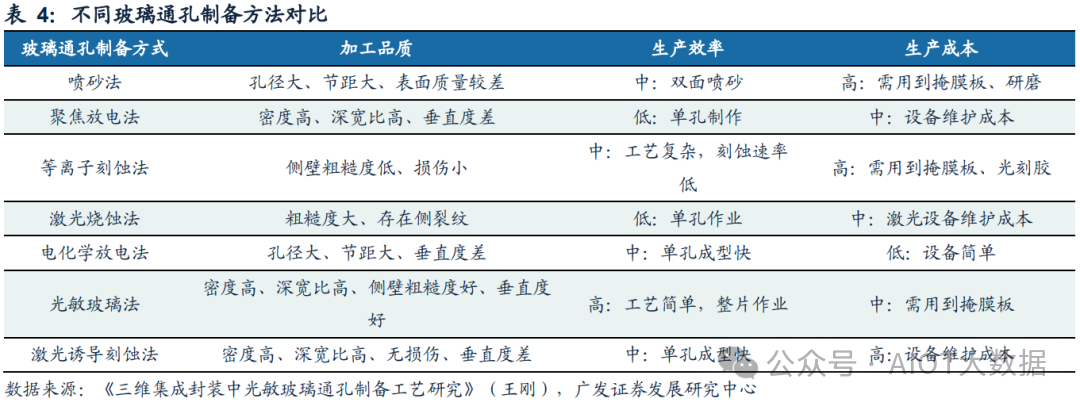

玻璃通孔成孔技術(shù):如何制作高精度的通孔/盲孔

玻璃通孔成孔技術(shù)是制約TGV發(fā)展的主要困難之一。TGV通孔的制備需要滿足高速、高精度、窄節(jié)距、側(cè)壁光滑、垂直度好以及低成本等一系列要求,如何制備出高深寬比、窄節(jié)距、高垂直度、高側(cè)壁粗糙度、低成本的玻璃微孔一直是多年來各種研究工作的重心。目前主流的玻璃通孔加工成型方法有噴砂法、聚焦放電法、等離子刻蝕法、激光燒蝕法、電化學(xué)放電法、光敏玻璃法、激光誘導(dǎo)刻蝕法等。

玻璃基板高密度布線

在完成玻璃通孔的制備后,需要在玻璃基板表面進(jìn)行布線來實現(xiàn)互聯(lián)互通的電氣連接,相對于有機(jī)襯底而言,玻璃表面的粗糙度小,所以在玻璃上可以進(jìn)行高密度的布線操作。但由于半加成工藝法在線寬小于5μm的時候會面臨許多挑戰(zhàn),例如在窄間距內(nèi)刻蝕種子層容易對銅走線造成損傷且窄間距里的種子層殘留易造成漏電,因此針對玻璃基板的表面高密度布線,學(xué)界和業(yè)界也有不同工藝路線的探索。

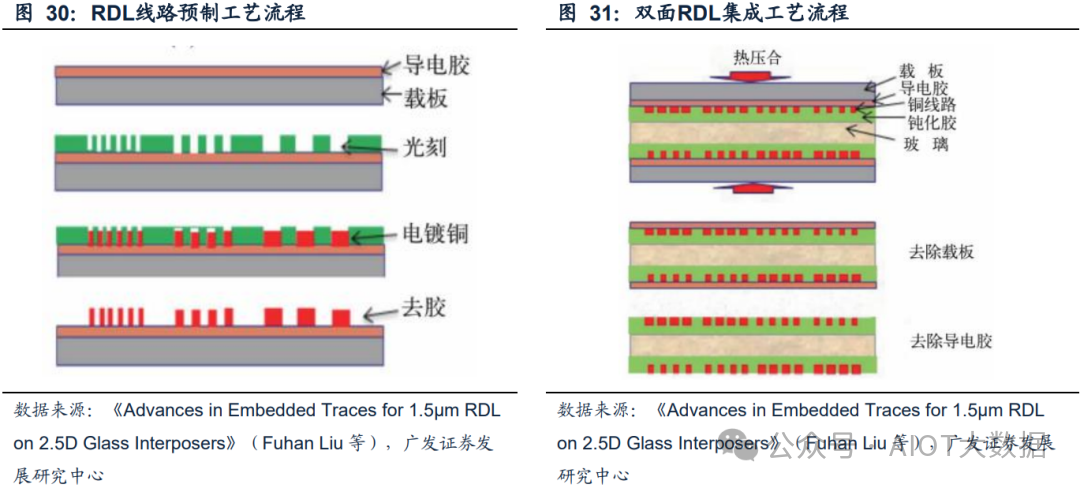

線路轉(zhuǎn)移(CTT)和光敏介質(zhì)嵌入(PTE)

針對在玻璃表面直接進(jìn)行窄距布線會造成缺陷的問題,劉富漢等人研究開發(fā)了線路轉(zhuǎn)移(CTT)和光敏介質(zhì)嵌入(PTE)。根據(jù)《Advances in Embedded Traces for 1.5μm RDL on 2.5D Glass Interposers》,CTT(Copper Trace Transfer,線路轉(zhuǎn)移)主要包括兩個過程:

1. 預(yù)制RDL線路:首先在可移動載體上單獨制造一層薄導(dǎo)電層,通過光刻、電鍍和去膠制作出RDL線路,并在轉(zhuǎn)移到基板上之前測試或檢查細(xì)線成品率。

2. RDL層集成:完成RDL層的制備后,先在玻璃中介層的兩面利用鈍化膠形成鈍化層,隨后使用熱壓合的方式將預(yù)制RDL層轉(zhuǎn)移到鈍化層上,最后去除載板和導(dǎo)電膠。

PTE(Photo Trench Embedding,光敏介質(zhì)嵌入)的詳細(xì)工藝流程包括:

1. 首先刻蝕基板下側(cè)銅箔,并使用真空壓膜機(jī)在基板上側(cè)壓合感光膜;

2. 隨后在光刻圖案化后進(jìn)行種子層沉積,采用物理氣相沉積(PVD)分別沉積Ti和Cu作為阻擋層和種子層,接著采用電鍍工藝填充溝槽;

3. 溝槽填充完后,使用化學(xué)腐蝕劑刻蝕掉上表面的銅從而露出線路。

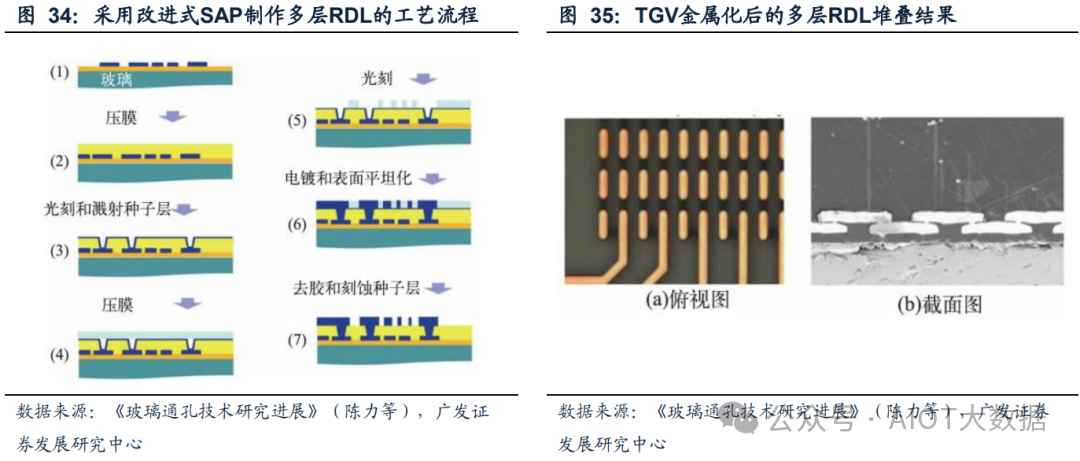

多層RDL的2.5D玻璃轉(zhuǎn)接板技術(shù)

在多層RDL制備領(lǐng)域,喬治亞理工學(xué)院的LU等研究了多層RDL的2.5D玻璃轉(zhuǎn)接板技術(shù),實現(xiàn)了面板級光刻后1.5~5 μm的線條溝槽制備,并提出改進(jìn)式半加成工藝法(SAP)達(dá)到了5 μm以下低成本的線寬制作工藝,即用旋轉(zhuǎn)金剛刀取代昂貴的CMP對層間RDL表面平坦化,進(jìn)而做到低成本多層RDL堆疊。

其工藝步驟包括:

1. 在第一層RDL上進(jìn)行壓膜;

2. 通過光刻和濺射制作通孔并暴露出第一層 RDL的銅焊盤,然后進(jìn)行種子層濺射;

3. 隨后將高分辨率的光刻薄膜層壓在基板,進(jìn)行曝光顯影來顯露第二層的RDL圖案;

4. 隨后采用電鍍工藝填充通孔形成RDL線路,并用旋轉(zhuǎn)金剛刀進(jìn)行表面平坦化,去除光刻薄膜并完成種子層刻蝕。

玻璃基板嵌入 (GPE)

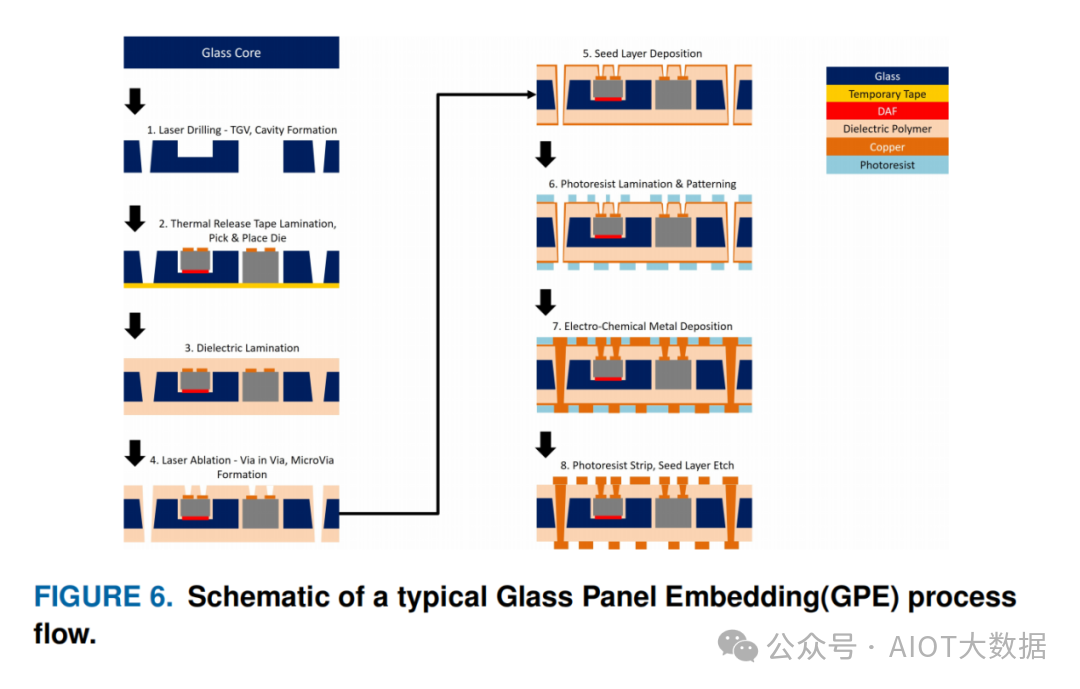

BGC 和 TGC 對于將芯片嵌入 BGC 和 TGC 非常重要,這被稱為玻璃面板嵌入 (GPE)。制造所需尺寸的腔體,并使用精度為幾微米的自動芯片拾取和放置工具將芯片放入這些腔體中。

GPE 工藝非常適合異構(gòu)集成,其中不同尺寸和功能的芯片(包括電容器和磁電感器等無源元件)內(nèi)置在封裝中。在這種方法中,電容器和電感器保持在靠近電力輸送/IVR 等應(yīng)用所需的位置。

GPE 中使用的典型工藝流程

利用先進(jìn)的 GPE 工藝,可以輕松地將熱解決方案集成到封裝中以消除熱量。例如,對于帶有 TGC 的 GPE,可以將隔熱材料和散熱器附著到玻璃基板的背面。對于 BGC,可以在減薄/研磨基板后加入散熱器來消除熱量。GPE 架構(gòu)可以輕松地從 2.5D 架構(gòu)調(diào)整為包括 3D 集成,其中可以使用以下方法之一:

(a)例如,可以將邏輯芯片與玻璃芯頂部和底部的 RDL 一起嵌入玻璃腔中,然后在頂部組裝存儲器芯片以生成具有短互連距離和小得多的外形尺寸的 3D 結(jié)構(gòu),從而顯著降低封裝的高度;

(b)無源芯片可以嵌入結(jié)構(gòu)化玻璃中,并且可以通過倒裝芯片工藝在玻璃封裝結(jié)構(gòu)上組裝多個芯片 ;

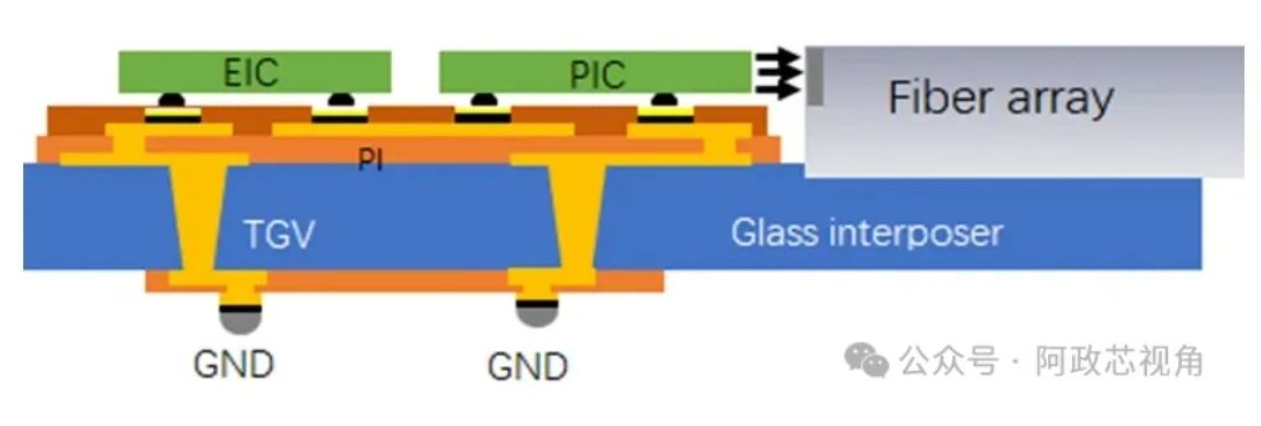

(c) 此外,GPE 實現(xiàn)了共封裝光學(xué)器件等先進(jìn)封裝概念,其中可以將電子芯片嵌入玻璃腔體(芯片背面采用上述散熱解決方案),并在封裝頂部組裝光子芯片 (PIC)。通過將 PIC 安裝在頂部,可以輕松地從頂部安裝光纖耦合器以及任何所需的散熱解決方案。

最后,除了各種優(yōu)越的性能外,玻璃對封裝中基板格式的限制更少。雖然硅只能在圓形晶圓中加工,但玻璃可以實現(xiàn)面板工藝,從而降低成本。例如,300 毫米晶圓可容納 2,500 個 6 毫米 x 6 毫米尺寸的封裝,而 600 毫米 x 600 毫米面板可容納 12,000 個封裝。

目前玻璃的限制

玻璃基板固有的易碎性帶來了重大挑戰(zhàn),尤其是當(dāng)行業(yè)采用更薄的基板來滿足對更高設(shè)備集成度和性能的需求時。薄玻璃板有時薄至 100μm 或更薄,在處理和制造過程中特別容易損壞。這種在壓力下開裂或破碎的風(fēng)險凸顯了專門設(shè)備和定制工藝的必要性,這些工藝旨在安全地處理這種材料。

除了處理困難之外,玻璃還表現(xiàn)出相對較低的散熱性。盡管玻璃比有機(jī)層壓板導(dǎo)熱性更好,但與硅相比,玻璃的導(dǎo)熱性較差。為了克服與玻璃導(dǎo)熱性低相關(guān)的限制,已經(jīng)證明了將銅結(jié)構(gòu)(例如通孔封裝通孔 (TPV)、銅塊和重分布層 (RDL) 中的銅跡線)結(jié)合到玻璃基板中的方法 [107]。此外,用于嵌入式和基于基板的封裝的下一代熱界面材料 (TIM) 也正在積極開發(fā)中,重點是降低熱界面電阻,以實現(xiàn)芯片的最大熱傳遞。

-

嵌入式

+關(guān)注

關(guān)注

5093文章

19178瀏覽量

307708 -

封裝

+關(guān)注

關(guān)注

127文章

7997瀏覽量

143413 -

基板

+關(guān)注

關(guān)注

2文章

287瀏覽量

23100

原文標(biāo)題:技術(shù)前沿:玻璃基板嵌入技術(shù)(GPE) 和玻璃基板扇出(eGFO)封裝

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

迎接玻璃基板時代:TGV技術(shù)引領(lǐng)下一代先進(jìn)封裝發(fā)展

一文解讀玻璃基板與陶瓷基板、PCB基板的優(yōu)缺點及適用領(lǐng)域

玻璃基板、柔性基板和陶瓷基板的優(yōu)劣勢

玻璃基板:半導(dǎo)體封裝領(lǐng)域的“黑馬”選手

AMD獲得玻璃核心基板技術(shù)專利

玻璃基板的四大關(guān)鍵技術(shù)挑戰(zhàn)

玻璃基板的技術(shù)優(yōu)勢有哪些

熱門的玻璃基板,相比有機(jī)基板,怎么切?

探尋玻璃基板在半導(dǎo)體封裝中的獨特魅力

英特爾是如何實現(xiàn)玻璃基板的?

康寧計劃擴(kuò)大半導(dǎo)體玻璃基板市占 擬推出芯片封裝用玻璃芯

玻璃基板時代,TGV技術(shù)引領(lǐng)基板封裝

玻璃基板:封裝材料的革新之路

技術(shù)前沿探索:玻璃基板嵌入技術(shù)(GPE)與玻璃基板扇出封裝(eGFO)

技術(shù)前沿探索:玻璃基板嵌入技術(shù)(GPE)與玻璃基板扇出封裝(eGFO)

評論