雷達數據采集及圖像顯示是雷達的一個基本應用,普遍應用于軍事、氣象預測、環境監測、船舶導航等領域。雷達數據具有實時性、高速性的特點。一般說來,對雷達信號采樣的時鐘頻率在100MHz以上,雷達數據采集和處理單元的數據吞吐量要求在Gbits/s以上。因此,要實現一個雷達數據采集和圖像顯示系統,對處理器的處理速度要求很高。傳統的雷達數據采集和圖像顯示系統采用的是微處理器+FPGA(或DSP)方案,利用微處理器實現操作系統、雷達GUI和顯示器控制,利用FPGA(或DSP)實現高速雷達數據采集和處理,這種方案的缺點是要想實現雷達圖像在800*600以上分辨率的大屏幕顯示比較困難,要么有較高的處理器速度,要么有獨立顯卡的支持,這樣增加了系統復雜度和成本。

SOPC 是一種特殊的片上系統,建立在可編程邏輯技術的基礎上,盡可能將一個大而完整的電子系統實現在一塊FPGA硅片上,具有硬件可裁剪、可擴充、可升級,軟件在系統可編程的特點,使得設計的系統在規模、功能、體積、性能、上市周期、開發成本等方面有著了很大的優勢。基于SOPC技術的軟核處理器主頻雖然不是很高,目前Xilinx公司的microblaze處理器最高主頻為210MHz、240DMIPS的運算能力,Altera公司的NIOS II處理器最高主頻為340MHz、290DMIPS的運算能力,但是由于其極強的靈活性,可以通過軟硬件協同設計,在處理器速度不高的情況下,解決需要高速度處理器才能完成的問題。

本文基于SOPC技術,提出一種在主頻較低的軟核處理器上實現雷達數據采集和圖像大屏幕顯示的方法。

2總體方案設計

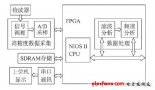

本設計采用microblaze軟核處理器作為開發平臺,SOPC系統框圖如圖1所示。

圖1 系統硬件結構框圖

本設計通過以下辦法,解決在主頻較低的SOPC軟核處理器上實現雷達數據采集、處理和大屏幕圖像顯示的問題。

首先,使用FPGA硬件邏輯設計實現雷達數據采集、處理和顯示控制器。雷達數據采集、處理模塊負責對雷達上單元、ADC芯片的控制和對雷達數據的處理。顯示控制器模塊完成顯存數據的管理和顯示器的驅動。

其次,使用DMA傳輸。DMA負責將雷達數據采集、處理后數據通過DMA通道送到內存中。

最后,根據SOPC硬件可配置、可裁剪的特性,將雷達數據采集和處理模塊、顯示控制模塊和DMA模塊作為microblaze處理器的設備掛載到外設局部總線上[4]。

由于雷達數采集、處理模塊和顯示控制模塊的內部邏輯都由FPGA硬件邏輯完成,微處理器不需直接對雷達上單元、ADC進行控制,不需進行復雜的雷達數據處理,不用對顯存數據進行管理,不用控制產生高速的信號驅動顯示器,從而大大減輕了處理器的負擔,加上DMA傳輸的使用,處理器只需要處理DMA傳輸的請求和傳輸完成中斷,從而使處理器從繁重的數據傳輸中解脫了出來。通過以上辦法,處理器的負擔已經變得很輕,使得較低的處理器速度即可處理系統的任務。而且顯示控制由FPGA硬件實現還有個優點是,使得顯示器分辨率的大小對處理器的負擔影響很小,從而在處理器較低的情況下,同樣可以支持大屏幕的圖像顯示。

-

sopc

+關注

關注

2文章

248瀏覽量

62337 -

數據采集

+關注

關注

39文章

6251瀏覽量

114037

發布評論請先 登錄

相關推薦

LCoS顯示技術的大屏幕HDTV介紹

SoPC技術在圖像采集和處理系統中的應用設計

一種基于SOPC和USB2.0接口的高速數據采集系統及虛擬儀器設計

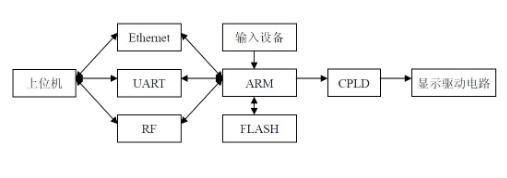

如何設計大屏幕顯示器控制系統?

FPGA+DSP的紅外圖像數據采集與顯示

SOPC基礎上的數據采集系統設計

基于SOPC的數據采集與處理系統設計

基于LED顯示技術的會展用大屏幕的設計與實現

LED大屏幕顯示屏控制系統的總體設計框架圖解析

基于SOPC技術實現雷達數據采集和圖像大屏幕顯示

基于SOPC技術實現雷達數據采集和圖像大屏幕顯示

評論