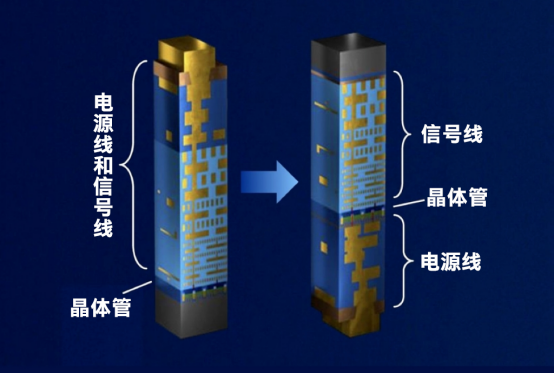

IBM 與日本芯片制造商 Rapidus 在 2024 IEEE IEDM 國際電子器件會議上,對外展示了雙方攜手合作所研發的多閾值電壓 GAA 晶體管技術成果。該技術上的重大突破預計會被應用于 Rapidus 的 2nm 制程生產流程之中。

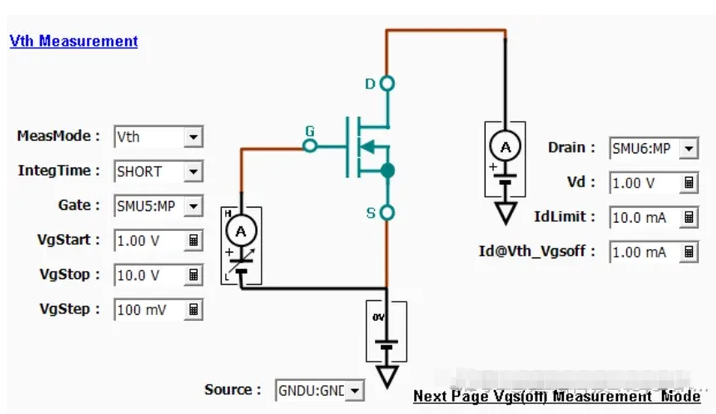

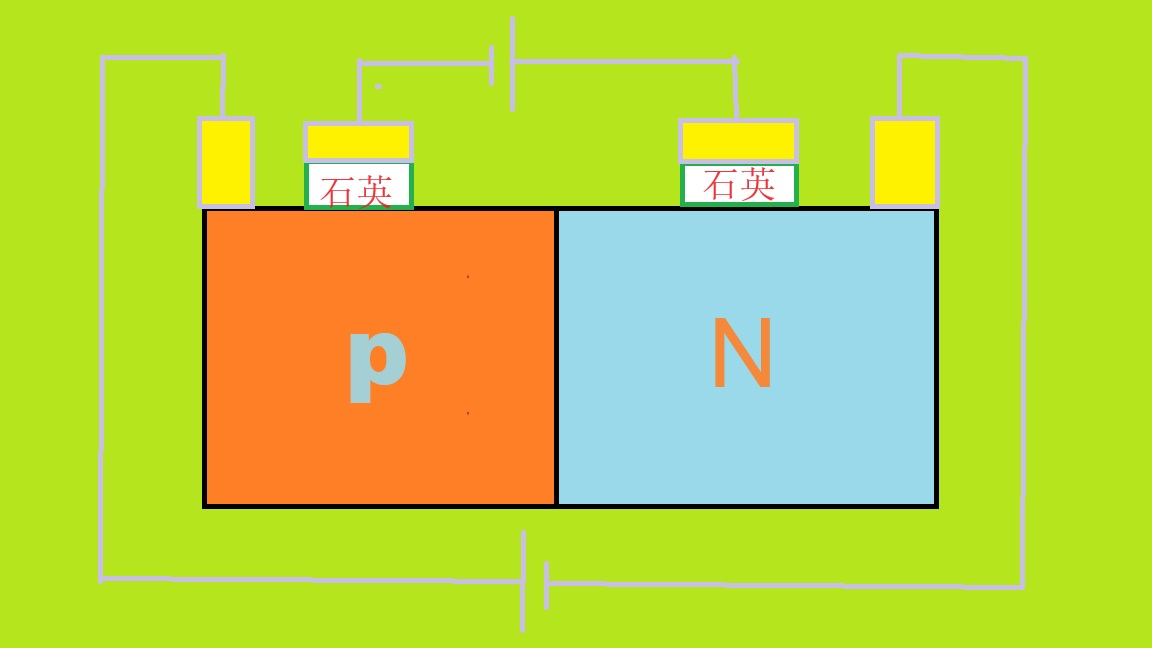

IBM 宣稱,當制程推進到 2nm 階段時,晶體管的結構會從長久以來所采用的 FinFET(鰭式場效應晶體管)轉換為 GAAFET(全環繞柵極場效應晶體管)。這一轉變為制程的迭代更新引發了新的難題:怎樣達成多閾值電壓,從而讓芯片能夠在較低的電壓環境下執行復雜的運算任務。

鑒于在 2nm 名義制程之下,N 型與 P 型半導體通道彼此間的距離極為狹小,所以需要精準的光刻技術才能夠在實現多閾值電壓的同時,又不對半導體的性能造成較大的負面影響。不過,IBM 與 Rapidus 引入了兩種存在差異的選擇性減少層(SLR)芯片構建工藝手段,順利達成了預期的目標效果。

IBM 研究院高級技術人員 Bao Ruqiang 表示:與上一代 FinFET 相比,Nanosheet 納米片的構造差異顯著,并且可能更具復雜性。我們所提出的新生產流程相較于之前使用的方法更為簡便,我們堅信這會使我們的合作伙伴 Rapidus 能夠更輕松、更可靠地運用 2 納米片技術進行大規模的芯片制造工作。

-

IBM

+關注

關注

3文章

1765瀏覽量

74860 -

晶體管

+關注

關注

77文章

9745瀏覽量

138896 -

Rapidus

+關注

關注

0文章

41瀏覽量

60

發布評論請先 登錄

相關推薦

意法半導體推出全新40V MOSFET晶體管

英特爾IEDM 2024大曬封裝、晶體管、互連等領域技術突破

EEPROM存儲器的工作原理 EEPROM與FLASH存儲器的比較

MOS管的閾值電壓是什么

二極管閾值電壓和導通電壓的區別

NMOS晶體管和PMOS晶體管的區別

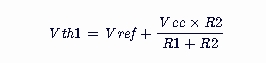

滯回比較器的閾值電壓如何確定?

MOSFET閾值電壓是什么?影響MOSFET閾值電壓的因素有哪些?

IBM與Rapidus在多閾值電壓GAA晶體管技術的新突破

IBM與Rapidus在多閾值電壓GAA晶體管技術的新突破

評論