測(cè)量對(duì)于確定 IC 的 EMC 特性是必要的。只有準(zhǔn)確了解 IC 的 EMC 特性,才能在生產(chǎn)前采取有效的預(yù)防措施,提高產(chǎn)品的抗 ESD 能力和 EMC 性能,避免后期因 ESD 干擾導(dǎo)致的產(chǎn)品故障和成本增加等問(wèn)題

集成電路ESD 測(cè)試與分析

1、測(cè)試環(huán)境與電場(chǎng)產(chǎn)生

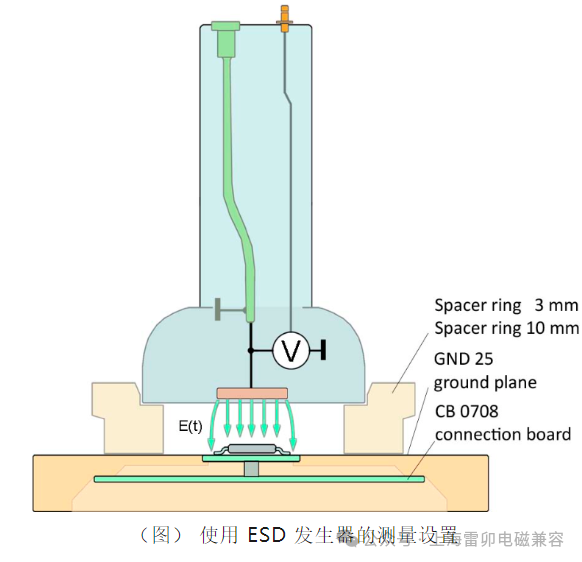

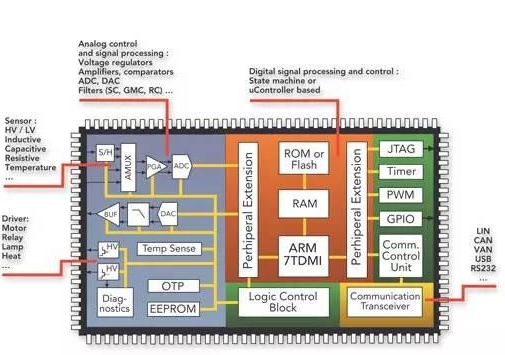

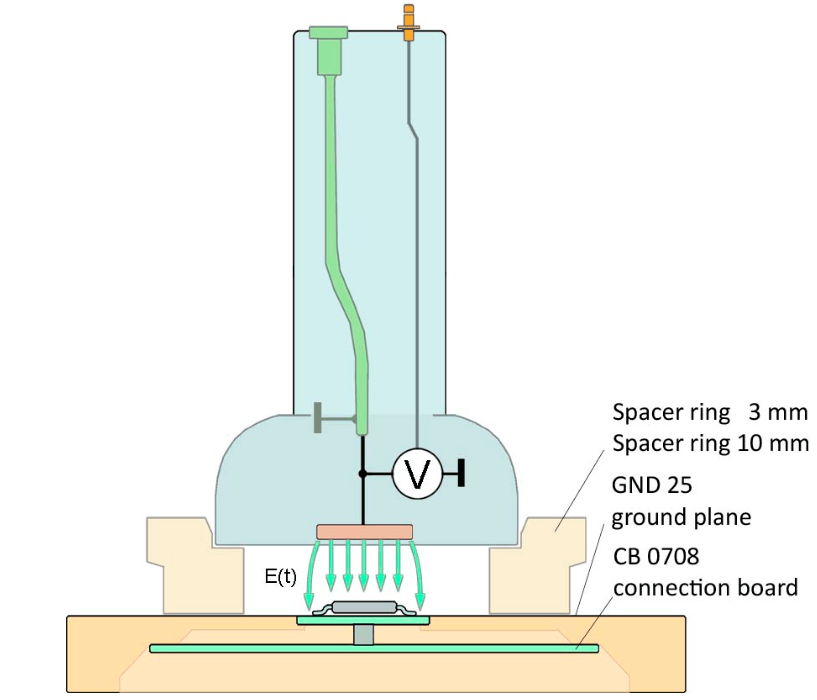

測(cè)試環(huán)境,集成電路(IC)被放置在一個(gè)由接地平面、隔離墊圈環(huán)和場(chǎng)源形成的屏蔽空間內(nèi)。接地平面:可起到接地保護(hù)和屏蔽電磁干擾的作用;隔離墊圈:用于確定場(chǎng)源與IC之間的距離;場(chǎng)源:則是產(chǎn)生電場(chǎng)的關(guān)鍵部件;通過(guò)隔離墊圈,場(chǎng)源被設(shè)置在集成電路上方特定高度處。場(chǎng)源包含一個(gè)電極,測(cè)試電壓脈沖會(huì)被施加到該電極上,電極進(jìn)而產(chǎn)生一個(gè)確定的電場(chǎng),集成電路就處于這個(gè)電場(chǎng)之中。這種設(shè)置能夠?yàn)榧呻娐诽峁┮粋€(gè)可控制且相對(duì)穩(wěn)定的電場(chǎng)環(huán)境,以便進(jìn)行相關(guān)測(cè)試.

場(chǎng)源可以產(chǎn)生多種在實(shí)際中可能出現(xiàn)的測(cè)試脈沖。例如,在實(shí)際使用中,脈沖的上升時(shí)間可能會(huì)出現(xiàn) 200 皮秒、1 納秒和 5 納秒等不同情況,這使得測(cè)試能夠更貼近真實(shí)的工作場(chǎng)景,更準(zhǔn)確地評(píng)估集成電路在各種實(shí)際電場(chǎng)條件下的性能。

測(cè)試過(guò)程中,電極電壓會(huì)逐漸增加,直至達(dá)到集成電路的抗擾度水平。通過(guò)這種方式,可以確定集成電路在不同電場(chǎng)強(qiáng)度下的耐受能力,為評(píng)估其可靠性和穩(wěn)定性提供重要依據(jù)。

2、靜電放電事件中的磁場(chǎng)影響

在靜電放電(ESD)事件期間,結(jié)構(gòu)部件可能會(huì)產(chǎn)生額外的磁場(chǎng). 例如,當(dāng)ESD發(fā)生時(shí),放電電流會(huì)在結(jié)構(gòu)部件周圍形成磁場(chǎng),這些磁場(chǎng)可能會(huì)與集成電路(IC)相互作用,從而干擾IC的正常運(yùn)行。

利用相同的測(cè)量設(shè)置和一個(gè)磁場(chǎng)源確定IC的磁場(chǎng)抗擾度水平,這種方法能夠在相對(duì)統(tǒng)一的條件下,對(duì) IC 抵抗磁場(chǎng)干擾的能力進(jìn)行量化評(píng)估,以便更好地了解 IC 在不同磁場(chǎng)強(qiáng)度和頻率下的性能表現(xiàn)。

故障模式分析:在進(jìn)行上述測(cè)量時(shí),需要對(duì)集成電路的故障模式進(jìn)行分析。在不同測(cè)試條件下出現(xiàn)的故障情況,如邏輯錯(cuò)誤、輸出異常、死機(jī)等,可以深入了解其在電場(chǎng)和磁場(chǎng)干擾下的薄弱環(huán)節(jié),為改進(jìn)設(shè)計(jì)和提高可靠性提供有價(jià)值的信息。

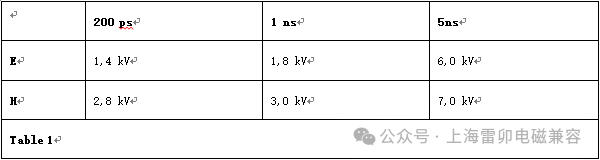

下表列出了針對(duì)一個(gè)微控制器的靜電放電抗擾度測(cè)量結(jié)果,通常情況下,干擾脈沖上升時(shí)間越短,其頻譜越寬,對(duì) IC 的干擾能力可能越強(qiáng)。表 1 中的數(shù)據(jù)可以幫助工程師更直觀地了解微控制器在不同 ESD 脈沖上升時(shí)間下的抗擾度性能,進(jìn)而為系統(tǒng)級(jí)的 ESD 防護(hù)設(shè)計(jì)提供依據(jù)。

測(cè)量裝置確定 EMC 參數(shù),這些參數(shù)對(duì)于評(píng)估 IC 在電磁環(huán)境中的性能和兼容性至關(guān)重要,包括抗擾度、發(fā)射水平等指標(biāo)。

3、關(guān)于集成電路受外部電磁場(chǎng)干擾的問(wèn)題

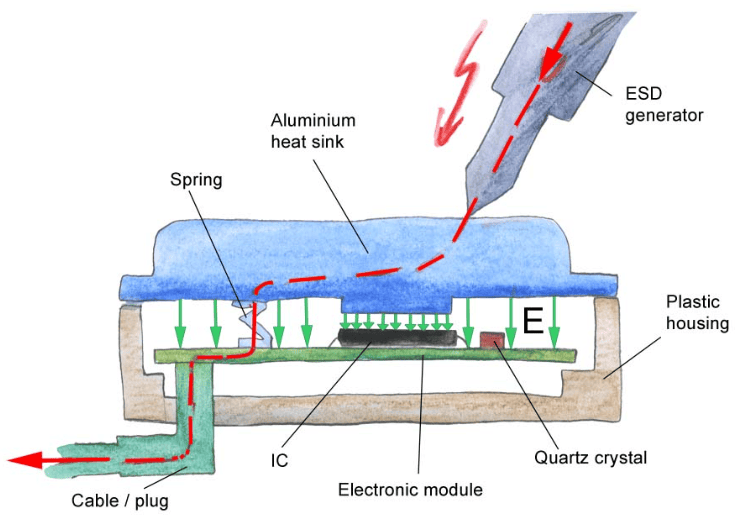

如果電場(chǎng)或磁場(chǎng)從外部干擾集成電路,改變布局作為對(duì)策是不合適的。在這種情況下,唯一有用的補(bǔ)救措施是改變機(jī)械設(shè)計(jì)。

屏蔽作用:通過(guò)改變機(jī)械設(shè)計(jì),可以為 IC 增加有效的電磁屏蔽措施。例如,使用金屬外殼或屏蔽罩將 IC 包裹起來(lái),這樣可以阻擋外部電磁場(chǎng)的進(jìn)入,從而保護(hù) IC 免受干擾。

距離和方向調(diào)整:合理地調(diào)整 IC 與外部電磁場(chǎng)源之間的距離和相對(duì)方向,也屬于機(jī)械設(shè)計(jì)的范疇。增加距離可以降低電磁場(chǎng)的強(qiáng)度,而改變相對(duì)方向則可能使 IC 處于電磁場(chǎng)較弱的區(qū)域。如大型變壓器周圍的電磁場(chǎng)分布不均勻,通過(guò)調(diào)整 IC 的位置和方向,使其遠(yuǎn)離強(qiáng)磁場(chǎng)區(qū)域或與磁場(chǎng)方向平行,可以減少磁場(chǎng)對(duì)其的影響。

4、針對(duì)散熱器強(qiáng)電場(chǎng)的具體應(yīng)對(duì)措施

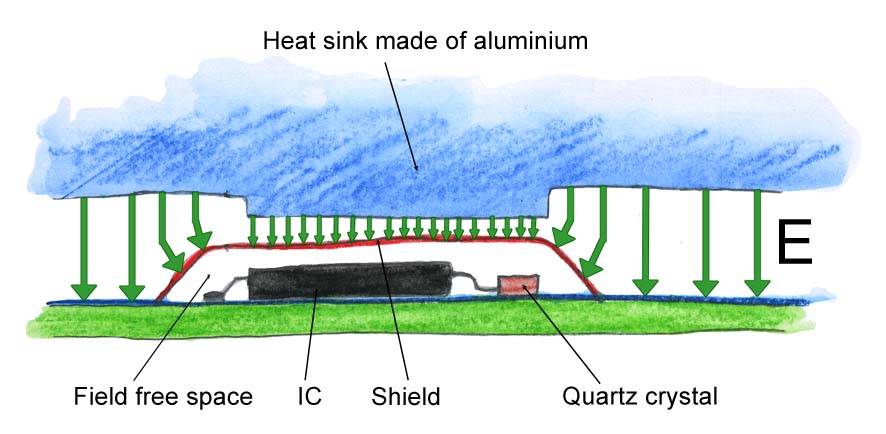

對(duì)于上圖中的具體示例,可以采取以下對(duì)策,其中 IC 上方的散熱器會(huì)產(chǎn)生強(qiáng)電場(chǎng):

1、增加電子模塊和散熱器之間的接觸彈簧數(shù)量,可以改善兩者之間的熱傳導(dǎo)。

2、在集成電路(IC)上方布置局部屏蔽罩,如圖所示。這主要是為了減少外部電磁場(chǎng)對(duì) IC 的干擾,保護(hù)其內(nèi)部的敏感信號(hào)和電路。如果可能的話,用屏蔽罩將模塊全方位封閉起來(lái),并可能配備穿心濾波器。這樣做可以提供更全面的電磁屏蔽效果,防止外部電磁場(chǎng)進(jìn)入模塊內(nèi)部,同時(shí)也能阻止模塊內(nèi)部產(chǎn)生的電磁輻射泄漏到外部。

3、將 IC 移動(dòng)到無(wú)電磁場(chǎng)的一側(cè),但這樣做會(huì)導(dǎo)致冷卻無(wú)法進(jìn)行。這是一種在電磁兼容性和散熱之間進(jìn)行權(quán)衡的措施。當(dāng) IC 受到電磁場(chǎng)干擾問(wèn)題較為嚴(yán)重,且其他電磁屏蔽措施難以實(shí)施或效果不佳時(shí),可以考慮將其移動(dòng)到遠(yuǎn)離電磁場(chǎng)源的位置。需要注意的是,該位置可能不利于散熱,因此需要綜合考慮 IC 的工作溫度范圍、散熱要求以及電磁環(huán)境等因素。

4、增加 IC 和散熱器之間的間隙:這樣做可能會(huì)對(duì)散熱產(chǎn)生一定的影響,但在某些情況下,如需要避免兩者之間的電氣耦合或機(jī)械干涉時(shí),是一種可行的方法。然而,這可能會(huì)導(dǎo)致散熱效率下降,因此需要根據(jù)具體情況進(jìn)行評(píng)估和優(yōu)化,例如通過(guò)增加其他散熱措施來(lái)彌補(bǔ)間隙增大帶來(lái)的散熱損失。

綜上,可以說(shuō),就開(kāi)發(fā)抗干擾組件的時(shí)間和成本節(jié)約而言,提前了解微控制器的 ESD 參數(shù)是非常有益的。這意味著必須測(cè)量微控制器的 ESD 參數(shù)。該信息將允許在組件開(kāi)發(fā)期間盡早規(guī)劃必要的對(duì)策,以確保整個(gè)組件具有抗干擾性。

-

集成電路

+關(guān)注

關(guān)注

5388文章

11563瀏覽量

362098 -

ESD

+關(guān)注

關(guān)注

49文章

2037瀏覽量

173091 -

測(cè)試

+關(guān)注

關(guān)注

8文章

5318瀏覽量

126730 -

電磁兼容性

+關(guān)注

關(guān)注

6文章

425瀏覽量

33714

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

集成電路的電磁兼容測(cè)試概述

電磁兼容性分析的方法

混合集成電路EMC設(shè)計(jì)產(chǎn)生的原因闡述

混合集成電路電磁干擾產(chǎn)生的原因是什么

集成電路電磁兼容性標(biāo)準(zhǔn)與測(cè)試

混合集成電路的電磁兼容設(shè)計(jì)

混合集成電路的電磁兼容設(shè)計(jì)思路

集成電路電磁兼容性設(shè)計(jì)應(yīng)遵循的原則和方法

汽車設(shè)計(jì)中的電磁兼容性和集成電路IC問(wèn)題解決方案

如何設(shè)計(jì)混合集成電路的電磁兼容

TEM小室法應(yīng)用在集成電路制造的電磁兼容測(cè)試

集成電路電磁兼容性及應(yīng)對(duì)措施相關(guān)分析(一) — 電子系統(tǒng)性能要求與ESD問(wèn)題

集成電路電磁兼容性及應(yīng)對(duì)措施相關(guān)分析(二)—集成電路ESD問(wèn)題應(yīng)對(duì)措施

集成電路電磁兼容性及應(yīng)對(duì)措施相關(guān)分析(三)—集成電路ESD 測(cè)試與分析

集成電路電磁兼容性及應(yīng)對(duì)措施相關(guān)分析(一) 電子系統(tǒng)性能要求與ESD問(wèn)題

集成電路電磁兼容性及應(yīng)對(duì)措施相關(guān)分析(三)集成電路ESD 測(cè)試與分析

集成電路電磁兼容性及應(yīng)對(duì)措施相關(guān)分析(三)集成電路ESD 測(cè)試與分析

評(píng)論