作者:Art Pini

投稿人:DigiKey 北美編輯

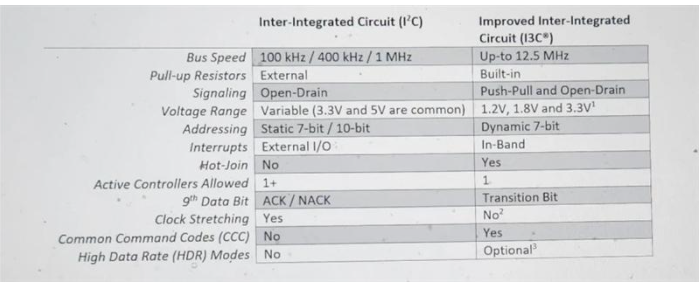

用于集成電路 (IC) 間通信的板載串行接口由內(nèi)部集成電路 (I2C) 和串行外設(shè)接口 (SPI) 主導(dǎo),兩者自 20 世紀 80 年代起就已問世。這些接口廣泛用于將低速傳感器和 IC 連接到微控制器單元 (MCU),以實現(xiàn)板內(nèi)短距離通信。然而,隨著數(shù)字系統(tǒng)的速度越來越快,這些接口已成為限制因素,I2C 的典型數(shù)據(jù)速率僅為 1 Mbit/s,而 SPI 也不過 10 Mbit/s。其他限制因素,包括專用中斷或芯片使能線路,需要額外的信號連接,這就增加了線數(shù)以及總線連接的復(fù)雜性。

改進型內(nèi)部集成電路 (I3C) 總線旨在對 IC 間通信進行升級。該總線具有更高的數(shù)據(jù)速率、更大的靈活性,以及真正的雙線接口,支持帶內(nèi)中斷 (IBI) 而非外部中斷。

本文討論了 I3C 接口的特征,以及為什么說它是 I2C 和 SPI 串行接口的理想升級品。我們將使用典型的 MCU、IC 開關(guān)和傳感器設(shè)備來展示其應(yīng)用。

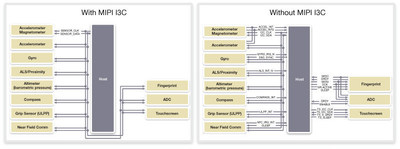

嵌入式通信總線

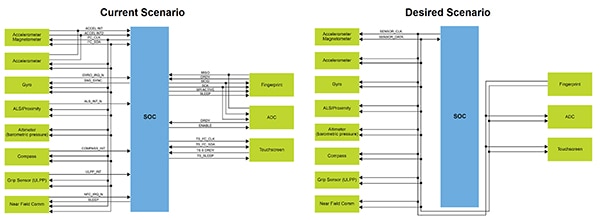

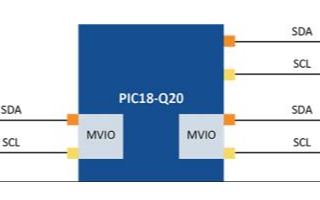

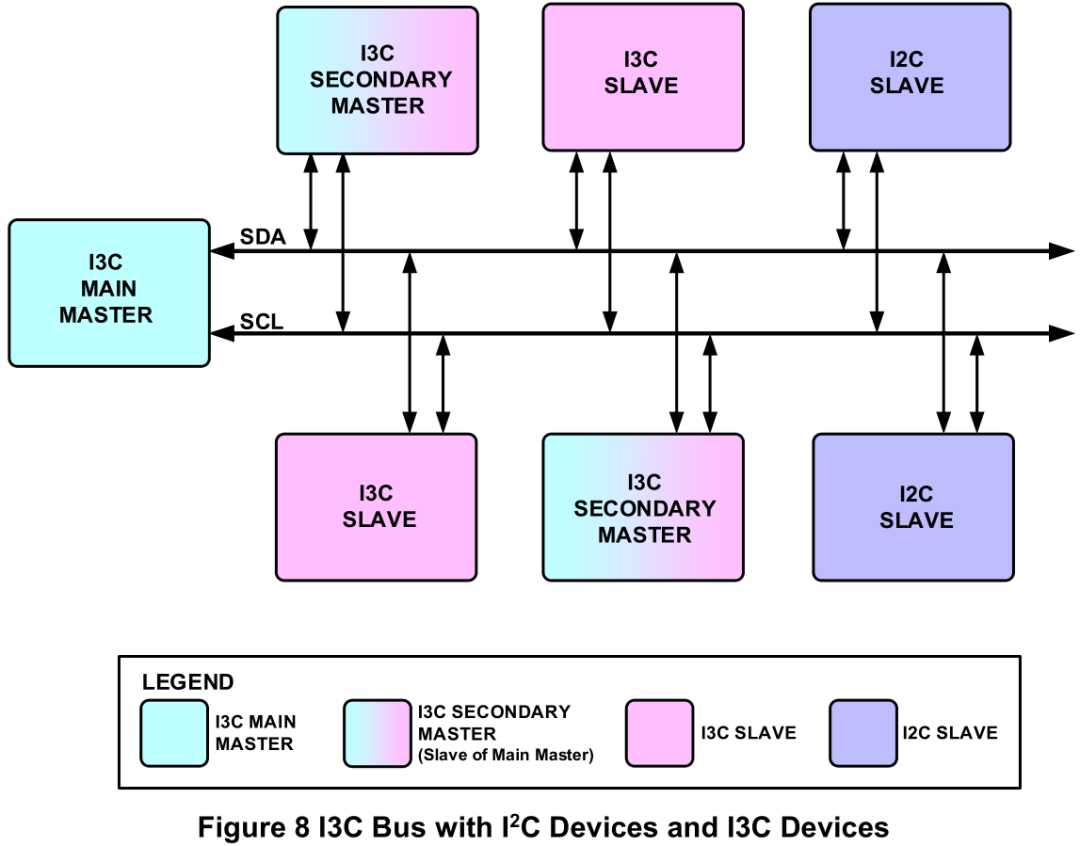

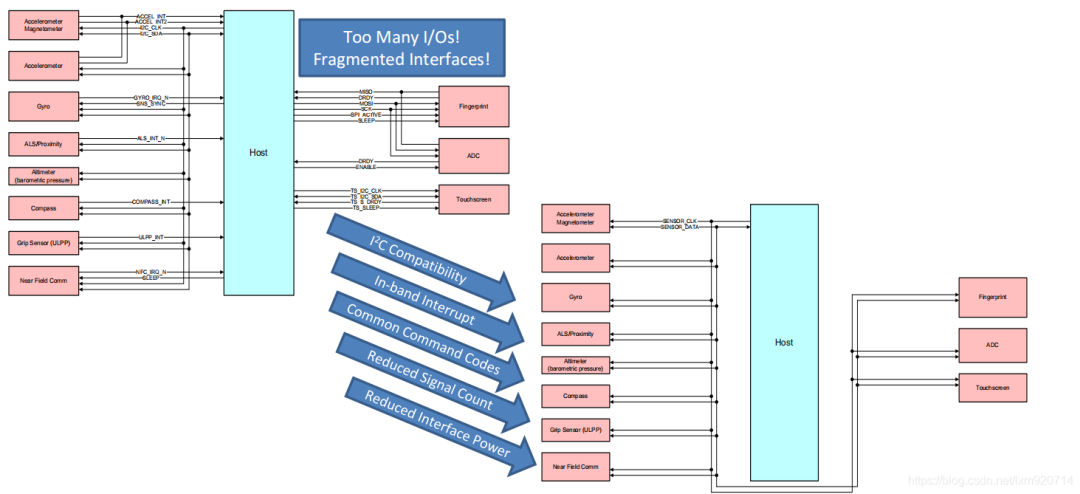

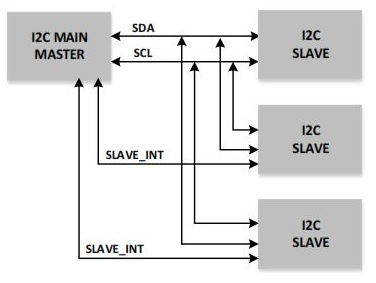

多年來,I2C 和 SPI 等嵌入式串行互連器件一直被用于板內(nèi)通信。這些器件主要用作傳感器和用戶界面設(shè)備及其控制處理器之間的通信總線。典型系統(tǒng)中的傳感器數(shù)量不斷增加,在手機中已達到 10 到 20 個,在汽車中則更多。與此同時,隨著對更高速度、更低功耗和更少導(dǎo)線的需求不斷上升,對設(shè)計人員而言,通信要求也變得更具挑戰(zhàn)性。設(shè)計人員必須滿足這些要求,同時通過中斷和使能線保持處理器控制(圖 1)。

圖 1:嵌入式通信應(yīng)支持更高速度、更低功耗和最少線數(shù)。(圖片來源:[NXP Semiconductors])

圖 1:嵌入式通信應(yīng)支持更高速度、更低功耗和最少線數(shù)。(圖片來源:[NXP Semiconductors])

現(xiàn)行技術(shù)使用兩線制 I2C 或四線制 SPI 接口實現(xiàn)傳感器和用戶控制設(shè)備接口。中斷、使能和其他控制線路與時鐘和數(shù)據(jù)線路分開,因此每個接口有更多線路。

設(shè)計人員需要一種更具前瞻性的接口方法,這種方法可以消除互連器件中的這些額外導(dǎo)線,僅使用時鐘和數(shù)據(jù)線路在帶內(nèi)處理這些操作。此外,總線應(yīng)具有更高的運行速度,以及更低的功率損耗。

I3C 接口

為了滿足這些要求,移動行業(yè)處理器接口 (MIPI) 聯(lián)盟開發(fā)了 I3C。該接口面向 MIPI 會員提供 MIPI I3C,面向非會員提供功能簡化版 MIPI I3C Basic。與傳統(tǒng)的 I2C 和 SPI 接口一樣,這種改進型也是串行接口,采用兩線制,盡可能減少了引腳數(shù)以及元器件之間的信號路徑數(shù)量。其數(shù)據(jù)速率高達 12.5 Mbits/s,采用單倍數(shù)據(jù)速率 (SDR) 模式,時鐘頻率為 12.5 MHz。該接口運行功率水平較低,采用簡單而靈活的設(shè)計架構(gòu)。

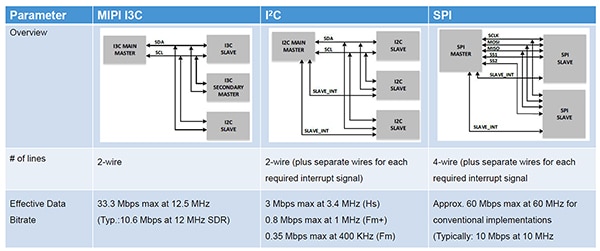

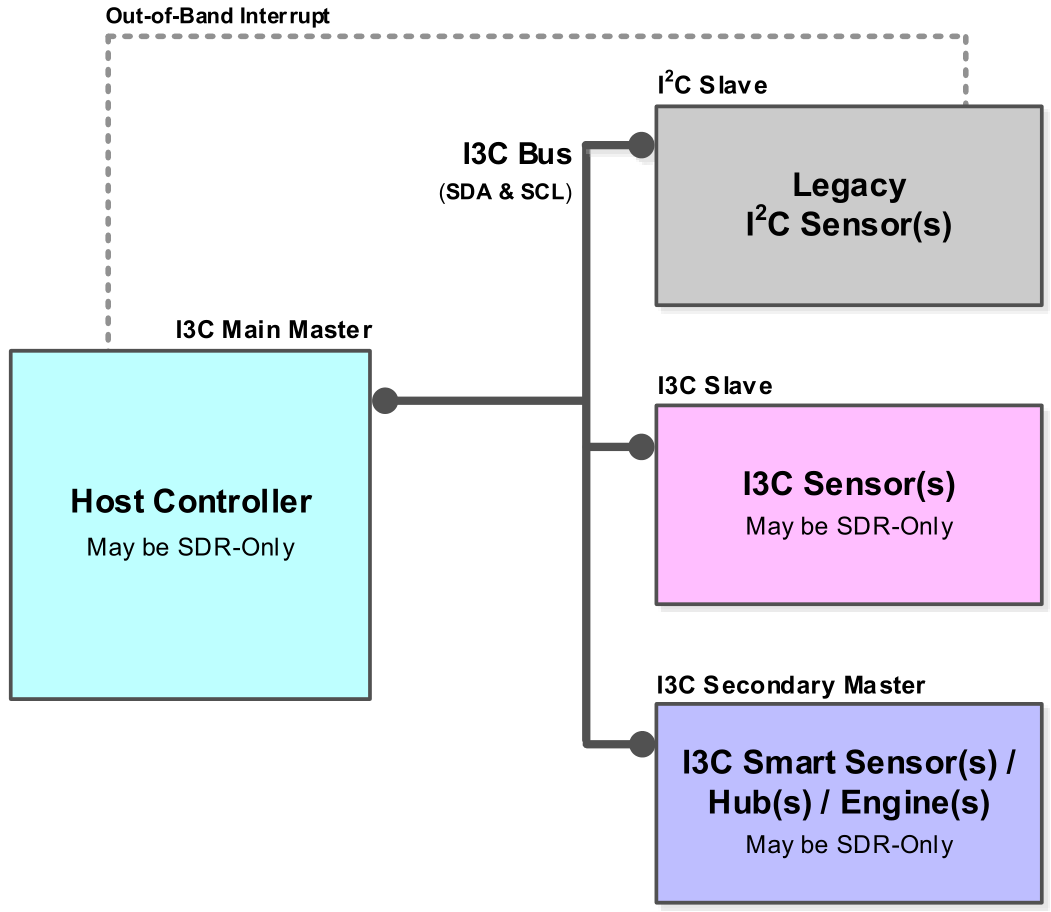

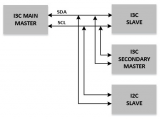

值得注意的是,I3C 標準保留了與 I2C 系統(tǒng)有限的向后兼容性,可讓現(xiàn)有 I2C 設(shè)備連接到 I3C 總線,同時仍允許總線在符合 I3C 標準的設(shè)備之間進行通信時切換到更高的數(shù)據(jù)速率。系統(tǒng)配置的比較見圖 2。

圖 2:通過對 I3C、I2C 和 SPI 接口的基本配置進行比較,可以看出 I3C 的速度更快,布線更簡單。(圖片來源:NXP Semiconductors)

圖 2:通過對 I3C、I2C 和 SPI 接口的基本配置進行比較,可以看出 I3C 的速度更快,布線更簡單。(圖片來源:NXP Semiconductors)

四線制 SPI 接口運行速度更快,并支持全雙工通信。I2C 通過由時鐘 (SCL) 和數(shù)據(jù) (SDA) 線路組成的雙線制總線進行半雙工通信。兩者都需要額外的線路來支持中斷和其他控制功能(如片選)。I3C 將接口中使用的線數(shù)減少至兩條,消除了 I2C 和 SPI 中單獨使用的中斷、使能和片選線路。對于需要 10 到 20 個傳感器與處理器相連且每個傳感器都有數(shù)條輔助線的系統(tǒng)來說,減少線數(shù)是一大優(yōu)勢。中斷和其他控制線路被 IBI 取代。在這種方法中,目標傳感器或設(shè)備會將其地址輸入 I3C 總線地址標頭,以通知處理器發(fā)生中斷。

I2C 和 I3C 的時鐘速率相差甚大。I2C 的時鐘速率一般為 100 kHz、400 kHz 或 1 MHz,而 I3C 的時鐘速率可達 12.5 MHz。以前,SPI 用于時鐘速率高于 1 MHz 的應(yīng)用。設(shè)計時需要在時鐘速率與線數(shù)之間進行選擇。I3C 采用真正的雙線制拓撲結(jié)構(gòu),具有更高的時鐘和數(shù)據(jù)速率,從而改變了這一現(xiàn)狀。

推挽輸出的開關(guān)速度比開漏或集電極驅(qū)動器更快,是 I3C 提高時鐘速率的重要因素。為了保持與 I2C 設(shè)備的兼容性,I3C 可根據(jù)總線狀態(tài)在開漏和推挽驅(qū)動器之間切換。開漏或集電極設(shè)計在初始尋址或仲裁期間使用,此時線路上可同時存在 I2C 和 I3C 設(shè)備。在進行單向通信時,I3C 采用推挽方式,不會出現(xiàn) I2C 設(shè)備同時通信的情況。

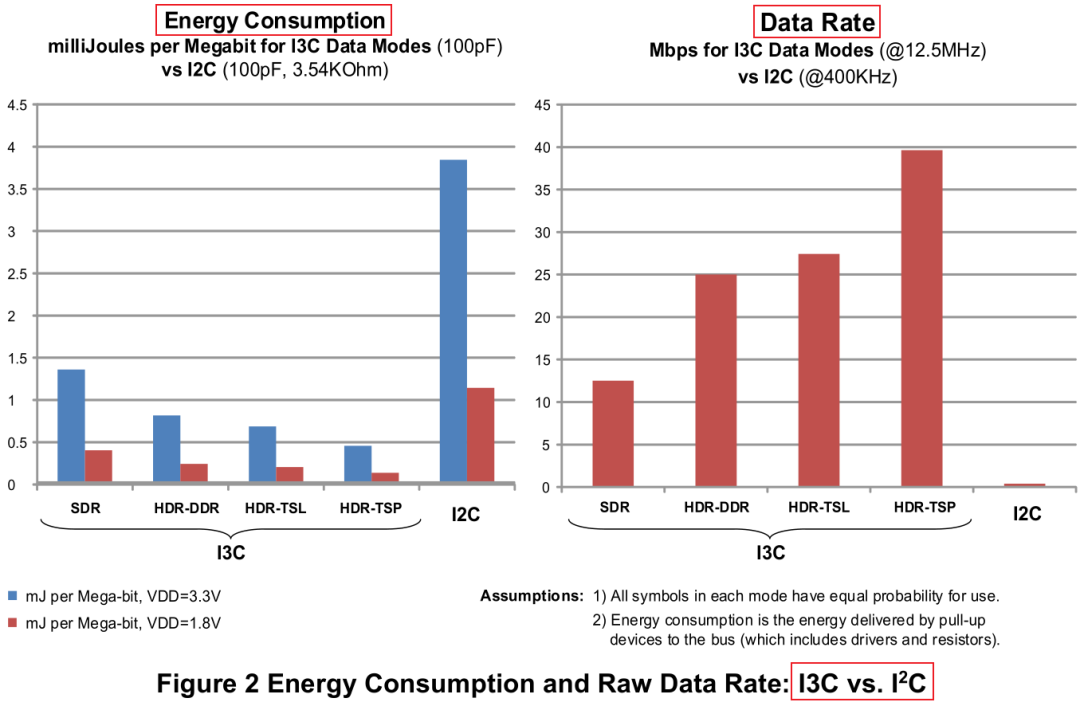

除標準 SDR 外,I3C 還支持多種可選的高數(shù)據(jù)速率 (HDR) 模式。這些 HDR 模式以相同的時鐘速率運行,但傳輸?shù)臄?shù)據(jù)密度更高。第一種 HDR 模式是 HDR 雙倍數(shù)據(jù)速率 (HDR-DDR),數(shù)據(jù)在時鐘信號的兩個邊沿進行傳輸,速率是原來的近兩倍。對于 12.5 MHz 時鐘,DDR 模式可實現(xiàn) 20 Mbits/s 的有效數(shù)據(jù)速率。

HDR 三元符號有兩個版本:HDR 純總線三元符號 (HDR-TSP) 僅適用于 I3C 設(shè)備,而 HDR 傳統(tǒng)三元符號 (HDR-TSL) 則適用于包括 I2C 和 I3C 器件在內(nèi)的總線。三元符號模式通過在 SCL 和 SDA 線路上編碼三位(三元)符號來實現(xiàn)每個時鐘三個數(shù)據(jù)位。

HDR 批量傳輸 (HDR-BT) 模式支持通過四路、雙路或單路 SDA 數(shù)據(jù)線路進行通信,從而提供最高數(shù)據(jù)速率。因此,在相同的時鐘速率下,這是原始單倍數(shù)據(jù)速率性能的 8 倍、4 倍或 2 倍。

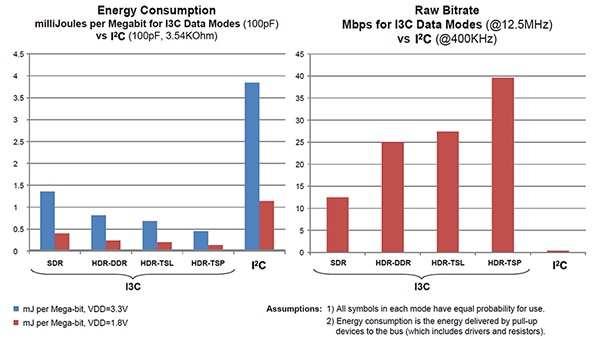

數(shù)據(jù)傳輸速度的提高使設(shè)備的啟動時間更短,從而降低了總線功率占空比。這與 I2C 相比降低了功耗(圖 3)。從帶有外部上拉電阻器的開集驅(qū)動器轉(zhuǎn)變?yōu)橥仆祢?qū)動器進一步降低了功耗,因為上拉電阻器需要很大的功率才能運行。

圖 3:與 I2C 相比,I3C 在數(shù)據(jù)速率和功耗方面均有改進。(圖片來源:NXP Semiconductors)

圖 3:與 I2C 相比,I3C 在數(shù)據(jù)速率和功耗方面均有改進。(圖片來源:NXP Semiconductors)

尋址

I2C 對每個總線設(shè)備使用 7 位或 10 位長度的靜態(tài)地址。這在 I3C 中已更改為 7 位動態(tài)尋址,即總線主設(shè)備在動態(tài)地址分配 (DAA) 時設(shè)置設(shè)備地址,并將其存儲在設(shè)備寄存器中。在 I3C 中仍可像在 I2C 外設(shè)中一樣使用靜態(tài)尋址。

由于采用動態(tài)尋址,設(shè)備地址可在以后更改。這支持熱連接,允許在總線運行時添加新設(shè)備。連接到 I3C 總線的新設(shè)備通過發(fā)送熱連接請求向 I3C 主設(shè)備發(fā)出其存在的信號。主控制器確認請求并分配一個地址,以將設(shè)備添加到總線上。

IBI

I3C 是真正的雙線制總線,使用 IBI 而不是 I2C 那樣的專用中斷線路。IBI 是指目標設(shè)備通過拉低 SDA 線路向主設(shè)備發(fā)出可用性信號的情況。然后,主設(shè)備會啟動 SCL 線路上的時鐘,目標設(shè)備將其地址傳輸?shù)?I3C 總線上,以通知控制器發(fā)生中斷。

常用命令代碼

常用命令代碼 (CCC) 是標準化命令,控制器可將其作為一般廣播同時發(fā)送給所有 I3C 設(shè)備或特定目標設(shè)備。這些命令用于與總線管理有關(guān)的項目。CCC 協(xié)議的格式以 I3C 廣播地址開始,總線上的所有 I3C 設(shè)備都能識別該地址。總線上的任何 I2C 設(shè)備都不會確認該請求,因為這是一個保留的 I2C 地址。

每條命令都包括一個 8 位描述符 ID 字段,后面還可能有一個命令有效載荷。向特定設(shè)備發(fā)送的命令會在有效載荷的第一個字節(jié)中傳遞設(shè)備地址。有四十多個 CCC 命令,包括:

- 輸入動態(tài)地址分配 (ENTDAA)

- 設(shè)置新動態(tài)地址分配 (SETNEWDA)

- 啟用事件 (ENEC)/禁用事件 (DISEC)

- 復(fù)位動態(tài)地址分配 (RSTDAA)

- 輸入高數(shù)據(jù)速率模式 (ENTHDRx)

- 獲取設(shè)備特征寄存器 (GETDCR)

供應(yīng)商可以使用一系列專用的 CCC ID 來執(zhí)行自己的命令。

錯誤檢測和恢復(fù)

與 I2C 不同,I3C 包含錯誤檢測和恢復(fù)功能。對于目標設(shè)備,有六種強制性錯誤和恢復(fù)方法,還有一種可選方法。此外,還有專門針對主設(shè)備端錯誤的其他錯誤和恢復(fù)方法。

支持 I3C 的元器件

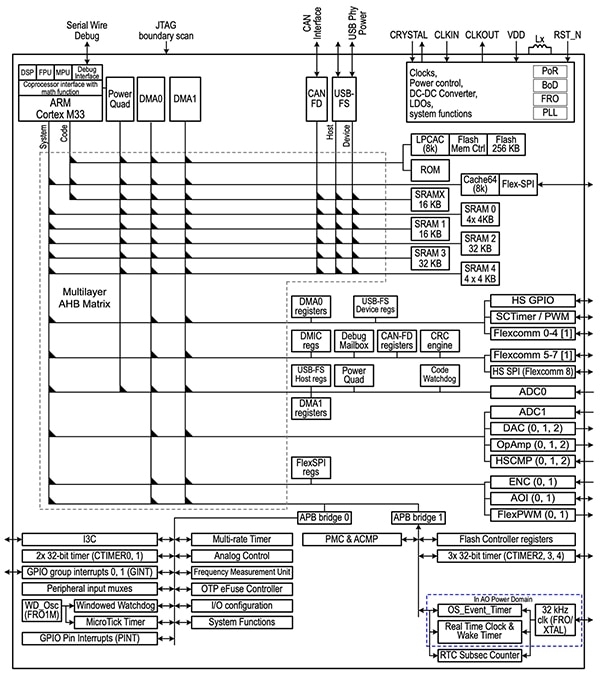

如圖 2(左)所示,基本的 I3C 網(wǎng)絡(luò)至少包括一個主控制器和一個或多個 I3C 目標設(shè)備或從設(shè)備 。 主設(shè)備可以是 MCU,例如 NXP Semiconductors 的 [LPC5534JHI48-00MP](圖 4)。該器件是一款 32 位 Arm? Cortex?-M33 MCU,具有 128 KB SRAM 和 256 KB 閃存。其 Flexcomm 接口支持八個不同的串行接口,包括 I3C。

圖 4:LPC5534JHI48/00MP MCU 包括一個 I3C 接口和其他七個串行接口。(圖片來源:NXP Semiconductor)

圖 4:LPC5534JHI48/00MP MCU 包括一個 I3C 接口和其他七個串行接口。(圖片來源:NXP Semiconductor)

I3C 總線允許添加作為從設(shè)備引入總線的輔助主設(shè)備。I3C 可以有多個主設(shè)備,但只能有一個是控制器。一旦注冊,輔助主設(shè)備即可請求獲取當前主設(shè)備狀態(tài),如果當前主設(shè)備同意,其控制權(quán)將移交給提出請求的輔助主設(shè)備。

NXP 的 [P3T2030CUKAZ]就是一種典型的 I3C 傳感器。該溫度傳感器可將 -40°C 至 +125°C 的溫度轉(zhuǎn)換為 12 位數(shù)值,精度為 ±2°C。該器件包括一個 I2C 和一個 I3C SDR 模式串行接口。

[TDK InvenSense]的 [ICM-42605]三軸微機電系統(tǒng) (MEMS) 陀螺儀和加速計是更為復(fù)雜的傳感器。作為速率陀螺儀,該器件可測量 ±15.2 至 ±2000 °/s 的旋轉(zhuǎn)速率。而作為加速計,其量程為 ±2 至 ±15 g 。該器件可檢測運動、傾斜、輕擊或步數(shù)(計步器)。作為 I3C 傳感器,其在 SDR 模式下的工作頻率為 12.5 MHz,在 DDR 模式下為 25 MHz。

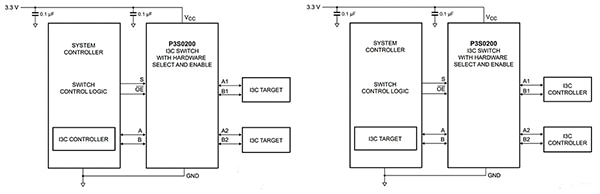

諸如 NXP [P3S0200GMX]I3C 開關(guān)之類的 IC 可在 I3C 控制器和多組目標設(shè)備之間,或在由外部 MCU 確定的單個目標設(shè)備和多個 I3C 控制器之間路由 I3C 總線信號,從而重新配置 I3C 總線(圖 5)。

圖 5:P3S0200GMX I3C 開關(guān)可用于在 I3C 控制器和多組目標設(shè)備之間,或在單個目標設(shè)備和多個 I3C 控制器之間路由 I3C 總線信號,從而重新配置 I3C 總線。(圖片來源:NXP Semiconductors)

圖 5:P3S0200GMX I3C 開關(guān)可用于在 I3C 控制器和多組目標設(shè)備之間,或在單個目標設(shè)備和多個 I3C 控制器之間路由 I3C 總線信號,從而重新配置 I3C 總線。(圖片來源:NXP Semiconductors)

如果兩個目標具有相同的地址,且不能位于同一總線上,則可能需要在兩個目標之間進行切換。另外,兩個進程可能須共享一個目標,這需要在兩個 I3C 控制器之間進行切換。

結(jié)語

I3C 是一種串行接口,通過提高數(shù)據(jù)速率、減少線數(shù)和增加總線控制的靈活性來擴展 I2C 總線。這種增強版總線可擴展傳統(tǒng) I2C 和 SPI 接口的實用性。

審核編輯 黃宇

-

傳感器

+關(guān)注

關(guān)注

2553文章

51390瀏覽量

756560 -

控制器

+關(guān)注

關(guān)注

112文章

16445瀏覽量

179431 -

串行接口

+關(guān)注

關(guān)注

3文章

331瀏覽量

42723 -

機電系統(tǒng)

+關(guān)注

關(guān)注

0文章

49瀏覽量

14013 -

i3c

+關(guān)注

關(guān)注

0文章

31瀏覽量

4881

發(fā)布評論請先 登錄

相關(guān)推薦

如何利用I3C提升嵌入式系統(tǒng)性能

從I2C升級革新到I3C,I3C能否取代傳統(tǒng)接口?

STM32H563的I3C無法正常通信是為什么?

Gowin I3C SDR IP的參考設(shè)計

Gowin I3C SDR IP參考設(shè)計

基于MIPI I3C規(guī)范從I2C無縫連接I3C的關(guān)鍵優(yōu)點

符合最新MIPI I3C規(guī)范的DesignWare IP提供高帶寬和可擴展性

Gowin I3C SDR IP參考設(shè)計

I3C協(xié)議規(guī)范的詳細內(nèi)容

I3C Introduction是什么意思

I2C和I3C的區(qū)別有哪些

I2C和I3C關(guān)于功耗和傳輸速率的對比

什么是I2C接口?什么是I3C接口?I2C與I3C的區(qū)別

什么是I3C接口 I3C和SPI接口有什么區(qū)別

I3C接口通信基礎(chǔ)

利用 I3C 實現(xiàn)更快、更簡單、更靈活的集成電路間通信

利用 I3C 實現(xiàn)更快、更簡單、更靈活的集成電路間通信

評論