在最新發(fā)布的 AMD VivadoDesign Suite 2024.2 中,引入的新特性之一是啟用了僅適用于 AMD Versal自適應(yīng) SoC 器件的 Advanced Flow 布局布線。關(guān)于此特性,文檔 UG904 以及 AR#000036830 均有說(shuō)明,本文基于此做些擴(kuò)展匯總,以幫助讀者對(duì) Advanced Flow 有更全面的了解。

為何要引入新的布局布線?

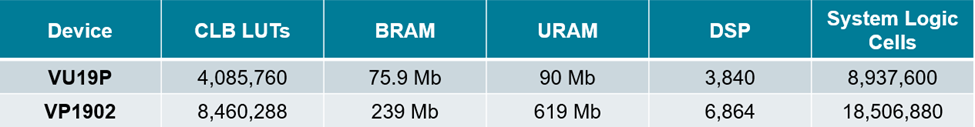

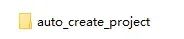

AMD Versal 自適應(yīng) SoC 將強(qiáng)大的可編程邏輯與加速引擎以及先進(jìn)的內(nèi)存和接口技術(shù)相結(jié)合,為各種應(yīng)用提供定制且高效的異構(gòu)加速。Versal 器件的邏輯密度顯著提高,從而提高了性能和容量。下表比較了 AMD UltraScale+ FPGA系列的 VU19P 與 Versal Premium 系列的 VP1902,后者是一款大型器件。

從 UltraScale+ 過(guò)渡到 Versal 器件已導(dǎo)致關(guān)鍵資源顯著增加:CLB LUT、BRAM、URAM、DSP 和邏輯單元的數(shù)量增加了一倍。這一增強(qiáng)功能能實(shí)現(xiàn)更復(fù)雜的設(shè)計(jì)。然而,隨著邏輯密度的增加,編譯時(shí)間也呈非線性增長(zhǎng)。

隨著設(shè)計(jì)變得越來(lái)越復(fù)雜,需要 AMD VivadoDesign Suite 工具進(jìn)行創(chuàng)新,以有效管理和應(yīng)對(duì)以下方面的挑戰(zhàn):

編譯時(shí)間

設(shè)計(jì)收斂

擁塞問(wèn)題

Advanced Flow 相較于 Vivado 傳統(tǒng)的 Standard Flow 而言,旨在提高設(shè)計(jì)效率并縮短編譯時(shí)間,適用于更大、更復(fù)雜、功能豐富的 Versal 自適應(yīng) SoC。

為了應(yīng)對(duì) Versal 架構(gòu)編譯時(shí)間更長(zhǎng)的挑戰(zhàn),優(yōu)化和加速布局布線過(guò)程至關(guān)重要。增強(qiáng)這一步驟將有助于管理 Versal 自適應(yīng) SoC 的復(fù)雜性。

從 2024.2 版本開(kāi)始,Vivado Design Suite 為所有 Versal 器件引入了 Advanced Flow。這種新流程具有新的布局布線算法,可提高設(shè)計(jì)性能、改善可布線性并更好地解決復(fù)雜的時(shí)鐘布局要求。額外的架構(gòu)改進(jìn)增強(qiáng)了將大型復(fù)雜問(wèn)題分解為可以并行解決的小問(wèn)題的能力。

Advanced Flow 的引入顯著加快了編譯時(shí)間,改善了 Versal 設(shè)計(jì)的 QoR,從而有助于提高整體生產(chǎn)力和加速設(shè)計(jì)迭代。

新流程詳述

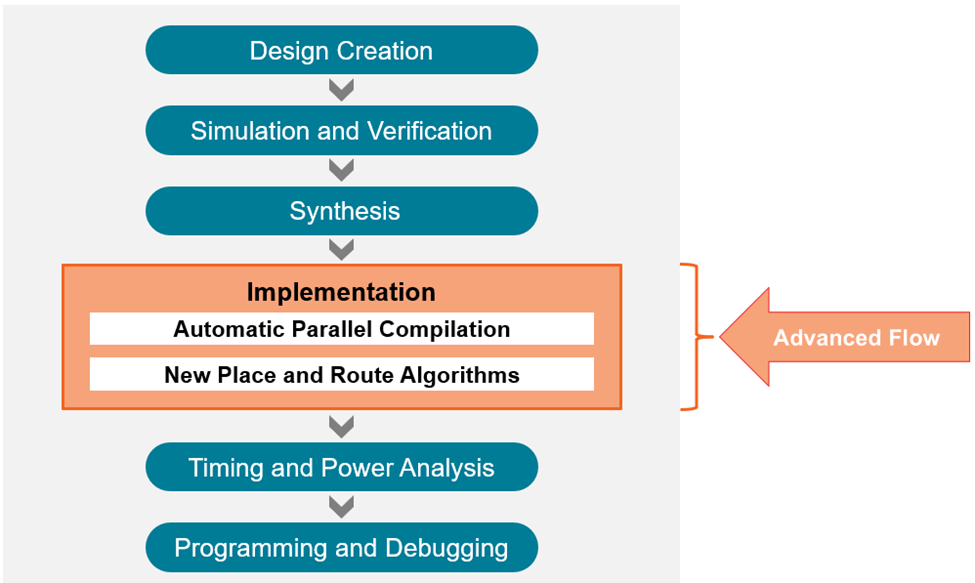

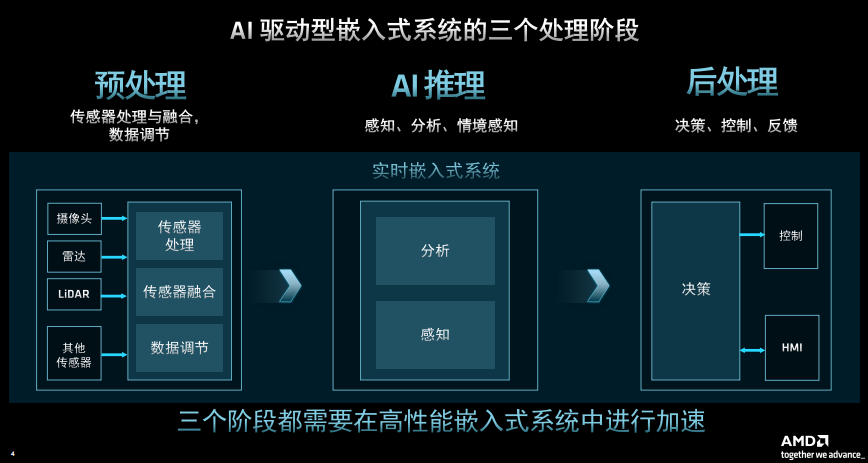

典型的設(shè)計(jì)流程從設(shè)計(jì)創(chuàng)建開(kāi)始,然后是所有設(shè)計(jì)功能的模擬和驗(yàn)證,然后進(jìn)入綜合階段。Advanced Flow 的主要重點(diǎn)是 Implementation 階段,其中包括自動(dòng)并行編譯和新的布局和布線算法,如下圖所示:

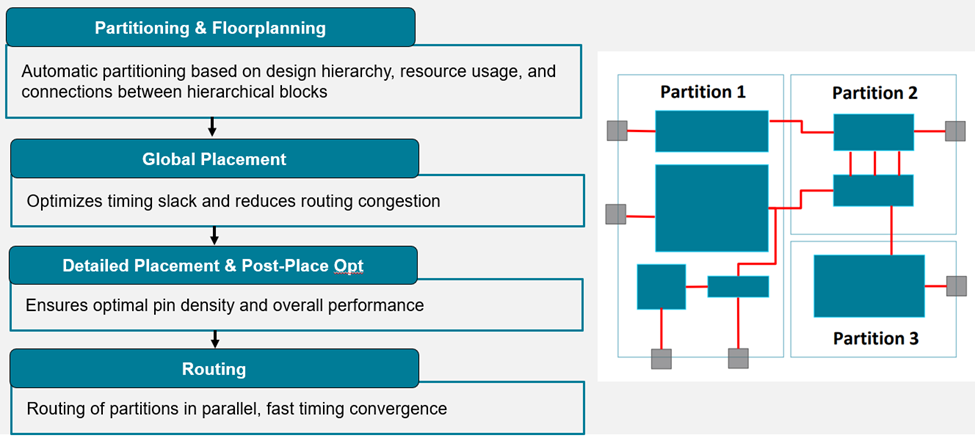

Advanced Flow 引入了改進(jìn)的分區(qū)和布局規(guī)劃方法,可優(yōu)化并行編譯。新算法有助于放置復(fù)雜的時(shí)鐘網(wǎng)絡(luò)、減少擁塞并提高整體性能。這種架構(gòu)和算法的組合大大加快了編譯過(guò)程。Placement 后,分區(qū)信息將傳遞到 Router,以便可以并行布線分區(qū)。

后續(xù)流程(例如時(shí)序和功率分析、編程和調(diào)試)與 AMD VivadoDesign Suite 的先前版本相同。

Advanced Flow 之所以成為 AMD Versal自適應(yīng) SoC器件更強(qiáng)大的解決方案,主要得益于其自動(dòng)分區(qū)以實(shí)現(xiàn)并行處理的功能。

自動(dòng)分區(qū)將大型復(fù)雜設(shè)計(jì)劃分為可以并行解決的較小布局和布線問(wèn)題,以更有效地處理分區(qū)的并行編譯。對(duì)于 SSI 設(shè)備,這涉及將邏輯劃分為 SLR,對(duì)于單片設(shè)備,將邏輯劃分為設(shè)備內(nèi)的不同區(qū)域。

分區(qū)器會(huì)分析設(shè)計(jì)層次結(jié)構(gòu)、資源使用情況以及模塊之間的連接,自動(dòng)完成設(shè)計(jì)分區(qū)。分區(qū)后,設(shè)計(jì)將以并行方式進(jìn)行布局,從全局布局階段開(kāi)始,通過(guò)粗略級(jí)別的時(shí)序和擁塞優(yōu)化進(jìn)行整個(gè)設(shè)備的設(shè)計(jì)布局。下一階段的詳細(xì)布局和布局后優(yōu)化器將優(yōu)化全局布局,以確保最佳引腳密度和最佳整體性能。

然后,分區(qū)信息將傳遞到布線器,布線器將使用相同的分區(qū)進(jìn)行并行布線,從而實(shí)現(xiàn)非常快速的時(shí)序收斂。

與之前的版本一樣,物理優(yōu)化(Phys Opt Design 步驟)可在布局后的任何時(shí)間使用,以改善時(shí)序。

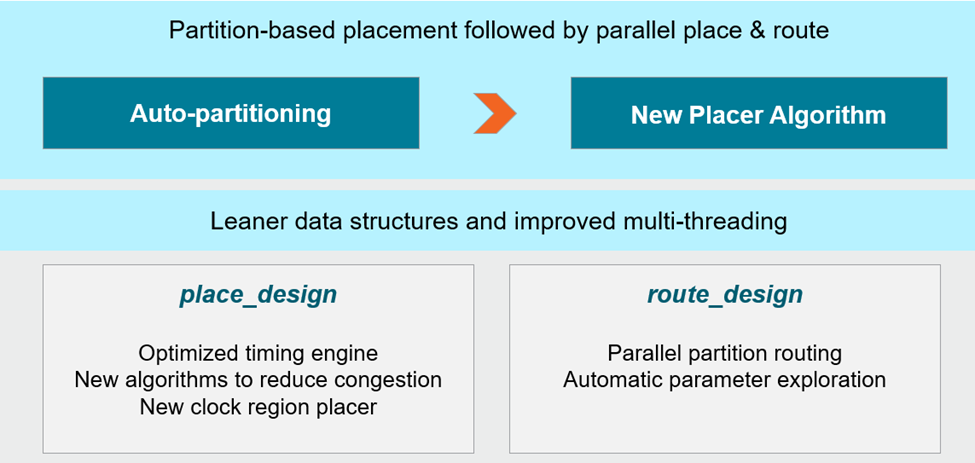

在 Vivado 內(nèi)部,Advanced Flow 使用更精簡(jiǎn)的數(shù)據(jù)結(jié)構(gòu)來(lái)存儲(chǔ)和檢索物理設(shè)計(jì)信息,這不僅提高了布局和布線速度,而且還提高了使用 Checkpoint 讀寫(xiě)大型設(shè)計(jì)的能力,減小了內(nèi)存占用。多線程的改進(jìn)進(jìn)一步提高了布局和布線效率。

新的時(shí)序引擎經(jīng)過(guò)優(yōu)化,可與布局器及其數(shù)據(jù)結(jié)構(gòu)配合使用,有助于快速評(píng)估布局更改的時(shí)序影響。此外,布局器還增加了減少每個(gè)方向的布線擁塞的功能,從而顯著提高了整體設(shè)計(jì)的可布線性。新的時(shí)鐘區(qū)域布局器的容量大大增加,從而可以更好地處理具有大量全局時(shí)鐘的復(fù)雜設(shè)計(jì)。

布線器可以從布局器獲取分區(qū)信息來(lái)并行布線這些分區(qū),也可以提前預(yù)測(cè)要使用多少個(gè)分區(qū)。初始布線后,會(huì)自動(dòng)探索布線算法的不同參數(shù)和閾值組合。布線器會(huì)選擇最佳組合,引導(dǎo)算法快速收斂到時(shí)序要求。

總體而言,這種新的工具架構(gòu)具有將大型復(fù)雜設(shè)計(jì)自動(dòng)分解為獨(dú)立分區(qū)的功能,無(wú)需用戶干預(yù)即可縮短編譯時(shí)間。

-

amd

+關(guān)注

關(guān)注

25文章

5496瀏覽量

134631 -

soc

+關(guān)注

關(guān)注

38文章

4204瀏覽量

219083 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

517瀏覽量

44178 -

Versal

+關(guān)注

關(guān)注

1文章

163瀏覽量

7710

原文標(biāo)題:開(kāi)發(fā)者分享|AMD Versal? 自適應(yīng) SoC 器件 Advanced Flow 概覽(上)

文章出處:【微信號(hào):gh_2d1c7e2d540e,微信公眾號(hào):XILINX開(kāi)發(fā)者社區(qū)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺(tái)之準(zhǔn)備工作(1)

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺(tái)之 Versal 介紹(2)

AMD Versal SoC刷新邊緣AI性能,單芯片方案驅(qū)動(dòng)嵌入式系統(tǒng)

Versal? 自適應(yīng) SoC 助力 8K 處理 – 為 8K 做好準(zhǔn)備(3)

Versal自適應(yīng)SoC系統(tǒng)和解決方案規(guī)劃方法指南

Versal 自適應(yīng)SoC設(shè)計(jì)指南

Versal自適應(yīng)SoC硬件、IP和平臺(tái)開(kāi)發(fā)方法指南

Versal自適應(yīng)SoC系統(tǒng)集成和 確認(rèn)方法指南

AMD率先推出符合DisplayPort? 2.1 8K視頻標(biāo)準(zhǔn)的FPGA和自適應(yīng)SoC

AMD Versal SoC全新升級(jí)邊緣AI性能,單芯片方案驅(qū)動(dòng)嵌入式系統(tǒng)

AMD發(fā)布第二代Versal自適應(yīng)SoC,AI嵌入式領(lǐng)域再提速

第二代AMD Versal Prime系列自適應(yīng)SoC的亮點(diǎn)

AMD Versal自適應(yīng)SoC CPM5 QDMA的Tandem PCIe啟動(dòng)流程介紹

AMD Versal自適應(yīng)SoC DDRMC如何使用Micron仿真模型進(jìn)行仿真

AMD Versal自適應(yīng)SoC器件Advanced Flow概覽(下)

AMD Versal自適應(yīng)SoC器件Advanced Flow概覽(上)

AMD Versal自適應(yīng)SoC器件Advanced Flow概覽(上)

評(píng)論