一般來(lái)講,如果要實(shí)現(xiàn)移位寄存器的話,通常都是寫RTL用reg來(lái)構(gòu)造,比如1bit變量移位一個(gè)時(shí)鐘周期就用1個(gè)reg,也就是一個(gè)寄存器FF資源,而移位16個(gè)時(shí)鐘周期就需要16個(gè)FF,這種方法無(wú)疑非常浪費(fèi)資源。

Xilinx FPGA的SLICEM中的一個(gè)查找表LUT可以配置為最多移位32個(gè)時(shí)鐘周期的移位寄存器,這比直接用FF來(lái)搭省了31個(gè)FF資源。

這種方法可以通過(guò)調(diào)用原語(yǔ)SRL16E(最多16個(gè)周期)和SRLC32E(最多32個(gè)周期)來(lái)實(shí)現(xiàn)。

SRL16E #(

.INIT(16'h0000), // Initial contents of shift register

.IS_CLK_INVERTED(1'b0) // Optional inversion for CLK

)

SRL16E_inst (

.Q(Q), // 1-bit output: SRL Data

.CE(CE), // 1-bit input: Clock enable

.CLK(CLK), // 1-bit input: Clock

.D(D), // 1-bit input: SRL Data

// Depth Selection inputs: A0-A3 select SRL depth

.A0(A0),

.A1(A1),

.A2(A2),

.A3(A3)

);

// End of SRL16E_inst instantiation

// SRLC32E: 32-bit variable length cascadable shift register LUT (Mapped to a SliceM LUT6)

// with clock enable

SRLC32E #(

.INIT(32'h00000000) // Initial Value of Shift Register

) SRLC32E_inst (

.Q(Q), // SRL data output

.Q31(Q31), // SRL cascade output pin

.A(A), // 5-bit shift depth select input

.CE(CE), // Clock enable input

.CLK(CLK), // Clock input

.D(D) // SRL data input

);

// End of SRLC32E_inst instantiation

如果需要實(shí)現(xiàn)更多時(shí)鐘周期的移位寄存器,則可以使用多個(gè)SRLC32E或者SRL16E來(lái)級(jí)聯(lián)實(shí)現(xiàn)。

IP核的定制

除了用原語(yǔ)實(shí)現(xiàn)外,還可以調(diào)用RAM-Based Shift Register這個(gè)IP核來(lái)實(shí)現(xiàn)。IP核實(shí)現(xiàn)方法使用不如原語(yǔ)方便,但是其對(duì)實(shí)現(xiàn)方式做了一些優(yōu)化,具有比原語(yǔ)更好的時(shí)序性能。

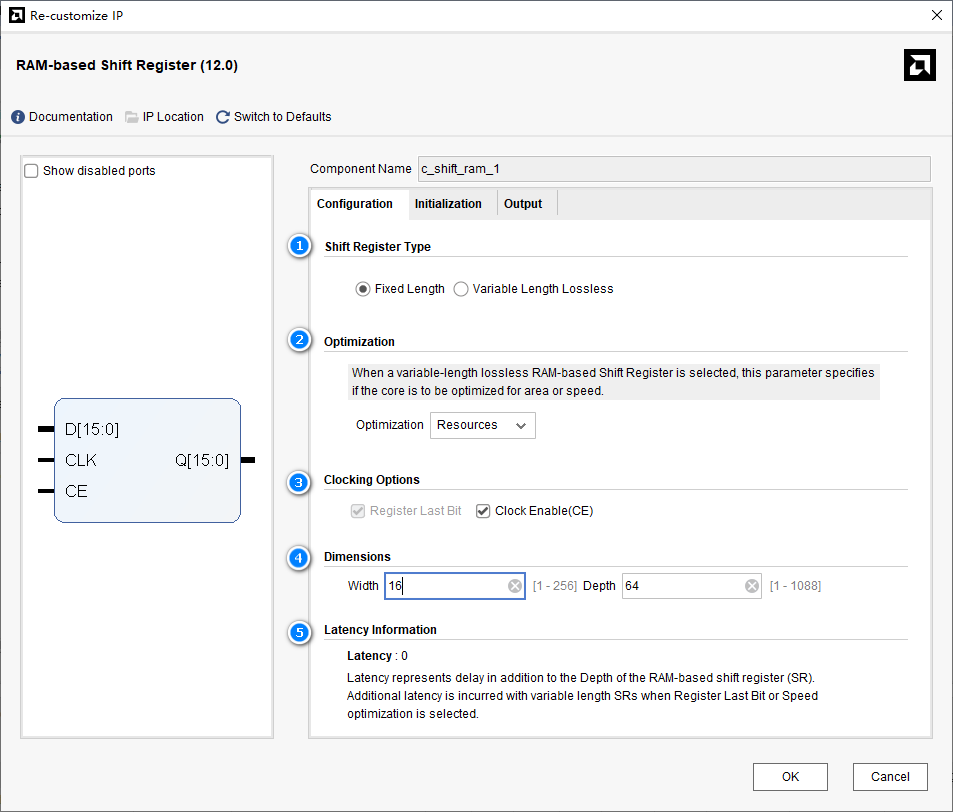

第一頁(yè)內(nèi)容

Shift Register Type:fixed length為固定長(zhǎng)度;variable length lossless為可變長(zhǎng)度

optimization:只有選擇可變長(zhǎng)度時(shí)才可選,可以選擇優(yōu)化面積還是優(yōu)化時(shí)序。如果優(yōu)化時(shí)序,則可能會(huì)多幾個(gè)延遲latency。

clocking options:Register last bit只有選擇可變長(zhǎng)度時(shí)才可選,會(huì)把輸出寄存一拍以改善時(shí)序,同時(shí)增加一個(gè)時(shí)鐘的延遲。clock enable(CE)時(shí)鐘使能功能。

dimensions:width移位寄存器寬度,depth移位寄存器深度。

latency information:延遲信息,根據(jù)各個(gè)選項(xiàng)的不同,輸出延遲可能會(huì)增加1~3個(gè)時(shí)鐘周期。

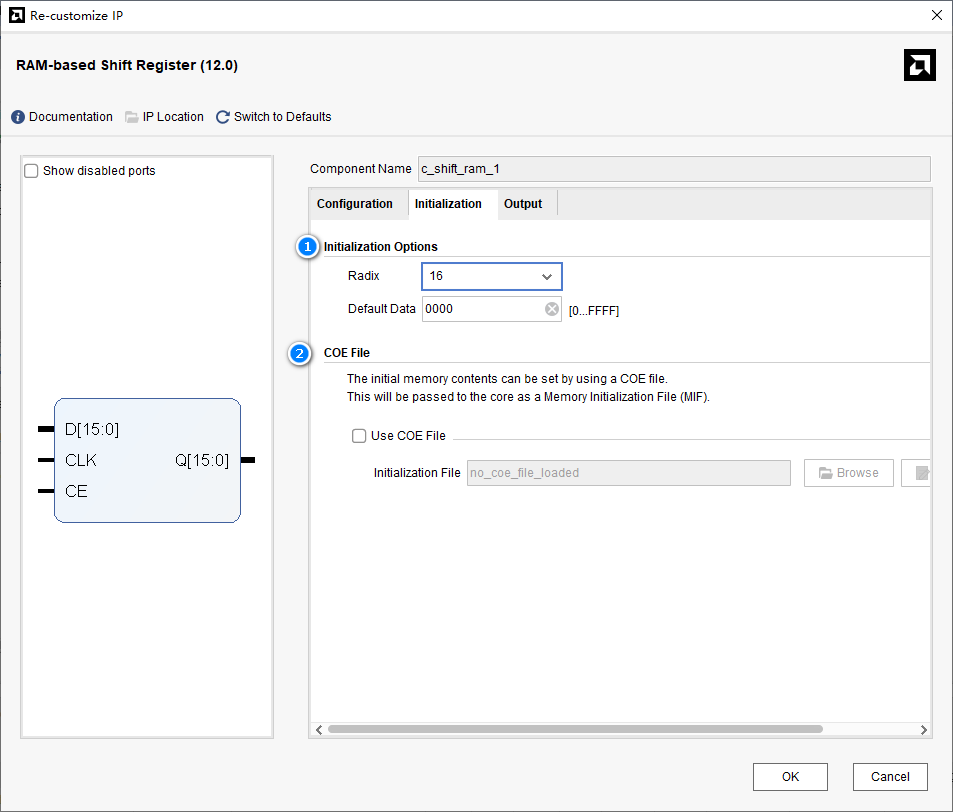

第二頁(yè)內(nèi)容

initialization options:初始化選項(xiàng),選擇初始化的進(jìn)制radix和默認(rèn)值default data。

COE file:初始化的值還可以選擇從COE文件來(lái)載入。

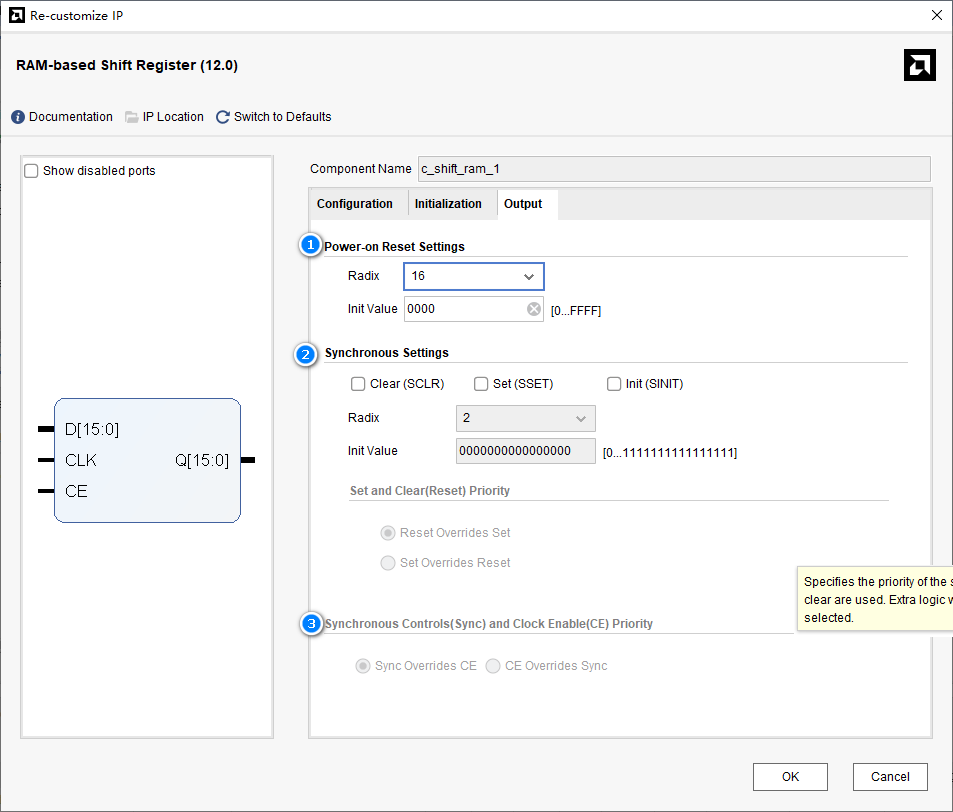

第三頁(yè)

power-on reset settings:上電復(fù)位設(shè)置選項(xiàng),選擇上電復(fù)位的進(jìn)制radix和初始值init data。

synchronous settings:同步設(shè)置,可以設(shè)置同步復(fù)位SCLR和同步置位SSET,二者的優(yōu)先級(jí)可選,默認(rèn)復(fù)位優(yōu)先級(jí)高于置位,如果選擇置位優(yōu)先級(jí)更高,則會(huì)消耗多余的資源。復(fù)位/置位與初始化SINT二者之間互斥。這三個(gè)選項(xiàng)一般都沒(méi)必要用。

synchronous controls(sync) and clock enable(CE) priority:選擇同步控制信號(hào)和CE信號(hào)的優(yōu)先級(jí)。默認(rèn)同步控制信號(hào)的優(yōu)先級(jí)高于CE,反之則會(huì)消耗多余的資源。

IP核的仿真使用

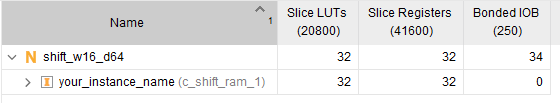

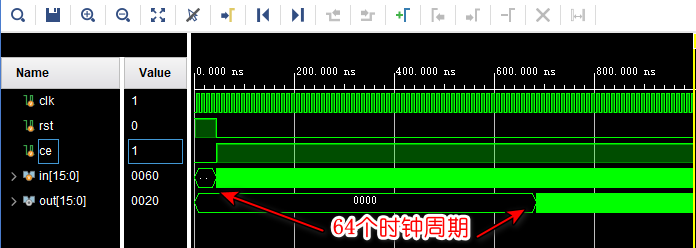

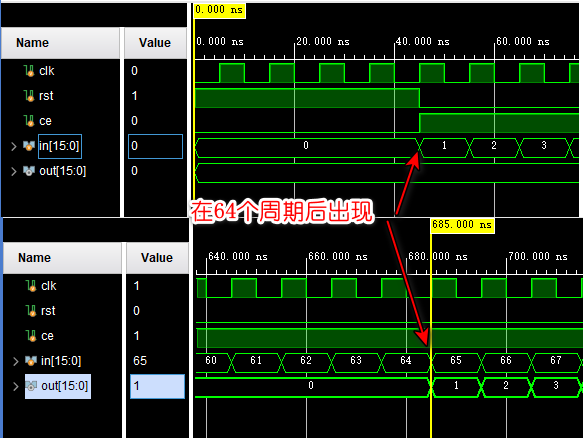

定制一個(gè)深度為64,位寬為16的IP核,然后編寫RTL代碼:

//固定的深度64個(gè)時(shí)鐘周期,位寬16的移位寄存器IP核設(shè)計(jì) module shift_w16_d64( inputclk,//時(shí)鐘信號(hào) input[15:0]in,//移位前的輸入數(shù)據(jù),位寬為16 inputce,//時(shí)鐘使能信號(hào) output[15:0]out//移位后的輸出,位寬為16 ); //移位寄存器IP;固定移位64個(gè)時(shí)鐘周期,位寬16 c_shift_ram_1 your_instance_name ( .D(in),//移位前的輸入數(shù)據(jù),位寬為16 .CLK(clk),//時(shí)鐘信號(hào) .CE(ce),//時(shí)鐘使能信號(hào) .Q(out)//移位后的輸出,位寬為16 ); endmodule

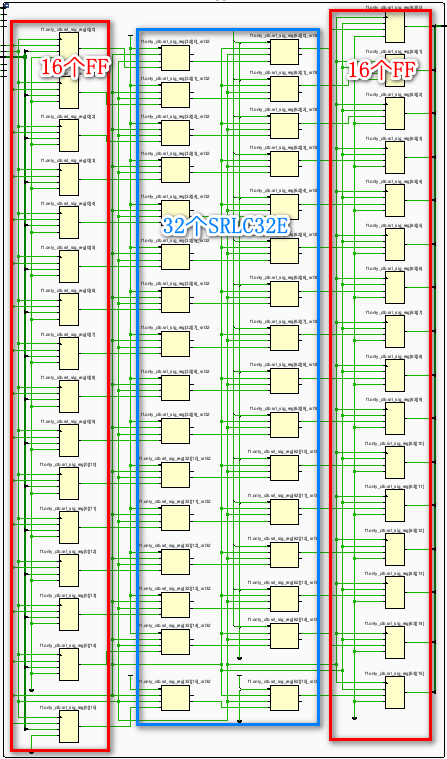

綜合后的資源使用情況:32個(gè)LUT + 32個(gè)FF。

看下綜合后的電路圖:

因?yàn)?個(gè)SRLC32E可以實(shí)現(xiàn)32個(gè)周期的移位,所以16×64的移位操作實(shí)際上只需要32個(gè)SRLC32E就可以實(shí)現(xiàn)了,為了改善時(shí)序性能,IP核在輸入端口和輸出端口一共用了2×16 = 32個(gè)FF來(lái)打拍寄存。

接下來(lái)編寫TB:時(shí)鐘使能信號(hào)一直拉高,輸入數(shù)據(jù)從1開(kāi)始累加。

`timescale 1ns/1ns

module tb_shift_w16_d64();

//信號(hào)聲明

regclk;

regrst;

reg[15:0]in;

regce;

wire[15:0]out;

//被測(cè)模塊實(shí)例化

shift_w16_d64inst_shift_w16_d64(

.clk(clk),

.in(in),

.ce(ce),

.out(out)

);

//生成時(shí)鐘信號(hào)

initial begin

clk= 1'b0;

forever #5 clk = ~clk;

end

//生成復(fù)位信號(hào)

initial begin

rst = 1'b1;//復(fù)位

#45 rst = 1'b0; //取消復(fù)位

end

//生成輸入數(shù)據(jù)與時(shí)鐘使能信號(hào)

always @(posedge clk or posedge rst)begin

if(rst)begin

in <= 16'd0;

ce <= 1'b0;

end

else begin

in <= in + 1'b1;//輸入數(shù)據(jù)累加1

ce <= 1'b1;//時(shí)鐘使能信號(hào)一直拉高

end

end

//仿真過(guò)程

initial begin

#1000 $stop;//關(guān)閉仿真

end

endmodule

仿真結(jié)果如下:

原文鏈接:

https://gitcode.csdn.net/65e6e9d51a836825ed787cef.html

-

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

121151 -

Xilinx

+關(guān)注

關(guān)注

71文章

2171瀏覽量

122124 -

IP核

+關(guān)注

關(guān)注

4文章

331瀏覽量

49634

原文標(biāo)題:RAM-Based Shift Register Xilinx IP核的使用

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

想要仿真下Quartus中的Shift Register(RAM-based),但是modelsim仿...

移位寄存器Shift Register(RAM-based)的如何實(shí)現(xiàn)延時(shí)

xilinx FPGA的FFT IP核的調(diào)用

RAM—based shift register如何設(shè)置

RAM—based shift register如何設(shè)置

移位寄存器的輸出與時(shí)鐘不對(duì)齊

Gowin RAM Based Shift Register IP用戶指南

Gowin RAM Based Shift Register IP參考設(shè)計(jì)

Gowin RAM Based Shift Register IP用戶指南及參考設(shè)計(jì)

英創(chuàng)信息技術(shù)WinCE RAM-Based與Hive-Based注冊(cè)表介紹

Gowin RAM Based Shift Register用戶指南

Gowin RAM Based Shift Register參考設(shè)計(jì)

如何申請(qǐng)xilinx IP核的license

RAM-Based Shift Register Xilinx IP核的使用

RAM-Based Shift Register Xilinx IP核的使用

評(píng)論