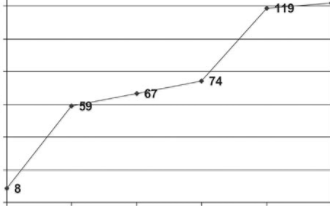

相信每一個電子工程師在項目開發的過程中都不可避免的要進行方案的調試,除了模擬調試我們還必須進行真機調試才能確保功能的正常,通常我們采用的調試方法分為兩種:第一種是使用硬件邏輯分析儀,第二種是采用嵌入邏輯分析IP,通過JTAG連接開發IDE進行調試,但是隨著FPGA設計越來越復雜,速度越來越快,這兩種方案顯得越來越捉襟見肘,邏輯分析儀會占用太多的FPGA I/O接口,嵌入式邏輯分析IP又會消耗寶貴的FPGA邏輯資源,因此Exostiv Labs公司推出了新型的調試工具EXOSTIV Probe。

圖1:傳統FPGA調試方案:硬件邏輯分析儀和嵌入式邏輯分析IP

EXOSTIV Probe從各方面都優于傳統方案,它支持Xilinx All Programmable所有系列,采用高速SerDes接口實現數據采集和通信,EXOSTIV Probe能夠采集多達32768個內部信號節點,此外EXOSTIV IP提供動態多路復用控制功能,能夠動態采集更多的數據集而不需要重新進行編譯。

圖2:EXOSTIV Probe硬件調試儀

EXOSTIV Probe提供8GB的存儲空間用于存儲從FPGA中采集到的數據,高速USB 3.0接口用于實現EXOSTIV應用上位機與EXOSTIV之間的通信,集成了四個SFP/SFP+收發器接口,每個接口速度可達6.6Gbps。此外上位機EXOSTIV Dashboard由Core Inserter和Analyzer兩大功能組件組成,Core Inserter可以動態配置EXOSTIV IP,Analyzer則實現采集數據的管理、顯示分析并且導出,MYRIAD波形顯示插件支持TB級波形數據的顯示。

EXOSTIV Pobe結合Xilinx Virtex UltraScale VCU108開發板卡調我們看到現在很多新興行業,比如云計算、5G通信、人工智能(AI)、機器學習、自動駕駛等應用場景都需要強大的計算能力來支持,因此FPGA的應用越來越多,這些設計不僅復雜,占用更多的邏輯資源,同時信號速度也呈現指數級別的增加,EXOSTIV Probe的出現提供了更強大的信號可視化能力,毫無疑問的方便了電子工程師們的調試工作,更快的將FPGA設計方案交付。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605996 -

邏輯分析儀

+關注

關注

3文章

214瀏覽量

23268

原文標題:高速FPGA設計方案調試利器:EXOSTIV Probe

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

簡化Xilinx和Altera FPGA調試過程

實用FPGA的調試工具—ChipScope Pro

FPGA硬件電路的調試必備原則和技巧

FPGA設計的創新調試手段

采用內部或者嵌入式邏輯分析儀推動FPGA調試技術改變

傳統FPGA調試方案與EXOSTIV Probe硬件調試儀

傳統FPGA調試方案與EXOSTIV Probe硬件調試儀

評論