verilog語(yǔ)言是什么

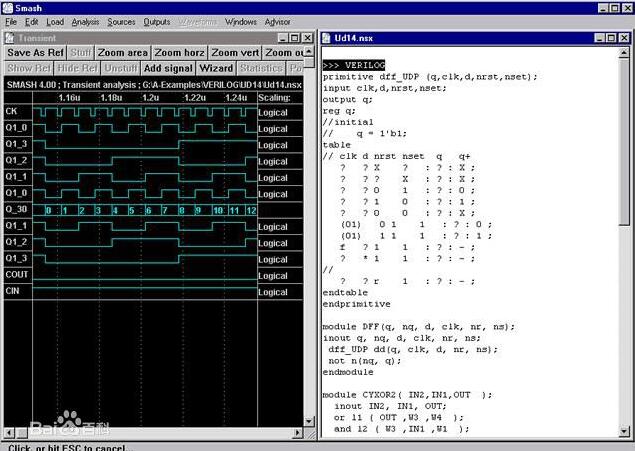

Verilog HDL是一種硬件描述語(yǔ)言(HDL:Hardware Description Language),以文本形式來(lái)描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語(yǔ)言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。

Verilog HDL是目前應(yīng)用最為廣泛的硬件描述語(yǔ)言.Verilog HDL可以用來(lái)進(jìn)行各種層次的邏輯設(shè)計(jì),也可以進(jìn)行數(shù)字系統(tǒng)的邏輯綜合,仿真驗(yàn)證和時(shí)序分析等。Verilog HDL適合算法級(jí),寄存器級(jí),邏輯級(jí),門(mén)級(jí)和版圖級(jí)等各個(gè)層次的設(shè)計(jì)和描述。

Verilog HDL進(jìn)行設(shè)計(jì)最大的優(yōu)點(diǎn)是其工藝無(wú)關(guān)性.這使得工程師在功能設(shè)計(jì),邏輯驗(yàn)證階段可以不必過(guò)多考慮門(mén)級(jí)及工藝實(shí)現(xiàn)的具體細(xì)節(jié),只需根據(jù)系統(tǒng)設(shè)計(jì)的要求施加不同的約束條件,即可設(shè)計(jì)出實(shí)際電路。

Verilog HDL是一種硬件描述語(yǔ)言(hardware description language),為了制作數(shù)字電路而用來(lái)描述ASICs和FPGA的設(shè)計(jì)之用。Verilog 的設(shè)計(jì)者想要以 C 編程語(yǔ)言為基礎(chǔ)設(shè)計(jì)一種語(yǔ)言,可以使工程師比較容易學(xué)習(xí)。

verilog語(yǔ)言基本語(yǔ)句有哪些

1、賦值語(yǔ)句:

(1)非阻塞賦值方式, 如 b《=a ;

特點(diǎn):塊結(jié)束后才完成操作,b的值不是立刻改變的。

(2)阻塞賦值方式, 如 b = a ;

特點(diǎn):賦值語(yǔ)句執(zhí)行完后,塊才結(jié)束,b的值是立刻改變的。

2、塊語(yǔ)句

(1)順序塊

顧明思議,就是順序執(zhí)行,這與C語(yǔ)言的順序結(jié)構(gòu)特性一樣。

格式如下:

語(yǔ)句1到n是順序執(zhí)行的,也可給塊命名,只需在begin后面加上“:塊名”即可。當(dāng)加給塊命名后,才可以在塊內(nèi)定義局部變量,和塊被其他語(yǔ)句調(diào)用,如disable語(yǔ)句。

(2)并行塊

同樣,從表面意思可知道,塊內(nèi)語(yǔ)句是并行進(jìn)行的,也就是同時(shí)進(jìn)行的。

當(dāng)執(zhí)行完所有語(yǔ)句或一個(gè)disable語(yǔ)句執(zhí)行時(shí),程序跳出并行塊。

并行塊的結(jié)構(gòu)和順序塊的結(jié)構(gòu)一樣,只需將關(guān)鍵字換成fork…join

注意:begin 、 end 、 fork 、 join 后面都沒(méi)有封號(hào)“;”。

3、條件語(yǔ)句

(1) if 語(yǔ)句

這里 if 語(yǔ)句與C語(yǔ)言沒(méi)有什么不同,只需注意,在C語(yǔ)言里,用大括號(hào)的地方,在Verilog里都用begin…end 。

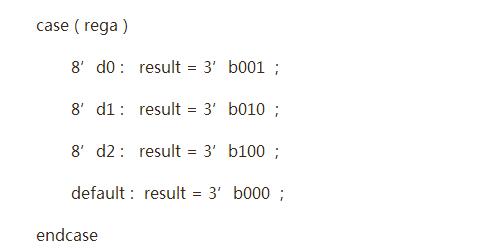

(2)case 語(yǔ)句

這個(gè)與C語(yǔ)言不同了,在Verilog里,沒(méi)有switch,只有case ,示例如下:

這里也不需要break , 每當(dāng)執(zhí)行完一個(gè)case 分項(xiàng)后的語(yǔ)句,則跳出該case語(yǔ)句,終止case語(yǔ)句的執(zhí)行。

另外,Verilog還提供了casex和casez兩個(gè)語(yǔ)句,他們?nèi)咧g有一定的區(qū)別。

在用case 語(yǔ)句時(shí),要求case括號(hào)中的值必須與分項(xiàng)中的值完全相等才執(zhí)行,即滿足“===”全等于的關(guān)系。

在用casex語(yǔ)句時(shí),將高阻值z(mì)和不定值x 都視為不關(guān)心的值,即不比較其所在位的值,只需其他位滿足全等于的關(guān)系即可。

在用casez語(yǔ)句時(shí),不考慮高阻值的z比較過(guò)程,只考慮x 、0、1三個(gè)值。

注意:if語(yǔ)句和case語(yǔ)句都只能用于always語(yǔ)句內(nèi)部,如果要在always語(yǔ)句之外應(yīng)用條件語(yǔ)句,可用三目運(yùn)算符 ? :如下:

assign data = ( sel ) ? a : b ;

4、循環(huán)語(yǔ)句

(1)for 語(yǔ)句 和 while 語(yǔ)句,這與C語(yǔ)言語(yǔ)法一樣。不解釋

(2)forever語(yǔ)句

forever循環(huán)常用于產(chǎn)生周期性的波形,用來(lái)作為仿真測(cè)試信號(hào)。它與always語(yǔ)句不同之處在于它不能獨(dú)立寫(xiě)在程序中,而必須寫(xiě)在initial塊中。

(3)repeat語(yǔ)句

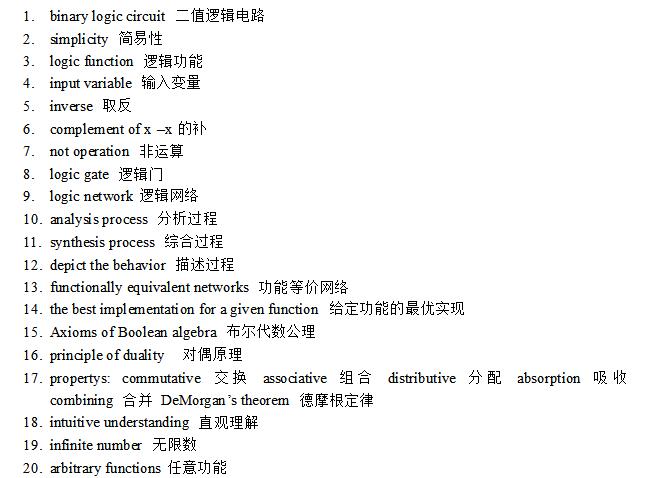

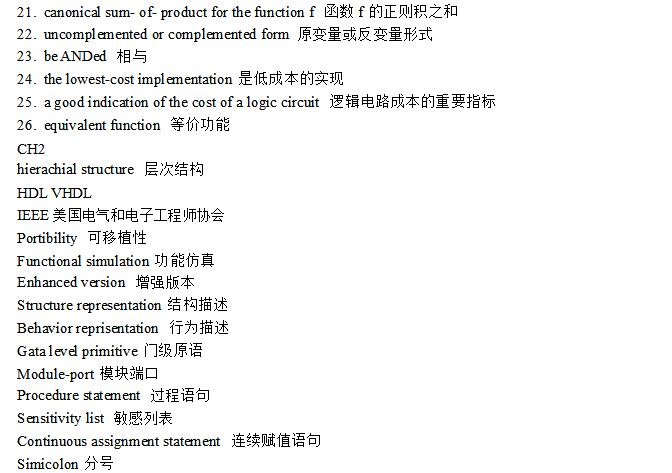

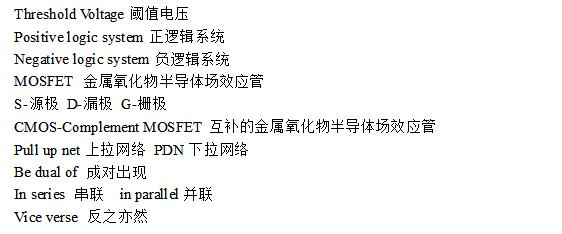

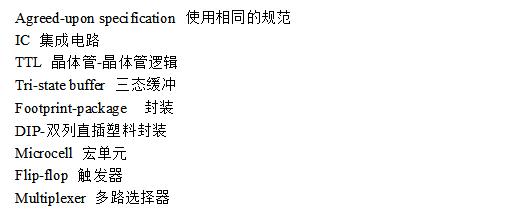

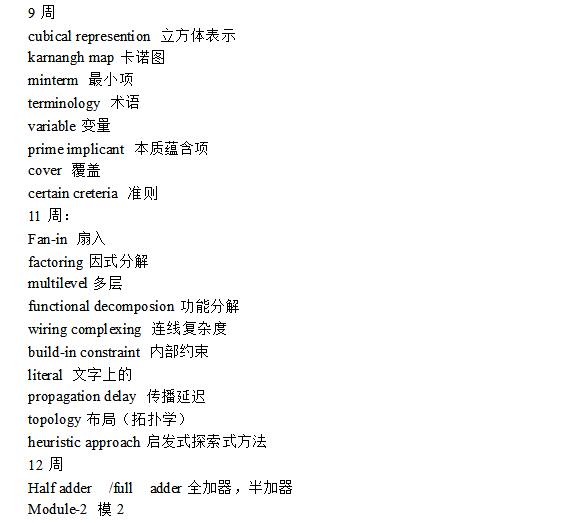

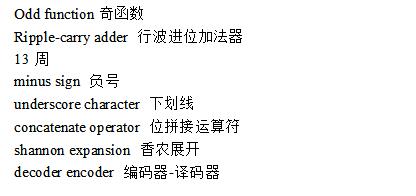

verilog語(yǔ)言詞匯大全

Verilog的主要應(yīng)用

1、ASIC和FPGA工程師編寫(xiě)可綜合的RTL代碼

2、 高抽象級(jí)系統(tǒng)仿真進(jìn)行系統(tǒng)結(jié)構(gòu)開(kāi)發(fā)

3、測(cè)試工程師用于編寫(xiě)各種層次的測(cè)試程序

4、用于ASIC和FPGA單元或更高層次的模塊的模型開(kāi)發(fā)

如何學(xué)習(xí)verilog語(yǔ)言

如果搞FPGA開(kāi)發(fā)verilog必然要精通。如果沒(méi)有數(shù)字電路基礎(chǔ)的話建議首先學(xué)一些基本的數(shù)字電路知識(shí)。

然后看書(shū),《Verilog HDL數(shù)字設(shè)計(jì)與綜合》,一定注意只要看能夠綜合的代碼,那些不能綜合的東西可以一帶而過(guò)。

實(shí)踐!實(shí)踐!實(shí)踐!光看書(shū)絕對(duì)學(xué)不會(huì)。如果你有開(kāi)發(fā)板當(dāng)然好,如果沒(méi)有至少也要寫(xiě)程序仿真。當(dāng)時(shí)我學(xué)的時(shí)候買(mǎi)了個(gè)幾千塊的開(kāi)發(fā)板。這個(gè)東西不練絕對(duì)學(xué)不會(huì)。

總之,先看書(shū),把基本的數(shù)電搞懂。然后最好學(xué)一點(diǎn)練一點(diǎn)。一個(gè)很有用的方法,就是對(duì)著書(shū)或者自己想一些代碼,然后看看編出的電路是什么樣子的。

FPGA和C語(yǔ)言等軟件語(yǔ)言相比,非常難以調(diào)試。一定要保證學(xué)的扎實(shí)些。

verilog是硬件描述語(yǔ)言,歸根結(jié)底你設(shè)計(jì)的是電路,而不是軟件,不能那C語(yǔ)言等軟件語(yǔ)言硬套。

學(xué)習(xí)verilog語(yǔ)言的注意事項(xiàng)

1、不使用初始化語(yǔ)句;

2、不使用延時(shí)語(yǔ)句;

3、不使用循環(huán)次數(shù)不確定的語(yǔ)句,如:forever,while等;

4、盡量采用同步方式設(shè)計(jì)電路;

5、盡量采用行為語(yǔ)句完成設(shè)計(jì);

6、always過(guò)程塊描述組合邏輯,應(yīng)在敏感信號(hào)表中列出所有的輸入信號(hào);

7、所有的內(nèi)部寄存器都應(yīng)該可以被復(fù)位;

8、用戶自定義原件(UDP元件)是不能被綜合的。

-

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110390 -

Verilog語(yǔ)言

+關(guān)注

關(guān)注

0文章

113瀏覽量

8309

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

討論Verilog語(yǔ)言的綜合問(wèn)題

Verilog HDL語(yǔ)言實(shí)現(xiàn)時(shí)序邏輯電路

Verilog HDL語(yǔ)言簡(jiǎn)介

VHDL和Verilog HDL語(yǔ)言對(duì)比

Verilog硬件描述語(yǔ)言參考手冊(cè)

基于verilog語(yǔ)言的數(shù)字頻率計(jì)設(shè)計(jì)

Verilog HDL硬件描述語(yǔ)言_Verilog語(yǔ)言要素

Verilog HDL語(yǔ)言中的分支語(yǔ)句

快速理解Verilog語(yǔ)言

Verilog是編程語(yǔ)言嗎

簡(jiǎn)述Verilog HDL中阻塞語(yǔ)句和非阻塞語(yǔ)句的區(qū)別

verilog語(yǔ)言基本語(yǔ)句_verilog語(yǔ)言詞匯大全

verilog語(yǔ)言基本語(yǔ)句_verilog語(yǔ)言詞匯大全

評(píng)論