PCI Spec規(guī)定了每個PCI總線上最多可以連接多達32個PCI設(shè)備,但是實際上卻遠遠達不到32個,33MHz的32位PCI總線一般只能連接10到12個負載。

注:如果使用插槽連接,則一個連接算兩個PCI設(shè)備,插槽和PCI卡分別算作一個PCI設(shè)備。也就是說一個33MHz的PCI總線最多只能連接4到5個插槽即PCI卡。

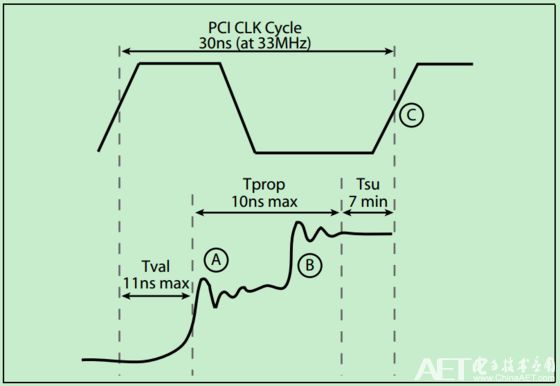

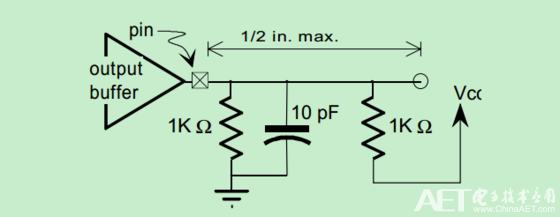

這是因為PCI總線在設(shè)計的時候,為了降低功耗,采用了一種叫做reflected‐wave signaling的技術(shù),如下圖所示:

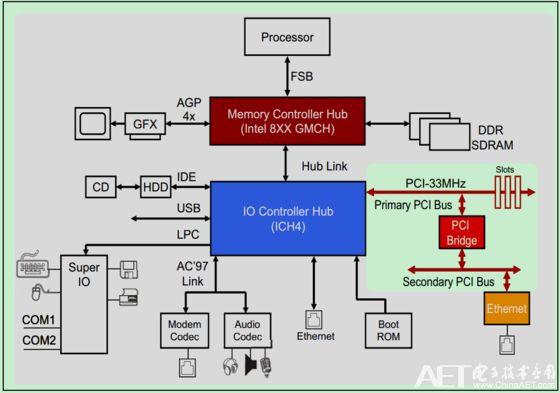

由圖可知,為了降低功耗PCI設(shè)備的發(fā)送端采用了一種 weak transmit buffers,其只能驅(qū)動信號電平達到實際需求的一半。然后依靠反射回來的信號疊加到原本的信號上,使得信號電平達到實際的需求。當(dāng)然,所有的這些過程都要求在一個時鐘周期內(nèi)完成,這種機制也限制了PCI總線頻率的提高,也限制了單個PCI總線上的最大連接設(shè)備的數(shù)量。如果需要連接更多的PCI設(shè)備,則需要借助PCI-to-PCI橋,每個橋的內(nèi)部都有隔離,這保證了每個橋又可以連接額外的10~12個負載。但是PCI Spec規(guī)定了,一個PCI總線系統(tǒng)中,最多只能有256個子總線。

此外,PCI總線的Input Buffer還沒有加輸入寄存器,這對信號的Setup時間提出了更高的要求。

一個包含PCI-to-PCI橋的33MHz PCI總線系統(tǒng)的架構(gòu)圖如下所示:

-

pci總線

+關(guān)注

關(guān)注

1文章

203瀏覽量

31930 -

信號

+關(guān)注

關(guān)注

11文章

2807瀏覽量

77117

原文標(biāo)題:【博文連載】PCIe掃盲——PCI總線中的Reflected-Wave Signaling

文章出處:【微信號:ChinaAET,微信公眾號:電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

PCI總線PCB設(shè)計丨實現(xiàn)高效外圍部件互連的關(guān)鍵要素

什么是PCI插槽

PCI 橋接器的技術(shù)發(fā)展近況

基于IP核的PCI總線接口設(shè)計與實現(xiàn)

PCI總線接口芯片9054及其應(yīng)用

分享:基于PCI總線的雙DSP系統(tǒng)及WDM驅(qū)動程序設(shè)計

Designing a 33MHz, 32-Bit PCI

Designing a 33MHz, 32-Bit PCI

LVDS總線技術(shù)有什么特點?在安全隔離網(wǎng)閘中有什么應(yīng)用?

如何設(shè)計一種以PCI總線為核心的微弱數(shù)據(jù)信號采集電路?

33MHz的32位PCI總線一般只能連接10到12個負載

33MHz的32位PCI總線一般只能連接10到12個負載

評論