將Quartus II中FPGA管腳的分配及保存方法做一個匯總。本文首先介紹了FPGA 的管腳分配方法,其次介紹了Quartus II自動添加管腳分配的方法,最后闡述了FPGA管腳分配文件保存方法,具體的跟隨小編一起來了解一下吧。

一、管腳分配方法

FPGA 的管腳分配,除了在QII軟件中,選擇“Assignments -》Pin”標簽(或者點擊按鈕) ,打開Pin Planner,分配管腳外,還有以下2種方法。

方法一:Import Assignments

步驟1:

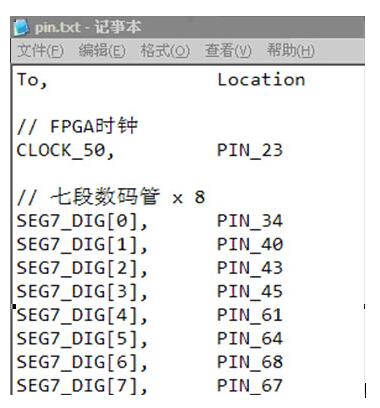

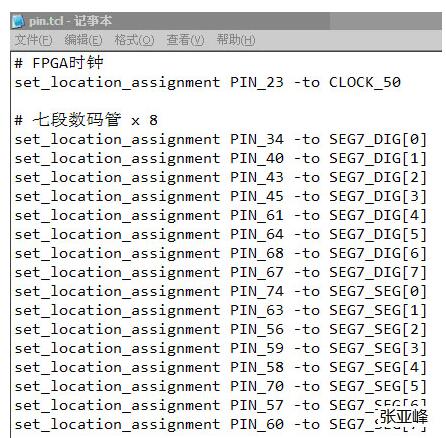

使用記事本或類似軟件新建一個txt文件(或csv文件),按如下格式編寫管腳分配內(nèi)容(不同的開發(fā)版,其內(nèi)容也不同,本文以我使用的DIY_DE2開發(fā)板為范例)。【這種方式格式最為簡單】

注意:To和Location兩個關(guān)鍵字中間有一個半角逗號。

圖1 pin.txt

步驟2:

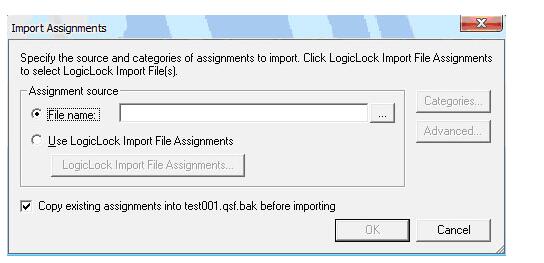

在QII軟件中,選擇“Assignments -》 Import Assignments”。如圖所示,導入xxx.txt或者xxx.csv文件即可

圖2 導入pin.txt

步驟3:

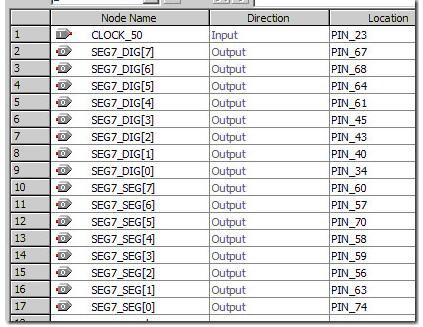

在QII軟件中,選擇“Assignments -》 Pin”標簽(或者點擊 按鈕) ,打開Pin Planner,驗證管腳是否分配正確。

圖3 驗證管腳是否分配正確

方法二:導入source xxx.tcl文件

步驟1:

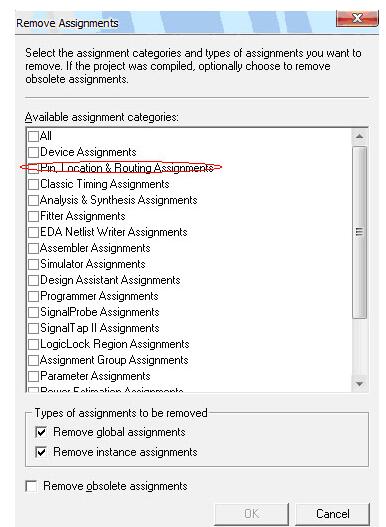

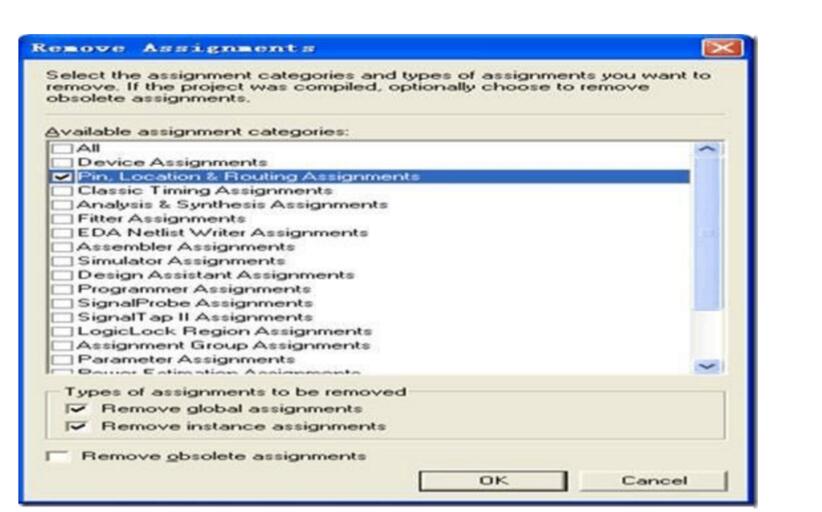

在QII軟件中,使用“Assignments -》 Remove Assignments”標簽,移除管腳分配內(nèi)容,以確保此次操作,分配的管腳沒有因為覆蓋而出現(xiàn)錯誤的情況。

圖4 Remove Assignments

注:在未執(zhí)行任何管腳分配操作新工程中,可跳過步驟1。

步驟2:

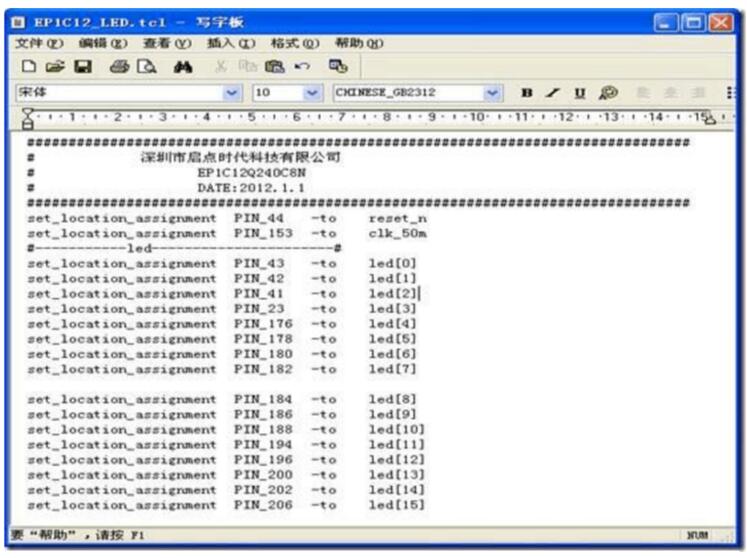

使用記事本或類似軟件新建一個tcl文件,按如下格式編寫管腳分配內(nèi)容(不同的開發(fā)版,其內(nèi)容也不同,本文以我使用的DIY_DE2開發(fā)板為范例)。

注意關(guān)鍵字set_location_assignment和-to的用法。

圖5 pin.tcl

步驟3:

執(zhí)行pin.tcl

方法1:在QII軟件中,使用“View -》 Utility Windows -》 Tcl Console”標簽,打開Quartus II Tcl Console。執(zhí)行語句:

圖6 source pin.tcl

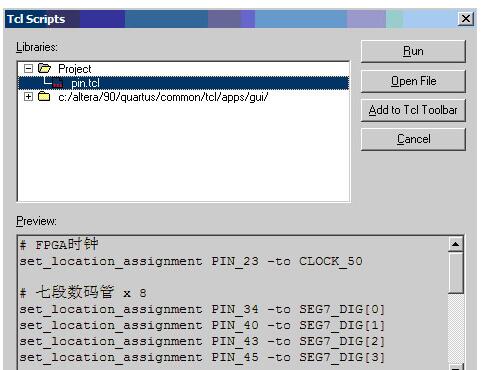

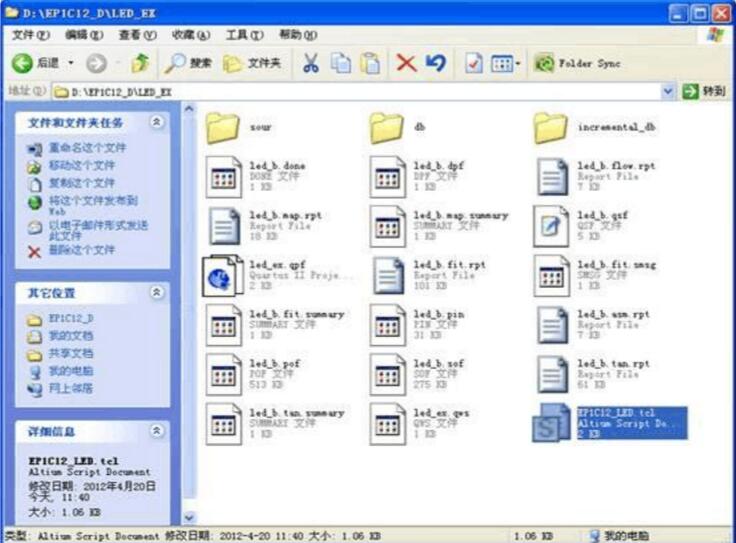

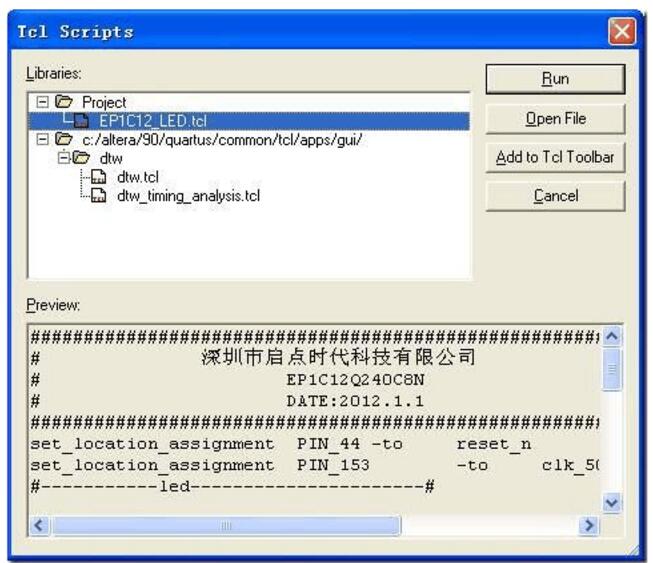

方法2:在QII軟件中,使用“Tools -》 Tcl Scripts …”標簽,打開Tcl Scripts。

圖7 Tcl Scripts

選擇pin.tcl,選擇“Run”標簽,執(zhí)行Tcl文件。

步驟4:

同方法1的步驟3。

步驟1:在QII軟件中,使用“Assignments —— Remove Assignments”標簽,移除管腳分配內(nèi)容,以確保此次操作,分配的管腳沒有因為覆蓋而出現(xiàn)錯誤的情況。

注:在未執(zhí)行任何管腳分配操作新工程中,可跳過步驟1。

步驟2:使用記事本或類似軟件新建一個TCL文件,按如下格式編寫管腳分配內(nèi)容(以EP1C12的 例程為例)

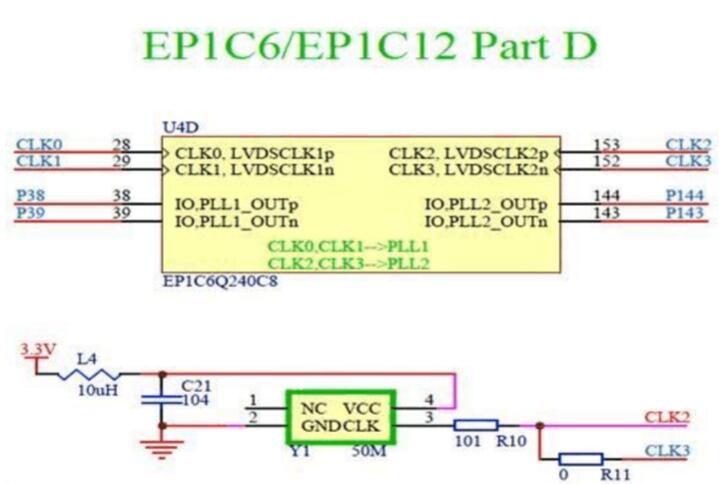

我們命名的名字就是后面那部分,PIN_*是FPGA硬件上癿引腳,-to后面的就是對應(yīng)的名字 如

set_location_assignment PIN_153 -to clk_50m

我們可以看到,原理圖中50MHz晶振Y1(CLK2)接的就是FPGA的153腳。 步驟3:將新建的TCL文件放到工程目錄文件夾下。

步驟4:執(zhí)行pin.tcl。

在QII軟件中,使用“Tools —— Tcl Scripts ?”標簽,打開Tcl Scripts

選擇pin.tcl,選擇“Run”標簽,執(zhí)行Tcl文件。

如下所示,又看見Successfully了吧,返說明我們腳本文件運行成功了

二、Quartus II自動添加管腳分配的方法

對CPLD大量管腳進行分配是件頭疼的事情。在Pin Planner里逐一添加比較麻煩。或者布線改動較多時需要逐一修改。

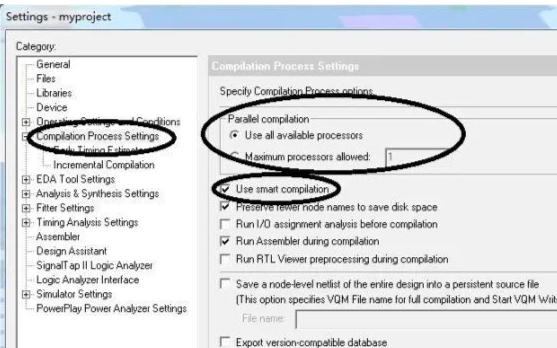

可以通過內(nèi)置tcl命令進行自動添加,步驟如下:

1. 新建一個文本文件,例如pin.txt

2. 添加多條管腳分配命令

set_location_assignment PIN_123 -to MODULE_PORT

其中,PIN_123是管腳123的編號,其它的類似。MODULE_PORT是TOP模塊的端口。

如果端口是多位的,則需使用如下命令

set_location_assignment PIN_123 -to MODULE_PORT[n]

其中,n表示端口的第n位

3. 在Quartus中打開Tcl console,可以通過快捷鍵Alt+2打開

4. 在Tcl console中粘貼pin.txt中所有命令,回車執(zhí)行

5. 自動分配完成!可以在Pin Planner中查看分配結(jié)果。保留pin.txt用于未來管腳的更改。

三、FPGA管腳分配文件保存方法

使用別人的工程時,有時找不到他的管腳文件,但可以把他已經(jīng)綁定好的管腳保存下來,輸出到文件里。

方法一:

查看引腳綁定情況,quartus -》 assignment -》 Pins,打開FPGA引腳界面,在這個界面的菜單中可以保存引腳文件為csv格式(表格形式)和tcl格式。

步驟:File -》 Export… -》 選擇保存名字和保存格式。

方法二:

直接輸出管腳配置,assignmengt -》 Export assignmengt,可以保存配置為qsf格式,該格式可以用記事本查看,在該文件中同樣包含了引腳信息。注意:保存時會在原工程文件夾下新建一個文件夾。

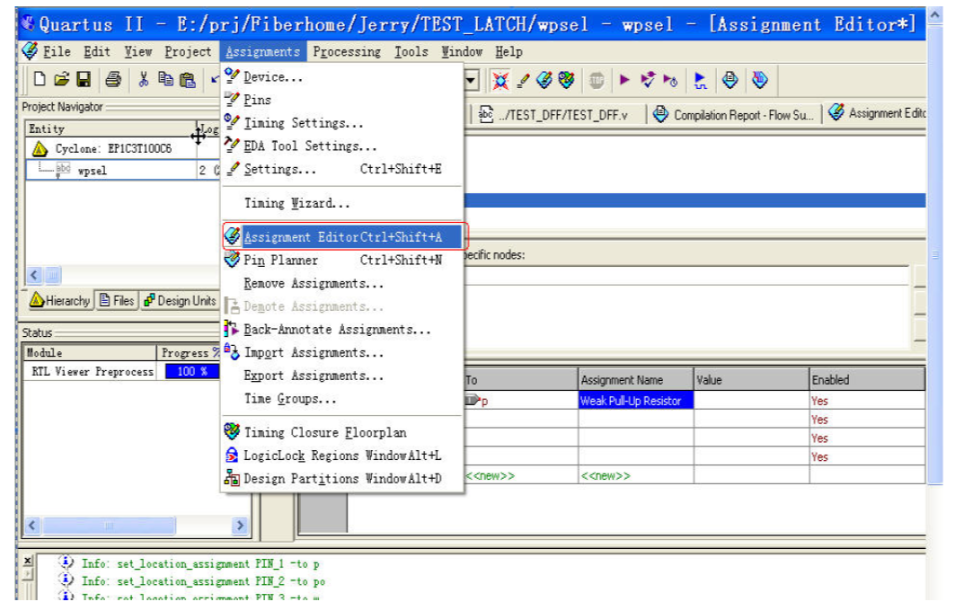

至于元件的其它配置方式,可以在qsf文件和tcl文件中用語句來設(shè)置,也可以在Assignment -》 device,界面中設(shè)置。

加載:

使用已經(jīng)有的引腳文件時,在選項assignment -》 Import assignment,中可以選擇要加載的引腳文件。此時,可以加載qsf 和 csv(或txt)文件。

保存的csv(txt)文件、qsf文件 和 tcl文件的區(qū)別:

csv(txt)文件:包含芯片所有管腳信息,包括分配的和未分配的;

qsf文件:包含管腳分配信息和芯片信息;

tcl文件:只包含已分配管腳信息。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605967 -

管腳分配

+關(guān)注

關(guān)注

1文章

5瀏覽量

7475

發(fā)布評論請先 登錄

相關(guān)推薦

我想問下,在quartus II 11版中運行了tcl的管腳分配文件,消...

quartus ii 遇到的問題!!!!

Quartus II打開Pin Planner后在管腳分配時有一項Reserved不知道里面列表的含義

Quartus II 下FPGA管腳鎖定

quartus ii使用教程,中文教程

Quartus II 中文教程

Quartus II中管腳上拉電阻應(yīng)該如何設(shè)置

一文詳解Quartus II自動添加管腳分配的方法

一文詳解Quartus II自動添加管腳分配的方法

評論