大家好,又到了每日學習的時間了,今天我們來聊一聊英特爾 Altera系列 cyclone V HPS GIC.

一、CYCLONE V GIC配置

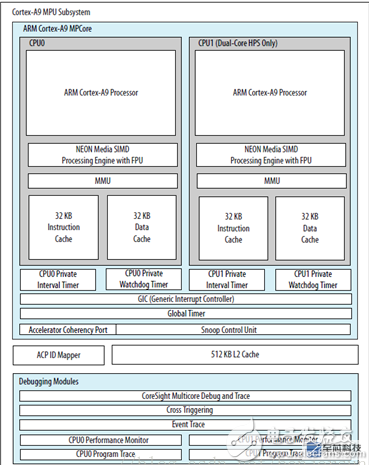

Cyclone v使用雙核ARM CORTEX A9硬核處理器,MPU系統框圖如下:

由上面圖可以看出,雙核CORTEXA9共同使用一個GIC,pl390。PL390實現了180個中斷源,包括了專用的FPGA中斷。每個核都有16個一組的軟件中斷(SGI)及16個一組的私有中斷(PPI)。這32個中斷占用了GIC的0-31中斷號,也稱為interrupt ID。但是這32個中斷采用了中斷與寄存器分區抽像。關于這個中斷與寄存器分區,后面講講。具體的中斷映射,請參照cyclone v HPS手冊。

PL390負責收集所有的中斷信號,并對這些中斷信號進行管理,包括中斷行為,中斷路由及安全擴展等。具體如下:

l ARM安全擴展,這部分內容需要了解ARM TRUSTZONE技術。

l 使能,關閉及生成外圍中斷。

l 生成軟件中斷。

l 中斷門限及優先級設置。

l 多處理器環境中的路由。

PL330支持三種中斷類型,PPI,SPI,SGI。

l PPI中斷為CPU核私有中斷,只連接到指定CPU核。

l SPI由PL330路由到相應的CPU核。

l SGI由軟件編程PL330直接生成,用與核間通信。

PL390支持兩中中斷模型:

l 1:N:只讓一個CPU核處理中斷。軟件通過系統編程GIC實現中斷路由,讓指定CPU核處理該中斷。

l N:N:每個處理器都會收到中斷,它們獨立處理這些中斷。這種方式在SGI上使用,用于CPU核間通信。

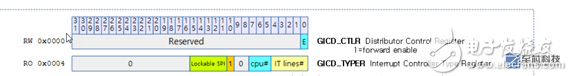

二、MPU GIC

PL390提供一個AMBA總線接口給SOC系統訪問其內部寄存器,可以進行可尋址配置及訪問,同時還可以提供最多8個CPU接口,也就是說可以最多為8個CPU提供中斷服務。

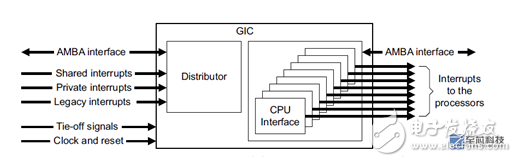

整個GIC被分成兩個部分,distributor(中斷分配器)與多個CPU接口。再看下面一張圖。

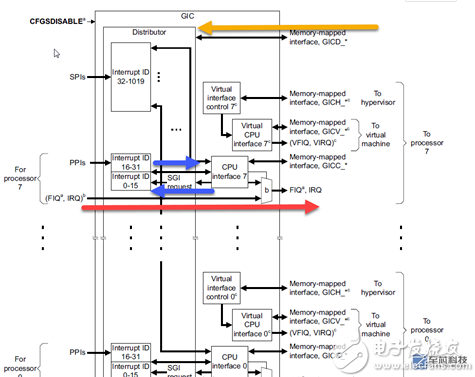

這張圖中,紅色箭頭直接穿過distributor,分配到FIQ與IRQ,這就是bypass模式,也稱為旁路模式,這種模式下,所有中斷被直接分配到了相應的CPU核。而橙色箭頭方向表示GIC提供了一個AXI接口,可以用于訪問distributor,對GIC進行配置。藍色表示軟件可以通過CPU接口直接編程GIC,產生中斷,該中斷具有廣播性質。

通用GIC系統框圖如下所示:

由上圖可以看到GIC明顯分成了Distributor與cpu接口兩部分。所有的中斷都經過Distributor,SGI中斷只是能edge觸發。

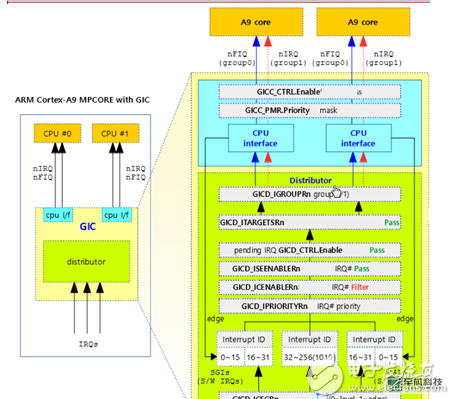

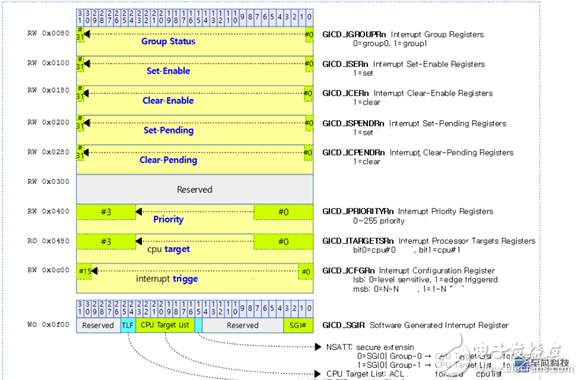

三、GIC編程模型

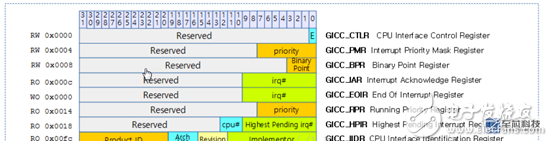

CPU接口寄存器如下圖所示,在CYCLONE V中的偏移地址是0xfffec000。

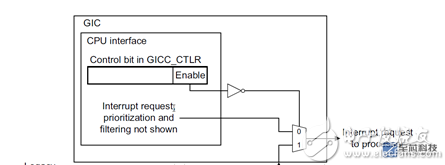

GICC_CTRL(CPU接口控制寄存器)

Enable= 1來轉發中斷。

中斷優先級屏蔽寄存器(GICC_PMR)

用來設置一個優先級,低于該優先級的中斷不會送到CPU。如果設置成0,那就意味著所有中斷都屏蔽了,都不會送到ARM核。

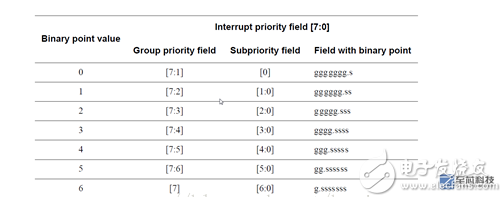

GICC_BPR(二進制點寄存器)

優先級值被分成組優先級與子優先級,跟IP地址掩碼相似。這樣設置后,有相同組優先級的中斷被認為有相同的等級。這樣就分成兩種情況,如果一個中斷要搶占一個正在活動的中斷,那么該中斷必須有一個比活動中斷小的優先級。如果沒有活動中斷情況下,相同組的中斷比較子優先級,產生一個。

GICC_IAR(中斷確認寄存器)

當接收到中斷時,讀取該寄存器并讀取中斷ID及SGI中產生中斷的CPUID,通知gic中斷處理程序已被確認。

中斷結束寄存器(GICC_EOIR)

當中斷服務程序(ISR)中的中斷處理完成時,記錄相應的中斷ID,并通知gic已執行eoi處理。寫該寄存器通過GIC中斷處理完畢。

-

英特爾

+關注

關注

61文章

10007瀏覽量

172335 -

Altera

+關注

關注

37文章

787瀏覽量

154171

發布評論請先 登錄

相關推薦

測試芯片出爐 Altera/英特爾搶得14nm頭籌

英特爾CEO親自上陣解讀重金收購Altera背后原因

為物聯網帶來驚喜 英特爾推出Cyclone10 FPGA系列

英特爾Altera系列cyclone V HPS GIC

英特爾Altera系列cyclone V HPS GIC

評論