FPGA技術的快速發展與VHDL(VeryhighspeedintegratedcircuitHardwareDescriptionLanguage)硬件描述語言的支持,使得智能控制策略(模糊邏輯、神經網絡、遺傳算法等)的VHDL描述和FPGA固核實現研究也隨之活躍。在模糊邏輯控制方面,Torralba等人完成了4輸入、12個隸屬度、64條規則的模糊邏輯控制器的FPGA實現,Cirstea等人基于FPGA設計模糊控制器。本文主要詳解基于FPGA的模糊PID控制器的設計實現,首先介紹了FPGA工作原理、基本特點以及FPGA的優勢,其次闡述了使用Altera的FPGA設計實現的數字模糊PID控制器,具體的跟隨小編一起來了解一下。

FPGA工作原理

FPGA采用了邏輯單元陣列LCA這樣一個概念,內部包括可配置邏輯模塊CLB、輸出輸入模塊IOB和內部連線三個部分。FPGA利用小型查找表(16&TImes;1RAM)來實現組合邏輯,每個查找表連接到一個D觸發器的輸入端,觸發器再來驅動其他邏輯電路或驅動I/O,由此構成了即可實現組合邏輯功能又可實現時序邏輯功能的基本邏輯單元模塊,這些模塊間利用金屬連線互相連接或連接到I/O模塊。FPGA的邏輯是通過向內部靜態存儲單元加載編程數據來實現的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯接方式,并最終決定了FPGA所能實現的功能, 加電時,FPGA芯片將EPROM中數據讀入片內編程RAM中,配置完成后,FPGA進入工作狀態。掉電后,FPGA恢復成白片,內部邏輯關系消失,因此,FPGA能夠反復使用。FPGA的編程無須專用的FPGA編程器,只須用通用的EPROM、PROM編程器即可。當需要修改FPGA功能時,只需換一片EPROM即可。這樣,同一片FPGA,不同的編程數據,可以產生不同的電路功能。FPGA是由存放在片內RAM中的程序來設置其工作狀態的,因此,工作時需要對片內的RAM進行編程。用戶可以根據不同的配置模式,采用不同的編程方式。

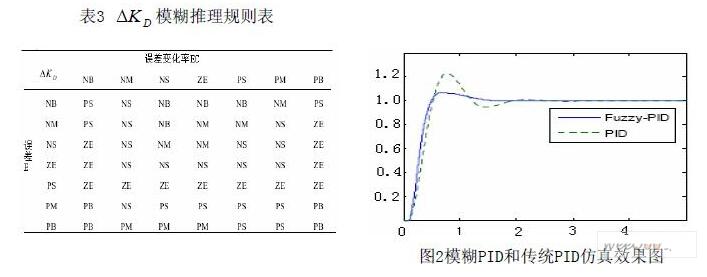

FPGA的基本特點

1)采用FPGA設計ASIC電路(專用集成電路),用戶不需要投片生產,就能得到合用的芯片。

2)FPGA可做其它全定制或半定制ASIC電路的中試樣片。

3)FPGA內部有豐富的觸發器和I/O引腳。

4)FPGA是ASIC電路中設計周期最短、開發費用最低、風險最小的器件之一。

5) FPGA采用高速CMOS工藝,功耗低,可以與CMOS、TTL電平兼容。

FPGA的優勢

優勢一:

更大的并行度。這個主要是通過并發和流水兩種技術實現。

A:并發是指重復分配計算資源,使得多個模塊之間可以同時獨立進行計算。這一點與現在的多核和SIMD技術相似。但相對與SIMD技術,FPGA的并發可以在不同邏輯功能之間進行,而不局限于同時執行相同的功能。舉個簡單例子說就是使用SIMD 可以同時執行多個加法,而FPGA可以同時執行多個加法和乘法和任何你能設計出來的邏輯。

B:流水是通過將任務分段,段與段之間同時執行。其實這一點和CPU相似,只是CPU是指令間的流水而FPGA是任務間流水或者可以說是線程間流水。

優勢二:

可定制。FPGA 內部通過Lookup Table實現邏輯,可以簡單理解為是硬件電路。可定制指的是在資源允許范圍內,用戶可實現自己的邏輯電路。通常情況下任務在硬件電路上跑是比在軟件上快的,比如要比較一個64位數高32位和低32位的大小,在CPU下需要2條區數指令,兩條位與指令,一條移位指令一條比較指令和一條寫回指令,而在FPGA下只要一個比較器就行了。

優勢三:

可重構。可重構指的是FPGA內部的邏輯可根據需求改變,減少開發成本。同時,使用FPGA復用資源比使用多個固定的ASIC模塊為服務器省下更多的空間

基于FPGA的模糊PID控制器的設計實現

一、控制器原理

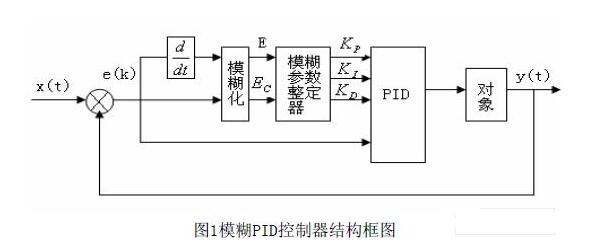

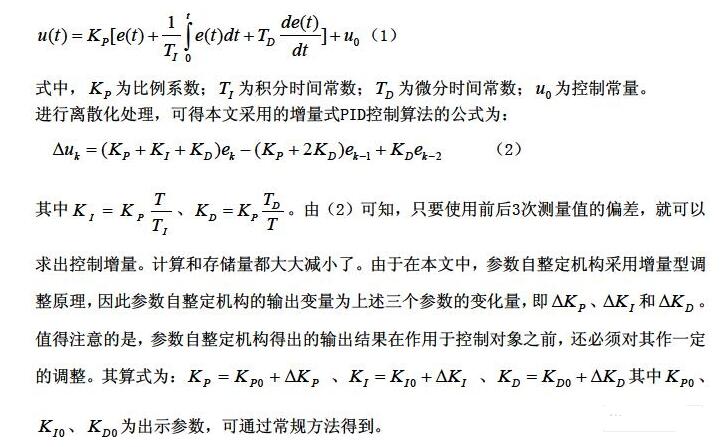

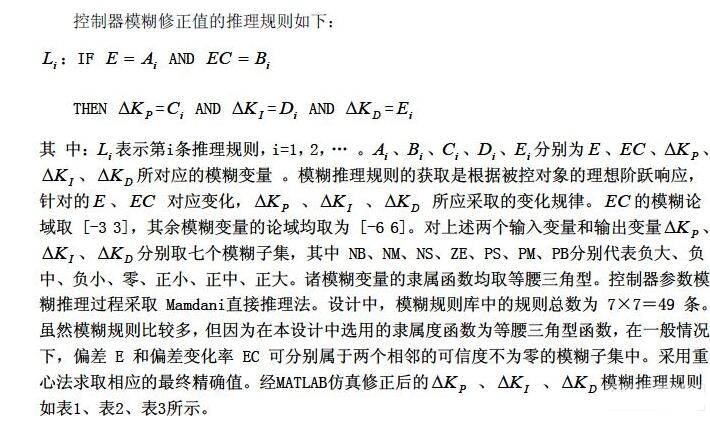

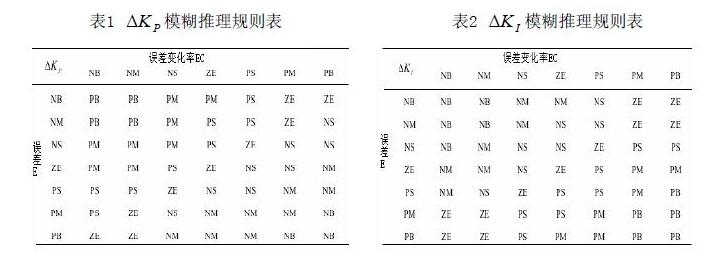

模糊自整定PID控制器結構:是模糊控制器與傳統PID控制器的結合,利用模糊推理判斷的思想,根據不同的偏差、偏差變化率對PID的參數KP、KI、KD進行在線自整定,傳統PID控制器在獲得新的KP、KI、KD后,對控制對象輸出控制量。由此模糊PID控制器的結構框圖如圖1所示。

二、控制器的VHDL分層設計

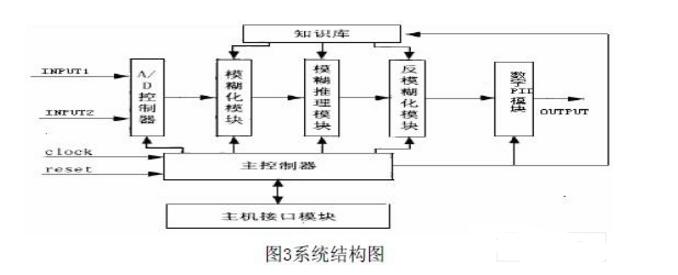

模糊PID控制器主要由A/D控制器、模糊化模塊、模糊推理模塊、反模糊化模塊、規則存儲器、數字PID運算等部分組成,其結構如圖3所示。現就模糊化模塊、模糊推理模塊、反模糊化模塊等主要模塊的建立來描述VHDL的設計過程。

1、模糊化模塊

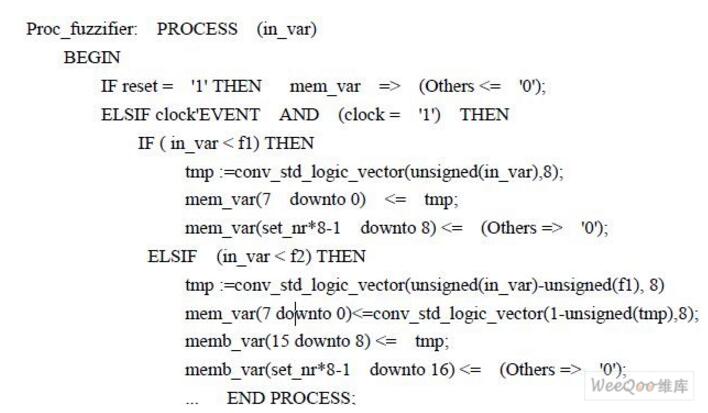

模糊化模塊的功能主要包括兩部分:把輸入的精確量進行尺度變換,變換到相應的論域范圍;將己變換到論域范圍的輸入量進行模糊化處理,主要是計算各個輸入量的隸屬度。由于變量的隸屬度函數均取用等腰三角形,則底邊寬度和底邊中點就可以確定隸屬函數的所有信息。分別用一個字節表示每個語言變量的底邊寬度(實際寬度的一半),用三個位(bit)表示底邊中點位置,將這部分信息存在兩個表中。根據兩個表中的信息,可以計算出輸入變量的隸屬度。為實現隸屬度的計算,需要用到一個加法器,一個減法器和一個除法器。計算的結果肯定是小數(由隸屬度的性質可知)。為了實現方便,將分子的計算結果左移8位。這樣,分子的計算結果是16位,分母是8位,計算結果是8位。對其部分輸入進行模糊化的VHDL描述如下:

2、模糊推理模塊

模糊推理模塊是模糊控制器的核心,它將輸入的模糊量經過推理,變為輸出的模糊量。模糊推理采用Mamdani推理,也稱為Max一Min推理,即最大一最小推理,因為其中主要包括最大化模塊和最小化模塊。對于兩輸入系統,最多輸出四個語言值和四個隸屬度。這樣,對于一個兩輸入系統,最多激活四條模糊規則。上述過程就是規則匹配的過程。規則匹配需要最小化運算,即Min運算。規則合并就是將后件相同的模糊規則進行合并,規則合并需要最大化運算,即Max運算。由模糊化模塊計算所得的四個隸屬函數值在控制信號作用下經過多路選擇器輸入到比較器;另外兩個控制信號經過譯碼后選中隸屬函數寄存器中的一個,同時選擇輸出最小值到比較器;比較器的輸出結果再輸入到隸屬函數寄存器中。這樣,經過4個循環,就完成了一個最小化運算。由于VHDL描述簡單,在這里省略。

3、反模糊化模塊

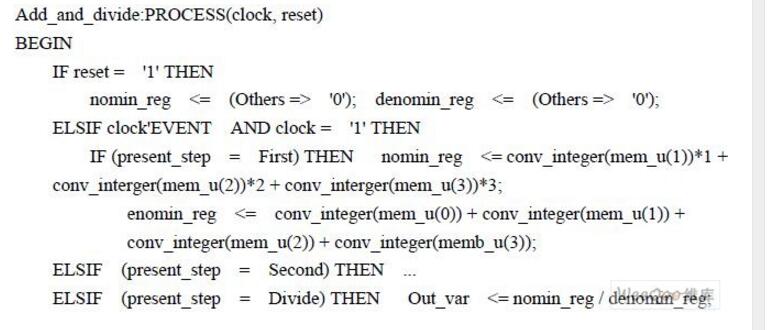

反模糊化通常采用重心法,由于隸屬度函數采用8為二進制表示,而所涉及的規則數最多為4條,所以分子運算需要四個8位x2位的乘法器,3個10位加法器,分母需要3個8位加法器。此外,還需要一個12位/10位的除法器。除法器的設計方法與模糊化模塊中的設計方法相同。而乘法器的設計也與除法器的設計方法相似。相應的VHDL描述如下:

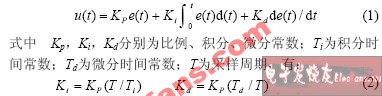

4、數字PID運算模塊

數字PID運算主要是加、減、乘的運算,運用原碼算法設計數字電路無疑增加電路的復雜度。而采用補碼運算進行設計就簡單多了。加減法運算都可以用相同的加法電路來實現。設計乘法電路的方法很多,考慮到節省FPGA器件資源問題,采用BOOTH算法。主要涉及累加器溢出處理和小數運算處理等問題。

三、試驗結果

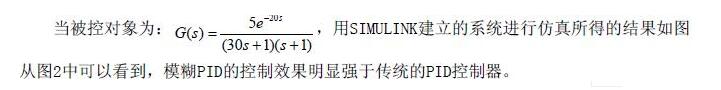

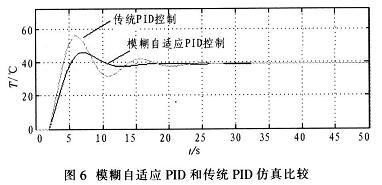

借助MATLAB的模糊控制工具箱提供的FIS編輯器建立mamdani型的模糊控制器,并結合Simulink工具箱建立FuzzyPID控制系統仿真模型。仿真得到的系統階躍響應如圖2。通過圖可以看出Fuzzy-PID控制調節時間短,超調量小,曲線平滑,具有較強的抗干擾和魯棒性。

各模塊程序經過編譯優化之后,由QuartusⅡ軟件綜合并生成網表文件,最后下載到Altera公司的Cyclone系列的EP1C6Q240C8芯片上。經實際測試顯示,該模糊PID控制器控制效果明顯優于普通的PID控制器。

四、結論

本文使用Altera的FPGA設計實現了一個數字模糊PID控制器。其中PID部分采用增量式算法,模糊控制部分采用離線計算、在線查表的方式實現,在不增加硬件資源耗費的前提下大大改善了普通PID控制器的控制效果。同時,FPGA作為單一控制器實現模糊自整定PID控制,編程規范、時序驗證方便、系統修改靈活,且基本無須改動硬件,是實現單片或小系統智能控制策略的一種新的有效途徑。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605998 -

PID控制器

+關注

關注

2文章

173瀏覽量

18671

發布評論請先 登錄

相關推薦

基于FPGA的溫度模糊自適應PID控制器的設計

基于FPGA的模糊PID控制器的設計實現

基于FPGA的模糊PID控制器的設計實現

評論