0 引言

發射機是主動聲納或水下通信設備的重要組成部分,由信號發生器、功率放大器、匹配網絡和發射換能器組成。為了達到預期的聲源級和發射指向性,幾十路甚至上百路換能器構成陣列,相控發射。相控陣發射機電子部分包含多個功率放大器,設備龐大復雜,系統可靠性受到限制。功率放大器是聲納發射機的核心設備,一般采用效率高、體積小的D類放大器,該放大器廣泛用于音響、工業控制等領域。

在發射機整體設計方面,江磊等人利用音頻功率放大器設計了小型水聲發射機,整機體積縮小了50%[1];戴戈等人提出了大功率、小體積且具有信號產生、監控和通信功能的智能寬帶聲納發射機設計方案[2];張纓、周雒維等人對放大器的控制方式進行研究,分別設計了級聯多電平和單周期控制的D類功率放大器[3-4]。

本文研究并設計了全數字化主動聲納發射機,針對常規發射機存在的問題,對發射機的結構進行設計,改進了功率放大器的控制方式,簡化了系統復雜度和調試難度,提高了系統的可靠性,并通過實驗室測試和湖上試驗驗證了發射機的性能。

1 常規主動聲納發射機的結構及分析

常規聲納發射機的信號發生器和功放機柜分離,通過電纜進行連接。信號發生器處于信號處理機柜中,便于與接收機進行收發同步,并與主控計算機通信。信號發生器中DSP根據主控計算機下達的工作參數,讀取存儲器中的波形數據,進行發射波束形成, 然后進行D/A轉換,形成多路模擬信號,通過電纜輸送給功率放大器。除了模擬信號外,電纜中仍需傳輸功放控制信號及功放工作狀態信號。

在艦艇嘈雜的工作環境中,信號容易受到噪聲干擾;模擬信號高達幾十路甚至上百路,模擬信號間、模數信號間容易形成串擾,嚴重影響信號質量。此外,信號處理機柜與功放機柜之間需要粗笨電纜連接,在狹窄的艙室內不容易安裝調試。

信號發生器存儲的數字信號經過D/A轉換,生成的模擬波形與載波進行比較,形成PWM數字信號,驅動功率放大模塊。這個過程增加了系統復雜度,容易引入噪聲干擾,降低了系統的性能和可靠性。

2 全數字式發射機的設計

2.1 發射機總體結構

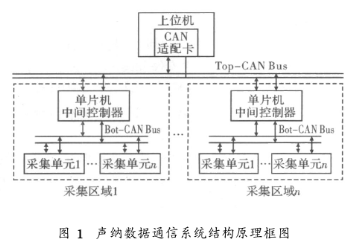

本文設計的全數字式聲納發射機去除了“數字—模擬—數字”的轉換過程,其結構如圖1所示。信號發生器、PWM波形產生、死區控制等功能集成在FPGA中,FPGA使用以太網或RS485等串行通信方式與信號處理機柜交互工作參數和狀態信息,并使用時間同步信號與接收機實現收發同步。這種全數字發射機結構減小了機柜間線纜規模,消除了信號間的干擾,降低了系統復雜度,可提高設備性能和可靠性。

FPGA是功放機柜的核心控制單元,完成了發射波形產生、發射功率控制、發射波束形成、PWM信號產生、死區控制等功能。FPGA內部數據處理流程如圖2所示。

控制指令經過解析后分發給各個模塊,根據指令讀取相應的發射波形進行幅度控制和波束形成,對波束形成后的N路數字信號直接轉換為PWM信號,經過死區控制,生成N對互補PWM波形,輸出后送給H橋的驅動電路。

2.2 發射波束形成的設計

為了實現預期的發射聲源級和指向性,發射機通常進行波束形成,相控陣發射,使各個陣元的信號同時到達目標[5]。

對于一個任意陣列,發射波束指向為a時(a為單位方向向量),各個陣元相對于發射方向a的波陣面有一個延時。為了保證所有陣元的發射信號同時到達該波陣面,每個陣元的信號需要進行延時或移相。

由接收陣列流行矢量得到陣元接收波束形成的延時時間,進一步對接收延時進行規整化處理,得到發射波束形成的延時時間:

FPGA實現可控數字延遲線,使用延時法設計發射波形成系統。由于數字延時的離散性,延時量不能做到連續變化,只能是采樣周期的整數倍,實際延時時間與理論值將會有一定誤差,誤差為:

其中,TS為采樣周期;k=round(τi/TS),round( )表示四舍五入取整,則-TS/2<Δτi

對于全數字D類功放控制器,數字波形生成PWM信號有脈沖密度調制、均勻脈沖寬度調制等多種方法[7]。本文采用UPWM的方式生成PWM信號[8],與傳統的D類功放控制器相比,該方法集成度更高,抗干擾能力強,避免了D/A轉換過程。

FPGA生成PWM波形的流程如圖3所示。發射信號經過幅度偏移后與L進制計數器進行比較,得到PWM波形。發射波形幅度為-A/2~A/2,得到的PWM波形最小脈寬為(L-A)TC/2,TC為計數器時鐘周期,則PWM信號最小占空比為(L-A)/(2L)。

D類放大器一般采用半橋或全橋結構,同一橋臂兩個開關管的驅動信號呈互補結構,為了防止開關管發生直通現象,互補的兩個驅動信號應存在一定的死區時間。死區時間的設置方法有多種[9],本文在FPGA內部實現死區時間控制,產生互補的兩路驅動信號。

FPGA設置死區時間的電路結構如圖4(a)所示,CLK為時鐘信號,PWM為CLK時鐘下產生的數字波形,CTRL調整死區時間的控制字,PQ1和PQ2為互補的兩路PWM信號。調試過程中,可以在線調整D觸發器的數量,控制死區時間的長度;圖4(b)顯示了電路中各節點波形的關系,其中死區時間τD可以在線調整,調整精度為一個時鐘周期。

利用Xilinx公司Spartan-6系列FPGA實現數字發射機的控制器,發射信號中心頻率為5 kHz,采樣頻率50 kHz,生成PWM的時鐘頻率為200 MHz,計數器最大計數值為4 000,數字信號幅度為-1 600~1 600,則生成PWM的占空比范圍為10%~90%。通過在線調試軟件Chipscope獲取FPGA內部運行數據,用MATLAB軟件進行離線分析,結果如圖5所示。

從圖5可以看出,數字波形與鋸齒波載波信號比較后可以生成占空比隨信號幅度變化的PWM波形PQ1,經過死區控制電路,可以產生與PQ1互補的功放驅動信號PQ2。

為了驗證全數字聲納發射機的發射指向性,2014年12月在新安江水庫組織湖上試驗。發射陣列為24陣元的圓柱陣,重復發射脈沖信號,同時緩慢勻速轉動。接收水聽器與發射陣列相距15 m, 采集數據傳輸到工控計算機進行處理,實驗裝置如圖6所示。

測量發射機全向發射時的不均勻性和單波束定向發射時的波束圖,結果如圖7所示。

由圖7可以看出:全向發射時,全數字發射機的全向發射不均勻性為0.89 dB;定向發射時,發射機的波束寬度約為14.2°,主旁瓣比為12.4 dB,滿足設計要求。

本文針對常規發射機存在的問題,對發射機結構進行重新設計,對功率放大器的控制方式進行改進,設計了全數字主動聲納發射機。發射機將信號發生器、發射波束形成、PWM波形產生、死區控制等功能集中在FPGA完成,通過串行通信方式與控制計算機交互控制指令和工作狀態信息。全數字發射機機構減小了機柜間線纜規模,降低了系統復雜度,提高了設備可靠性。經過實驗室測試和湖上試驗驗證,設計的發射機性能可靠,指標滿足設計需求。

2.3 PWM的生成

2.4 死區控制

3 測試與驗證

3.1 功放控制信號的測試

3.2 全數字發射機指向性的驗證

4 結論

-

發射機

+關注

關注

7文章

507瀏覽量

48151 -

聲納

+關注

關注

0文章

14瀏覽量

12466

發布評論請先 登錄

相關推薦

數字式聲納的機動目標跟蹤的算法及實現

實驗用雷達發射機的系統設計

關于數字式主動聲納發射機的研究與設計

關于數字式主動聲納發射機的研究與設計

評論