4位二進制加法器原理

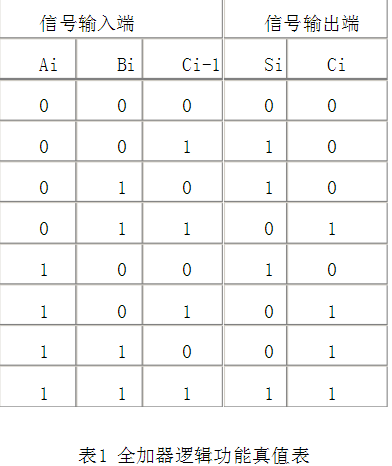

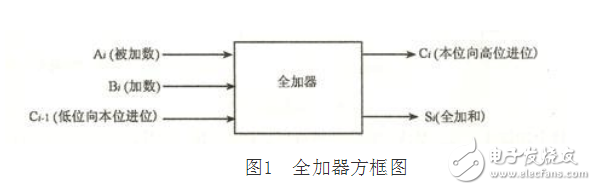

除本位兩個數相加外,還要加上從低位來的進位數,稱為全加器。圖1為全加器的方框圖。圖2全加器原理圖。被加數Ai、加數Bi從低位向本位進位Ci-1作為電路的輸入,全加和Si與向高位的進位Ci作為電路的輸出。能實現全加運算功能的電路稱為全加電路。全加器的邏輯功能真值表如表1中所列。

4位二進制加法器設計

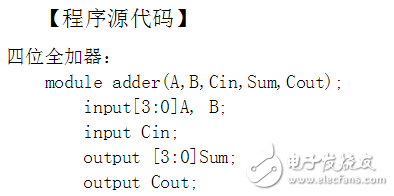

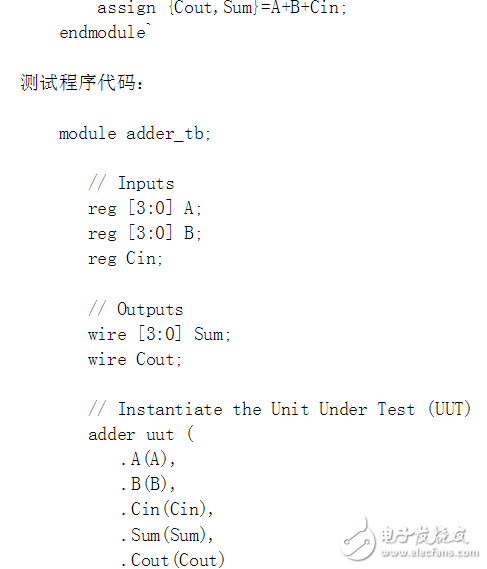

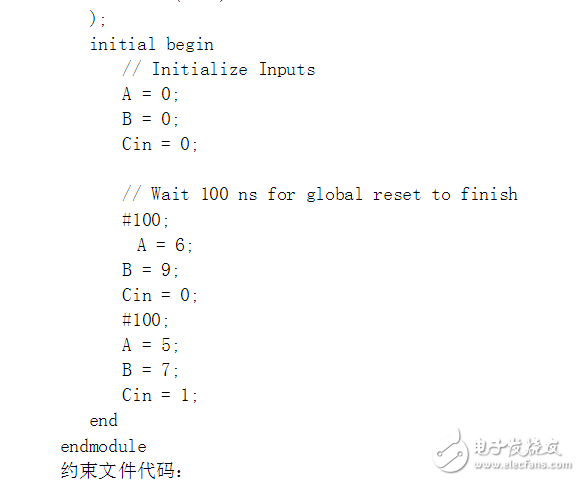

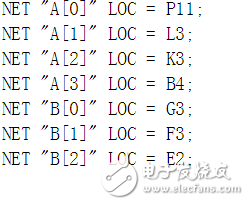

四位全加器

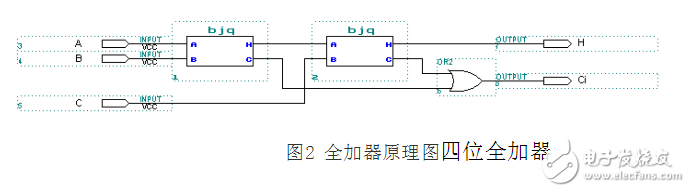

如圖所示,四位全加器是由半加器和一位全加器組建而成:

下圖為四位全加器仿真圖:

由仿真圖可知電路正確。?

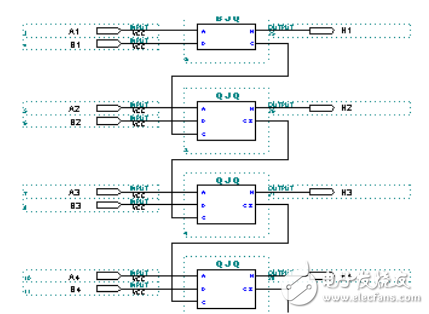

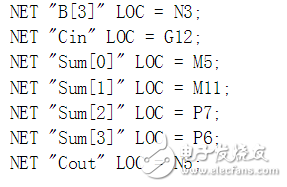

下圖為內部電路模塊圖:

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

加法器

+關注

關注

6文章

183瀏覽量

30230 -

二進制加法器

+關注

關注

0文章

3瀏覽量

3294

發布評論請先 登錄

相關推薦

加法器工作原理_加法器邏輯電路圖

。在電子學中,加法器是一種數位電路,其可進行數字的加法計算。三碼,主要的加法器是以二進制作運算。由于負數可用二的補數來表示,所以加減器也就不

發表于 02-18 14:40

?3.3w次閱讀

串行加法器和并行加法器的區別?

串行加法器和并行加法器是兩種基本的數字電路設計,用于執行二進制數的加法運算。它們在設計哲學、性能特點以及應用場景上有著明顯的區別。

4位二進制加法器原理 4位二進制加法器設計

4位二進制加法器原理 4位二進制加法器設計

評論