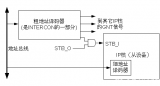

地址不變突發是一個總線周期,在這個總線周期中完成多次操作,但是地址不變。地址不變突發的典型應用是以DMA方式讀/寫FIFO。主設備在時鐘的某一個上升沿將CTI()置為3’b001后,下一個周期的操作必須與本周期,包括SEL_O()信號也不能改變,即在地址不變突發中的每一次操作除傳輸的數據可能發生變化外其他都是相同的。

圖27 Wishbone總線的地址不變突發示例

圖27給出了一個地址不變突發寫總線周期示例。圖中主設備和從設備一共進行了4次操作。

在時鐘上升沿0,主設備將地址信號ADR_O()放到總線上,將數據信號DAT_O()、TGD_O()放到總線上,將WE_O置為高表示寫操作,將CTI_O()置為3’b001表示地址不變突發總線周期,將適當的SEL_O()信號置高通知從設備將數據總線上哪些信號是有效的,將CYC_O和TGC_O置高表示操作正在進行,將STB_O置高表示第一次寫操作開始。

在時鐘上升沿1,從設備檢測到主設備的寫操作,將DAT_I()采樣,并置高ACK_O。

在時鐘上升沿2,主設備檢測到ACK_I為高,知道第一次傳輸順利完成,由于數據沒有準備好,于是將STB_O置低表示插入等待周期。

在等待周期,從設備知道地址不變突發寫操作仍然在進行,因此一直將ACK_O置高。但是此時主設備和從設備知道沒有真正的傳輸發生。

在時鐘上升沿3,主設備已經將新的數據準備好,于是將STB_O置高表示第二次寫操作開始,并更新DAT_O()。

在時鐘上升沿4,從設備檢測到主設備的寫操作,將DAT_I()采樣。同時從設備發現沒有足夠的空間存儲數據或者由于其他原因不能及時接收新的數據,于是將ACK_O置低插入等待周期。主設備檢測到ACK_I為高,于是發起第三次操作,更新DAT_O()。

在時鐘上升沿5,從設備發現可以繼續接收數據,于是將DAT_I()采樣并將ACK_O置高。

在時鐘上升沿6,主設備檢測到ACK_I為高,于是發起第四次操作,更新DAT_O(),同時將CTI_O置為3’b111表示本次操作為最后一次操作。

在時鐘上升沿7,從設備將DAT_I()采樣,并根據CTI_O為3’b111知道本次地址不變突發寫操作完成,于是將ACK_O置低。

-

時鐘

+關注

關注

11文章

1746瀏覽量

131799 -

總線

+關注

關注

10文章

2903瀏覽量

88392 -

Wishbone

+關注

關注

0文章

16瀏覽量

10443

原文標題:【博文連載】Wishbone總線地址不變突發結束方式

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

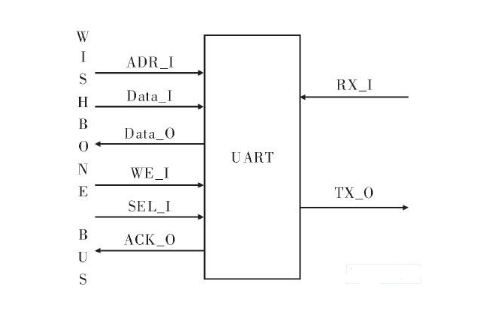

wishbone總線

基于WISHBONE總線的FLASH閃存接口設計

基于Wishbone片上總線的IP核的互聯

基于Wishbone總線的UART IP核設計

基于WISHBONE總線的FLASH閃存接口設計

基于WISHBONE總線的通用接口控制器

Wishbone總線實現UART IP核設計

基于FPGA的SDX總線與Wishbone總線接口設計

Wishbone一般總線規范的共同特點

Wishbone總線的突發結束

Wishbone總線的主要特征概括

Wishbone II交易總線:速度的另一個等級

Wishbone總線的地址不變突發示例

Wishbone總線的地址不變突發示例

評論