1 引言

雷達信號模擬技術根據信號注入點不同分為射頻信號模擬、中頻信號模擬、視頻信號模擬。信號注入點位置越靠前,模擬越復雜,越接近現實;信號注入點位置越靠后,模擬越容易,逼真程度越低。因此應根據實際需求選擇不同的模擬方法。目前,視頻信號模擬器多采用PC機+DSP組合架構。PC機離線產生所需的雜波、噪聲等數據,模擬器工作時,通過PCI接口或USB接口,將預先產生的數據由PC機實時傳輸至硬件電路指定的存儲空間。DSP調用相關數據,經實時運算生成視頻數據并存入輸出緩存,最終在同步信號的觸發下,經D/A轉換,生成視頻信號。

單片容量為4 G字節的Flash存儲器可為存儲雷達視頻模擬過程中所需的大量背景雜波數據提供了硬件基礎,而且Flash峰值讀寫速度達到40 M字節,能夠滿足大多數視頻模擬數據的吞吐量要求。這里的視頻信號模擬器正是基于這一條件設計的,整個系統使用PC機+DSP組合架構,但在視頻模擬過程中不再從PC機實時傳輸數據至硬件存儲單元,而是在生成視頻信號前,將預先產生的大量雜波、噪聲數據下載至硬件電路的Flash存儲器中,并在生成視頻信號的過程中,從Flash中讀取雜波、噪聲及目標參數。然后經DSP運算產生視頻數據,最終經D/A轉換器生成視頻信號。

這里提出的視頻回波模擬器可模擬某型導引頭雷達系統中的輸出、生成和差3個通道共6路視頻信號,用來調試對應的雷達信號處理器。

2 系統結構

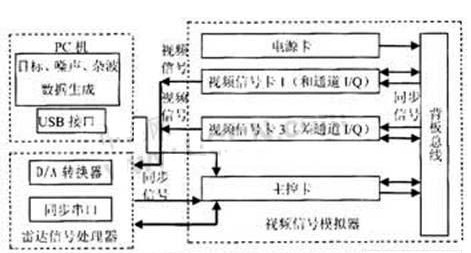

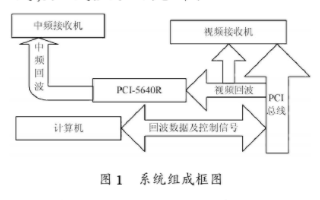

該模擬器采用板卡式結構,由一塊主控卡、三塊視頻信號卡(每塊信號卡兩路,包括和差、俯仰及方位I,Q共6路信號)和一塊高速背板總線組成。主控卡與PC機通過USB接口通信,并通過同步串口與信號處理器通信,另外將信號處理器的PRT同步信號、搜索/跟蹤等同步信號接入背板總線。視頻信號卡根據上位機生成的雜波數據目標參數、航跡數據。生成視頻信號。為保證各路信號的一致性,所有視頻信號卡采用相同的PCB設計;整個背板總線包含并行總線和LVDS總線兩部分。前者用于傳遞同步信號及各卡的電源,后者作為命令、地址及數據傳輸路徑。圖1給出該模擬器的硬件框圖及其與雷達信號處理器的連接。電源卡用于給整個系統供電。

2.1主控卡

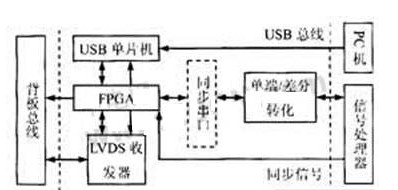

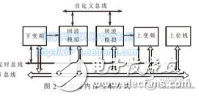

圖2給出主控卡的原理框圖。該卡以FPCA為中心控制單元,使用USB接口器件與上位機通信。FPGA控制USB單片機及LVDS收發器將上位機指令、地址及數據通過背板總線傳輸至視頻信號卡。另外,FPGA在其內部開辟緩存空間,通過USB接收上位機發送信號處理器的指令,通過同步串口將其轉為差分信號并發送至信號處理器。另外,信號處理器反饋至其相應的狀態信息,通過FPGA控制USB單片機上傳至上位機,實時顯示。

2.2背板總線

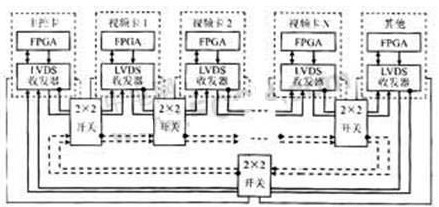

該系統需產生和差三通道I,Q共6路回波信號,而每路信號都需將對應的雜波、噪聲及目標參數下載到Flash存儲器中。由于數據量較大,且考慮到下載速度,該背板總線采用了自行設計的單環總線結構。該結構采用基于低壓差分信號收發器DS92LV18和低壓差分信號傳輸模擬交叉點開關SCAN90 CP02來實現。通過各子卡的插拔,實現對SCAN90 CP02的邏輯控制,從而保證無論背板各擴展槽是否有卡,整個環路都保持封閉狀態。DS92LV18的主要性能:15~66 MHz,18:1/1:18串行/解串器;收發一體設計;內置發射/接收數字鎖相環;提供幀同步、幀檢測、時鐘恢復功能;可進行單器件環路測試,器件引腳基本兼容,設有本地及線路環回模式。SCAN90CP02的特點:每通道的傳輸速率達1.5 Gb/s;低功耗;在雙中繼器模式下,最高速率時,電流為70 mA;低輸出抖動;配置有預增強功能,可驅動有損耗的背板和電纜LVDS/BLVDS/CML/LVPECL輸入;LVDS輸出。由這兩款器件組成的環網總線最大數據喬吐速度為1.188 Gb/s,能夠滿足快速下載數據的要求。圖3給出單環總線的結構原理框圖。

2.3視頻信號卡

視頻信號卡為整個系統的核心部分,因其視頻信號的生成所涉及的運算量很大,單個DSP難以生成多路視頻信號,同時出于系統升級的考慮,因此該視頻信號模擬器的每路都使用高性能的TMS320C6713型浮點數字信號處理器。該DSP采用先進的超長指令字結構,內置8個獨立的功能單元、2個定點算術邏輯單元,2個浮點乘法器,4個浮點ALU、32個32位通用目的寄存器,4 K字節的L1高速程序緩存區,4 K字節的L1高速數據緩存器,256 K字節的L2兩級數據緩存器。這種結構能最大限度地發揮8個功能單元的并行計算能力,使得300 MHz系統時鐘工作下的DSP性能達到2400MI/s和1 800MFLO/s。

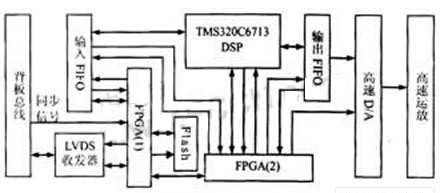

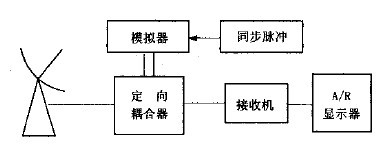

單路視頻信號生成原理框圖如圖4所示。其中,DSP完成視頻信號運算;FPGA(1)用于控制LVDS收發器接收來自總線上的命令、地址及數據,在產生視頻信號前,將上位機事先產生的雜波數據、噪聲及目標參數下載至Flash存儲器中。在生成視頻信號期間,FPGA(1)判斷DSP的工作狀態,將Flash存儲器的數據讀入輸入FIFO中;FPGA(2)主要完成DSP瀆寫輸入、輸出FIFO的邏輯轉換,接收來自DSP計算視頻信號相對PRF信號的延遲時間,通過FPGA(1)接收同步信號,讀取輸出FIFO的數據并啟動D/A轉換器;DSP將輸入FIFO的數據瀆人其內部RAM,根據對應的數據及目標參數生成所需的視頻信號數據,并將運算后的數據寫入輸出FIFO。FIFO采用IDT72V17160,其讀寫速度可達100 MHz。

3系統工作流程

上位機根據噪聲和雜波模型脫機產生和路、方位差、俯仰差三通道I/O雜波、噪聲及目標參數,由上位機發出指令、卡地址將各通道的數據下載至對應的Flash存儲器。然后,由上位機生成DSP指令,發送至主控卡的緩存中,觸發同步信號,將指令發送至DSP,同時視頻卡根據該同步信號產生視頻信號,DSP對視頻信號進行采樣、運算,并將其結果及狀態信息發送至上位機顯示。

3.1數據下載

數據下載即將上位機預先產生的雜波、噪聲數據及目標參數通過背板總線下載到各通道對應的Flash存儲器中,整個發送過程由上位機控制,按表1所示格式將命令、地址、數據的順序發送至主控卡,然后由主控卡FPGA控制LVDS收發器,將命令、地址及數據發送至單環總線上,所有總線節點(視頻卡)接收到命令后,轉為數據下載工作狀態,接著再判斷是否為該節點地址。若是,準備接收數據,并判斷區地址,將數據寫入對應的Flash分區中;若不是,關閉數據通道,等待接收新卡地址。因為Flash存儲器在寫入2 K字節數據后需要一個較長的編程時間,所以在實際數據下載的過程中,使用輪詢寫人方法,即上位機每發送2 K字節數據后,就發送新卡地址,將數據寫入下一通道的Flash存儲器中,依次執行,直到第一通道,Flash存儲器編程結束,再將數據繼續寫入,節約了數據下載時間。

3.2視頻信號的生成

整個視頻信號的生成過程,數據的搬移及信號的運算均由DSP完成,由于TMS320C6713 DSP具有16個EDMA通道,可在不占用CPU運行周期的前提下,實現數據快速搬移,所以該設計在DSP內部開辟一個乒乓緩存區(Ping PangCache),CPU在調用乒乓緩存數據時,EDMA往乒乓緩存中搬移數據后進行交換,這樣可同時執行EDMA數據搬移和CPU信號運算,保證實時生成視頻信號。

當各通道的雜波、噪聲及目標參數下載完成,各通道FPGA(1)接收上位機指令,將存儲在Flash的數據讀入輸入FIFO中,DSP啟動EDMA通道將輸入FIFO數據讀至其內部乒乓緩存中。此時,DSP發出READY信號給FPGA(2),FPGA(2)將PRF同步信號接入DSP的外部中斷引腳,這樣當下一個PRF同步信號到來時,觸發DSP的外部中斷,DSP執行內部的波形運算程序,并啟動EDMA通道將雜波等數據搬移至乒乓緩存,運算結束后,DSP將目標出現的延時發給FPGA(2),并將運算完畢的波形數據搬移至輸出FIFO。FPGA(2)收到延遲后,在下一個PRF同步信號到來時,計數DSP接收時間,計數結束,從輸出FIFO讀取運算完畢的數據,同時啟動D/A轉換器進行數據轉換。

3.3性能改進

雖然系統性能能夠滿足實際應用需求,但對某些環節稍作改進,會使整個系統功能進一步增強。對于DSP而言,同步FIFO為異步存儲器,所以DSP在讀寫FIFO時設置為異步方式,讀FIFO的頻率僅能達到25 MHz,寫FIFO的頻率僅能達到33 MHz。如果將DSP讀寫SDRAM時序進行邏輯轉換,可使讀寫FIFO的頻率達到100 MHz,大大增強DSP的數據吞吐能力;另外單路視頻信號的數據僅使用一片Flash存儲器,雖然其峰值讀數速度可達40 M字節,但由于每讀2 K字節后,Flash需占一個緩存時間,這樣其平均讀數速度僅能達到約27 M字節。若將兩片Flash并聯,則達到其峰值速度,提高了系統性能;另外,目前在DSP內部僅在數據輸入端開辟一個乒乓緩存,若在數據輸出端也開辟一個乒乓緩存,則可將數據搬移和CPU運算進一步并行執行,縮短每個PRF周期的數據處理時間。

4結語

針對具體的雷達信號處理器,提出一種視頻信號模擬器的硬件設計,模擬器采用PC機+DSP組合架構,整個系統采用插卡式結構,各路視頻信號的生成使用相似的硬件電路,由PC機產生所需的雜波、噪聲數據及目標參數,并事先將生成的各路視頻信號所需的雜波、噪聲及目標參數通過自行設計的自適應單環總線下載到對應的大容量Flash存儲器中,數據下載完畢后,經由DSP組合實時運算,在每個PRF同步信號的觸發下輸出視頻模擬信號。由于Flash存儲器為非易失性存儲器,具有掉電后數據不丟失的優點,所以如果雜波、噪聲及目標參數不改變的情況下,數據只需下載一次。另外,使用文中提出的環網總線結構,可保證數據的快速下載。

-

存儲器

+關注

關注

38文章

7528瀏覽量

164342 -

PC

+關注

關注

9文章

2102瀏覽量

154661 -

雷達

+關注

關注

50文章

2966瀏覽量

118017 -

模擬器

+關注

關注

2文章

881瀏覽量

43419

發布評論請先 登錄

相關推薦

基于LabVIEW軟件和PCl-5640R數據卡實現和雷達回波模擬器的設計

基于CPCI接口DSP板的雷達目標模擬器

基于DSP+FPGA的雷達信號模擬器系統設計

一種自主產生式的雷達回波模擬器中頻部分的設計實現方法論述

一種自主產生式的雷達回波模擬器中頻部分的設計論述

雷達回波模擬器的設計方法是什么?

一種雷達回波信號模擬器的設計與實現

雷達回波模擬器中頻部分的實現

基于DSP和FPGA的多波形雷達回波中頻模擬器實現

插卡式電表有哪些優勢

如何實現雷達回波模擬電路的設計

采用插卡式結構實現雷達視頻回波模擬器系統的設計

采用插卡式結構實現雷達視頻回波模擬器系統的設計

評論