目前,顯示屏按數據的傳輸方式主要有兩類:一類是采用與計算機顯示同一內容的實時視頻屏;另一類為通過USB、以太網等通信手段把顯示內容發給顯示屏的獨立視頻源顯示屏,若采用無線通信方式,還可以隨時更新顯示內容,靈活性高。此外,用一套嵌入式系統取代計算機來提供視頻源,既可以降低成本,又具有很高的可行性和靈活性,易于工程施工。因此,獨立視頻源LED顯示系統的需求越來越大。

本系統采用ARM+FPGA的架構,充分利用了ARM的超強處理能力和豐富的接口,實現真正的網絡遠程操作,因此不僅可以作為一般的LED顯示屏控制器,更可以將各顯示節點組成大型的戶外廣告傳媒網絡。而FPGA是一種非常靈活的可編程邏輯器件,可以像軟件一樣編程來配置,從而可以實時地進行靈活而方便的更改和開發,提高了系統效率。

1 獨立視頻LED系統

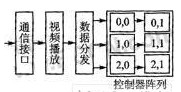

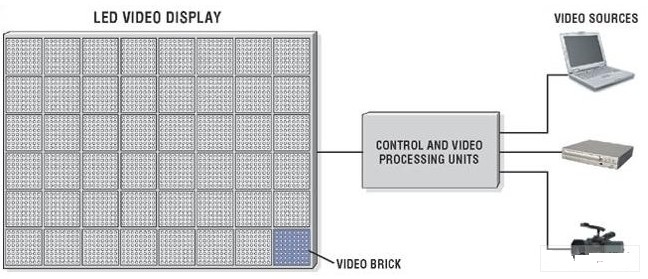

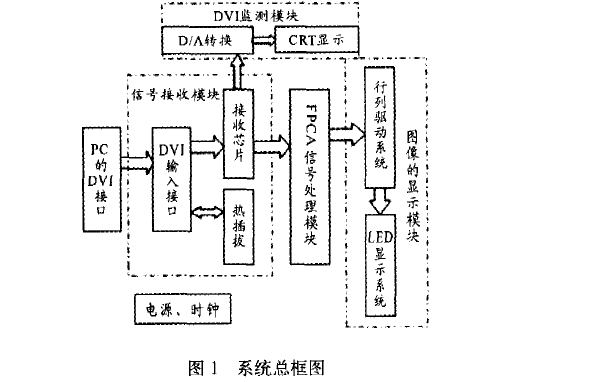

LED顯示屏的主要性能指標有場掃描頻率、分辨率、灰度級和亮度等。分辨率指的是控制器能控制的LED管的數量,灰度級是對顏色的分辨率,而亮度高則要求每個灰度級的顯示時間長。顯然,這3個指標都會使得場掃描頻率大幅度降低,因此需要在不同的場合對這些指標進行適當的取舍。通常灰度級、亮度和場掃描頻率由單個控制器決定,而分辨率可以通過控制器陣列的方式得到很大的提高。這樣,每個控制器的灰度和亮度很好,場掃描頻率也適當,再通過控制器陣列的形式,實現大的控制面積,即可實現顏色細膩的全彩色超大屏幕的LED顯示控制器。獨立視頻LED系統完全脫離計算機的控制,本身可以實現通信、視頻播放、數據分發、掃描控制等功能。為了實現大屏幕、全彩色、高場頻,本系統采用控制器陣列模式,如圖1所示。

圖1 獨立視頻LED系統結構

系統可以通過網絡接口(以太網接口)由網絡服務器端更新本地的數據,視頻播放部分則通過對該數據進行解碼,獲得RGB格式的視頻流。再通過數據分發單元,將這些數據分別發送到不同的LED顯示控制器上,控制器將播放單元提供的數據顯示到全彩色大屏幕LED上。

2 通信接口和視頻播放單元

本系統的通信接口和視頻播放部分由ARM uClinux實現。ARM (Advanced RISC Machine)是英國ARM公司設計開發的通用32位RISC微處理器體系結構,設計目標是實現微型化、低功耗、高性能的微處理器。Linux作為一種穩定高效的開放源碼式操作系統,在各個領域都得到了廣泛的應用,而uClinux則是專門針對微控制領域而設計的Linux系統,具有可裁減、內核小、完善的網絡接口協議和接口、優秀的文件系統以及豐富的開源資源等優點,正被越來越多的嵌入式系統采納。系統中使用Intel XScale系列的PXA255芯片,與ARM v5TE指令集兼容,沿用了ARM的內存管理、中斷處理等機制,并在此基礎上做了一些擴展,如DMA控制器、LCD控制器等。由于ARM9的處理能力有限,目前只用其播放320×240像素的視頻。

系統視頻播放的數據來自于系統中的SD存儲卡(Secure Digital Memory Card)。更新SD卡的數據有兩種方式:一種是用計算機更新SD卡的數據;另一種是通過網絡接收服務器的數據,直接由ARM更新SD卡。此外,播放器也可以直接播放網絡傳送的MPEG-4格式數據口由于XScale未提供物理層接口,若想實現網絡功能需外接一片物理層芯片。本系統選用SMSC公司的高性能100M以太網控制器LAN9118。

3 視頻數據分發

由于控制器采用陣列模式,因此需要對視頻源提供的數據進行分發,將不同行列的數據正確地送入不同的控制器。

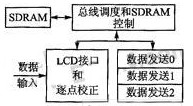

3.1 數據分發單元方案

本系統中的LED控制器灰度級高達3×12位(可顯示多達64G種顏色)、控制區域為128×128點。系統播放單元提供的數據為320×240像素,因此需要分解成6個LED控制器來控制(見圖1)。因此,需要將PXA255提供的RGB數據分3組發送到這6塊控制器,以FPGA實現,方案如圖2所示。

圖2 數據分發單元方案

LCD接口子模塊接收PXA255 LCD接口的數據和控制信號,將這些輸入的數據進行逐點校正之后存入SDRAM,然后將該場數據分成3 組,每組128行(最后一組只有64行,為了后面控制板的一致性,此處由總線調度器補零),同時發送,之后由LED顯示控制器處理。

3.2 存儲器分配和總線調度

為了方便各模塊間的接口,有利于不同時鐘域的數據同步,系統的存儲器采用兩級存儲模式,即SDRAM作為主存儲器,而各模塊也有相應FIFO作為Cache, SDRAM具有容量大、帶寬高、價格便宜等優點;但是控制比較復雜,每次讀寫有多個控制和等待周期。因此為了提高效率,通常采用地址遞增的碎發讀寫方式,而不能像SRAM那樣隨時讀取任意地址的數據。

本方案采用完全動態的內存分配機制,即每個模塊請求時,如果不是同一場數據,則可以分配到一塊新的內存,而一旦該內存的數據不再有效,則釋放這塊內存。這樣,每塊內存都有自己的屬性,標志是使用中的內存,還是空閑內存,以及當前內存中的數據是否在等待被使用的隊列中,因此內存需要分成3塊。其中一塊存儲逐點校正參數,一塊存儲當前場數據,另一塊存儲上一場數據(即正在發送的數據)。這就要求在一個場同步周期內需要將數據發送完畢,而這一要求是完全可以達到的。

總線調度是本模塊的核心部分,必須精確計算總線帶寬的占用情況,確定各部分FIFO的深度,以保證各個FIFO不會出現溢出或讀空的現象。

總線調度器需要調度3塊存儲器,還需要為每一個模塊維護一個偏移地址的首地址,以及一個偏移地址計數寄存器。為了便于計算偏移地址,用SDRAM物理上的兩行存儲一行的數據,而將多余部分空余。

總線調度器的仲裁算法為:逐點校正參數與校正后數據寫人SDRAM的優先級一樣,采用先來先得的方式占用總線,分別由各自FIFO的指針來觸發總線占用。一場數據寫入SDRAM完畢之后,開始發送。需要依次讀出第n,n+ 128,n+ 256行的數據給數據發送FIFO0,1,2,等待數據發送單元啟動發送。

3.3 LCD接口和逐點校正

PXA255 的LCD接口配置為smart panel形式,具體時序關系可參考PXA255的手冊。FPGA根據這些時序關系,將數據讀入,進行下一步的處理。

由于在生產過程中LED管的參數不可能完全一致,因此為了獲得良好的圖像顯示效果,必須對LED管進行篩選。這也是LED屏價格昂貴的一個重要原因。

采用逐點校正技術,可逐點調節LED的亮度,將顯示屏亮度的一致性提高一個數量等級,從而可以使采購廠商放寬LED在亮度和顏色方面的要求,LED采購的成本也隨之大大降低。此外,系統采用的逐點校正技術,可以在線修改校正參數,使得LED屏在投入運營之后也可以修改校正參數,補償由于LED管老化對顯示效果的影響,提高LED屏的使用壽命。因此,逐點校正技術使LED模塊作為室內外全彩色顯示屏的基本元件成為理想方案。

逐點校正參數存于SD卡中,在系統上電之后,ARM首先將該數據通過LCD接口(此時配置為GPIO)傳送到FPGA, FPGA將其存入SDRAM 中。此后,即可對LCD接口輸入的數據進行校正。

3.4 數據發送

在數據發送時,每行數據作為1幀,加入特定的幀頭之后開始發送。為了減少總線數量,采用串行總線形式,每組信號共有4路,分別是源同步時鐘和RGB三基色的串行數據。信號均以LVDS(Low Voltage Differential Signal,低電壓差分信號)的形式傳輸。LVDS采用差分方式傳送數據,有比單端傳輸更強的共模噪聲抑制能力,可實現長距離、高速率和低功耗的傳輸。Altera公司的Cyclone II系列FPGA可以方便地通過I/O配置獲得LVDS的能力。

發送幀頭由4字節的同步頭+數據當前行號+ID號組成。由于圖像的連續像素值的相關性比較高,因此使用偽隨機碼作為同步頭,其同步性能比較可靠。當前行號用于控制器判斷是否出現丟幀,并根據當前的行號決定當前數據的存儲地址。由于每一組數據實際上由兩個控制器分別處理(見圖1),所以需要判斷標志來截取不同的數據部分。ID號即是不同控制器截取某行中不同列數的標準,數據在發送時ID為零。

4 全彩色LED顯示控制器

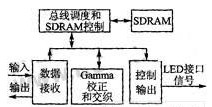

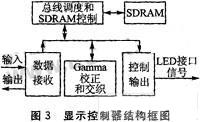

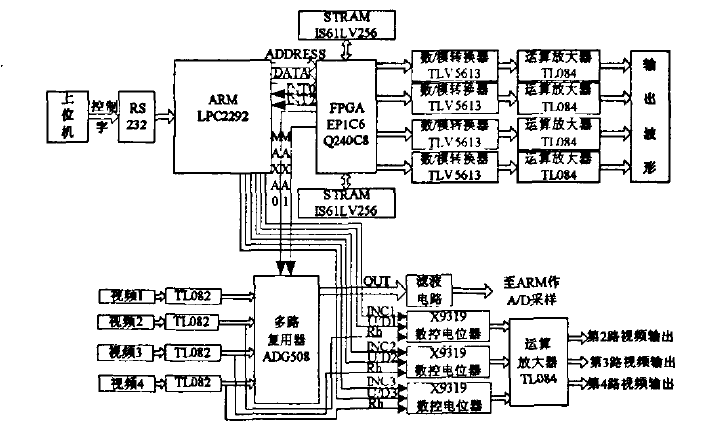

全彩色LED顯示控制器負責接收、轉換和處理串入的RGB三基色信號,以一定的規律和方式將信號傳送到LED顯示屏上顯示。控制器直接決定了顯示屏的顯示效果,也決定了LED顯示屏性能的優劣。控制器的結構如圖3所示。

圖3 顯示控制器結構框圖

控制器的架構與數據分發類似,也采用二級存儲模式,主要有數據接收、Gamma校正和交織、掃描控制輸出以及總線調度和SDRAM控制四部分。

4.1 存儲器分配和總線調度

由于數據輸入場頻與LED掃描場頻通常不能成整數倍關系,可能出現輸入一場數據結束,該場數據的處理結果(Gamma校正和交織后)需要寫入SDRAM,而此時掃描一場沒有結束,即正在讀的那個區域不能覆蓋,而上一場的數據還沒有顯示也不能覆蓋,因此交織地寫入(即掃描的讀出)需要開辟三塊分區。

總線仲裁算法為:控制輸出模塊和寫人模塊采用先來先得的算法,而校正和交織過程的讀寫,則優先級最低,可以在前面二者申請時被掛起,只有當前二者不再需要總線時,才可以分配到總線的使用權。

4.2 數據接收

數據接收單元除了需要同步判決、串并轉換之外,還要確定一行中哪些數據需要本控制器處理。控制器截取每行中第128×ID-128×(ID+1)-1列的數據,同時將ID號加1,其他數據原樣輸出,送給下一級控制器。這樣的控制方法比常用的撥碼開關法更加靈活可靠。

4.3 Gamma校正和交織

Gamma校正可以使LED顯示效果更接近于人眼的生理特性,而且由于PXA255輸出的是8位數據,系統需要將其校正為12位,大大提高了顯示的對比度。由于LED顯示控制器采用逐位顯示的方法,輸入的數據與輸出到LED顯示屏上的數據組織形式不一樣:前者按像素點排列,而后者則按像素數值的不同位數組織。

4.4 控制輸出

12位數據顯示的時間分別為(64,32,16,8,4,2,1,1/2,1/4,1/8,1/16,1/32) * 128 * Tsclk,其中Tsclk為串行移位時鐘。交織之后,不同權重的數據顯示信號顯示有效時間不同,即可達到顯示的效果。

總線調度器將交織后的數據寫入本模塊的FIFO。由模塊內部生成讀取該FIFO的控制信號,并對其進行計數。模塊內需要對移位個數及權重進行計數,以決定發出鎖存信號及顯示信號的有效時間。

5 結論

實驗測試結果表明,該系統亮度合適,使用分辨率細膩(64G色),場掃描頻率高(約400 Hz),像素高(320×240點),可用于戶外廣播級應用。該設計通過逐點調節亮度,從而可以使采購廠商放寬LED在亮度和顏色方面的要求,LED采購的成本也隨之降低,從8位增至12位使圖像的顏色等級大大增加,特別在低亮度區可使圖像完美再現,而Gamma校正則使LED顯示屏所進行的亮度變換更符合人眼的生理特點。此外,除接收來自ARM的信號外,還可通過HDMI接口接收來自機頂盒的數據信號,有廣闊的市場應用前景。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

606003 -

led

+關注

關注

242文章

23355瀏覽量

663188 -

ARM

+關注

關注

134文章

9165瀏覽量

369194 -

計算機

+關注

關注

19文章

7536瀏覽量

88639

發布評論請先 登錄

相關推薦

基于MAX6974 LED驅動器與FPGA芯片的LED視頻顯示板設計

采用AT91M42800A實現LED顯示系統設計

如何利用ARM和FPGA設計全彩獨立視頻LED系統?

介紹幾種基于ARM處理器的純硬件視頻融合拼接系統技術方案

基于ARM和FPGA的全彩獨立視頻LED系統

采用ARM與FPGA芯片實現獨立視頻源LED顯示系統的設計

采用ARM與FPGA芯片實現獨立視頻源LED顯示系統的設計

評論