引言

在系統設計中,設計師們面臨的重要挑戰是既要支持高可靠性(HA,High Availability),又要使系統盡可能簡單、有效。而PCI Express、基于PCI Express的高級交換架構(Advanced SwitchingArchitecture)、基于PCI Express的QOS(Quality-Of-Service)特性以及PCI-Express非透明橋的出現,共同為這樣的系統設計提供了一個非常有發展潛力的解決方案。

1、PCI Express技術簡介

PCI Express技術是一個比較新的互連標準。該技術適用于高性能的芯片到芯片、板子到板子、背板和機箱之間的互連。它是PCI標準的一個演進版本,因此,在軟件結構上仍保持著對PCI的兼容性。

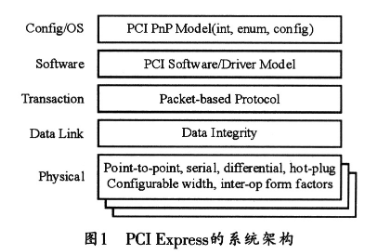

PCI Express是基于層次化的、高速的串行通信技術。其協議棧可分為物理層、數據鏈路層和傳輸層。

其中,物理層包括低電壓差分信號的高速串行接口、8B/10B編碼以及AC耦合差分信號。通常把一組LVDS雙絞線稱為一個通道(lane),而且PCI Express允許將多個通道合并成一個更大更寬的端口,如x1,x2…直到x32。物理層接口可支持熱插拔(hot-plugging)。

數據鏈路層可支持與臨近PCI Express實體交換數據包,同時支持數據完整性(data integrity)和順序性檢查,以及數據包的確認和流量控制的能力。

PCI Express技術系統中的傳輸層可在主機和終端設備間傳送讀/寫請求,并可選擇性的提供傳輸層的端到端(end-to-end)數據包的完整性檢查(CRC-32)。

一直以來,PCI Express傳輸系統中的物理層的速度一直在不斷的提高,但是,分層結構使物理層的變化不會影響到它的上層。如PCI Express1.x標準的時鐘頻率是1.25 GHz,2.0標準的則為2.5 GHz,3.0標準的是4 GHz。圖l所示是PCI Ex-press協議棧結構。

PCI Express的QOS可通過定義8個運輸等級(TC-Traffic Classes)、八個虛擬通道(VC-VirtualChannel)、TC到VC的映射以及VC的仲裁機制來實現。

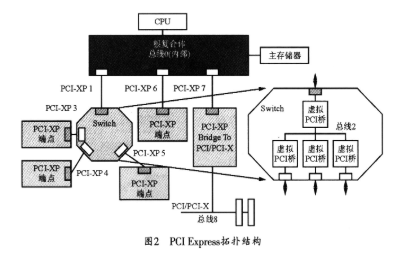

PCI-SIG組織則定義了從PCI Express串行接口到PCI/PCI-X的橋接規范。該規范可以使得當前使用PCI/PCI-X的應用系統能夠平滑的轉移到PCI Express。圖2所示是一個典型的PCI Express系統,其中包含有根復合體(root complex)、PCIExpress交換開關(switch)、橋(bridge,PCI Expressto PCI-X,PCI Express to PCI)以及端點(end-point)等設備。

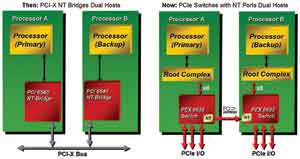

2、PCI Express非透明橋

與PCI/PCI-X一樣,PCI Express本身也是開發維護一個以單一主機為中心的系統架構,但是人們一直使用非透明橋把他們用在多主機的環境中。

非透明橋的功能和透明橋很相似,其主要差別只有一點,即在非透明橋的兩邊都有智能設備或處理器,并且他們擁有獨立的地址空間。而且,非透明橋一邊的主機不能看到橋另一邊的完整地址或I/O空間。每個處理器把非透明橋的另一邊看做一個端點(endpoint),并把它映射到自己的地址空間。

2.1 地址翻譯

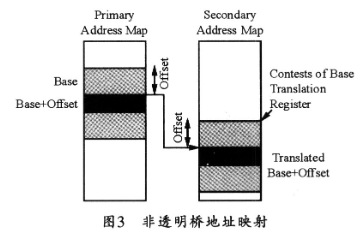

在非透明橋環境中,PCI Express系統需要在從一個內存地址空間穿越到另一個地址空間時進行地址翻譯。每一個非透明橋(NTB)端口都有兩套基地址寄存器(BAR),一套是給主設備端用的,另一套是給從設備端用的。基地址寄存器可用來定義在非透明橋另一端的內存地址空間的地址翻譯窗口,并允許這個翻譯被映射到本地的內存或I/O空間。每個BAR定義了一個設置寄存器(setup register),可用來定義窗口的大小、類型以及一個地址翻譯寄存器。與透明橋基于總線號轉發所有CSRs不同,非透明橋設備只接受針對本設備的CSR事務。其地址翻譯技術有直接地址翻譯和查表地址翻譯兩種。

在直接地址翻譯模式下,地址翻譯的過程是基于事務終結的BAR基址加上一個偏移量。BARs中的基址翻譯寄存器可被用來設置這樣的翻譯。圖3所示給出了從主設備端地址映射到從設備端地址的偏移過程。

BARs則用一種特別的查找表來為落在它窗口中的事務進行地址翻譯。因為地址中的索引域可通過編程來調節窗口大小,因此,這種方法在本地地址到主機地址的映射中具有更高的靈活性。通常索引被用來提供新內存地址的高位比特(bits)。

2.2 處理器間的通信

非透明橋允許橋兩邊的主機通過便箋寄存器、門鈴寄存器和心跳消息來交換一些狀態信息。

便箋寄存器在非透明橋的兩端都是可讀寫的,但是,便箋寄存器的數量在具體的實現中是可以不同的。他們可以被橋兩邊的設備用來傳送一些狀態信息,也可作為通用的可讀可寫寄存器使用。

門鈴寄存器被用來從非透明橋的一邊向另一邊發送中斷。非透明橋的兩邊一般都有軟件可以控制的中斷請求寄存器和相應的中斷屏蔽寄存器。這些寄存器在非透明橋的兩邊都是可以被訪問的。

心跳消息一般來自主設備端往從設備端的主機,可用來指示它還活著。從設備主機可監控主設備主機的狀態,如果發現出錯,它就可以采取一些必要的措施。通過門鈴寄存器可以傳送心跳消息。當從設備主機沒有收到一定數量預先規定好的心跳消息時,就可以認為主設備的主機出錯了。

3、基于PCI Express非透明橋的多主機系統

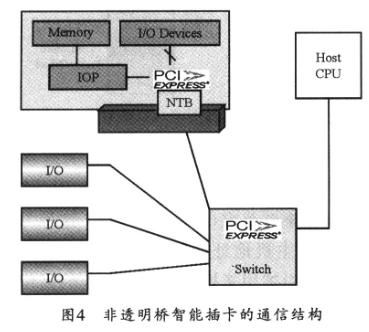

3.1 智能插卡

在智能卡模式下,智能插卡上的PCI Express非透明橋可以將IOP和Host CPU隔離開來,但仍允許這兩個CPU通過一些特殊的寄存器進行通信。圖4所示是智能插卡模式下的非透明橋的通信結構。

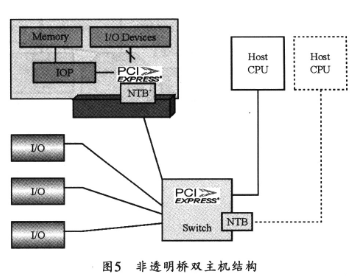

3.2 雙主機模式

非透明橋也可用在雙主機(Dual Host)、主機故障轉移(Host Failover)和負載分擔(Load-shar-ing)等應用中。圖5所示是將兩個Host CPU被非透明橋隔離開的結構示意圖。

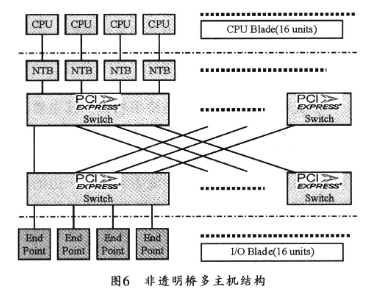

3.3 多主機模式

在多主機系統中,每一個主機都可以通過非透明橋接入到系統之中,并且可以訪問所有的端點。在PCI的枚舉過程中,每個端點都要和某個特定的CPU關聯,但在正常的操作過程中,依賴于非透明橋的地址翻譯能力。所有的CPU都可以訪問所有的端點。圖6所示是主機系統的非透明橋結構。

4、結束語

非透明橋技術在PCI時代就已被應用。現在,在PCI Express系統中也有類似的實現。相信在不遠的將來,從簡單的智能插卡到復雜的、帶虛擬輸入輸出技術的多主機系統,人們都將看到PCIExpress非透明橋的廣泛應用。

責任編輯:gt

-

接口

+關注

關注

33文章

8694瀏覽量

151927 -

PCI

+關注

關注

4文章

671瀏覽量

130477 -

主機

+關注

關注

0文章

1011瀏覽量

35312

發布評論請先 登錄

相關推薦

CPU如何通過PCI Express訪問板上的系統?

針對可編程PCI Express解決方案的評估方法

基于PCI Express總線高速數據采集卡的設計與實現

基于PCI Express實時視頻采集系統的設計

PCI Express交換及橋接芯片的展望

PCI Express插槽,什么是PCI Express插槽

PCI Express總線

PCI Express解決方案的介紹

如何創建和使用Xilinx的UltraScale PCI Express解決方案

PCI Express系統中DMA的基本功能介紹

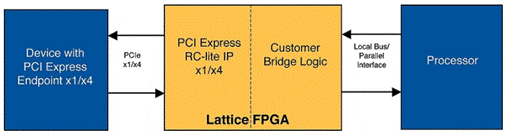

FPGA中實施PCI Express橋接解決方案

基于PCI Express非透明橋實現多主機系統的設計方案研究

基于PCI Express非透明橋實現多主機系統的設計方案研究

評論