在NiosⅡ系統的構建過程中,SoPCBuilder開發環境集成了許多常用類型的設備模型,供開發者調用。在日新月異的嵌入式系統設計中開發環境所集成的接口設備是非常有限的,有時無法滿足開發者的需要,SoPCBuilder開發工具允許用戶依據規則擴展自己的所需設備,完成系統的設計和開發,開發者按照Avalon總線規范將設備驅動程序集成到SoPCBuilder的硬件抽象層(HAL)中,在SoPCBuilder環境下加載使用,方便了用戶開發一個自定制的片上系統。本文通過在NiosⅡ嵌入式系統內部集成了基于Avalon總線的脈沖寬度調制(PWM)從外設,介紹了自定制Avalon設備的過程。將其應用在嵌入式智能小車監控系統,為采用NiosII處理器的開發者提供了一些方法和建議。

1、定制基于Avalon總線的用戶外設介紹

NiosⅡ的Avalon總線不同于其他微處理器的固定外設,NiosⅡ的外設是可以任意定制的,這使得用戶可以根據具體的應用需求而定制。所有的NiosⅡ系統外設都是通過Avalon總線與NiosⅡ軟核相連,從而進行數據交換。因此對于用戶定義的外設必須遵從該總線協議才可與NiosⅡ之間建立聯系。

Avalon信號接口定義了一組信號類型片選、讀使能、寫使能、地址、數據等,用于描述主從外設上基于地址的讀寫接口。外設使用準確的信號與其內核邏輯進行接口,并刪除會增加不必要開銷的信號。

在NiosⅡ系統中一個自定義設備由如下幾部分組成:

(1)硬件文件:用HDL語言編寫的描述自定義設備元件邏輯的硬件描述文件。

(2)軟件文件:用C語言編寫的設備寄存器文件以及設備的驅動程序文件。

(3)設備描述文件(Ptf):本文件描述了設備的結構,包含SoPCBuilder配置以及將其集成到系統中時所需要的信息。本文件由SoPCBuilder根據硬件文件以及軟件文件自動生成。

2、基于NiosⅡ系統的PWM設計

PWM是利用數字輸出來對模擬電路進行控制的一種非常有效的技術,廣泛應用于從測量、通信到功率控制與變換的許多領域中。實際上PWM是一種對模擬信號電平進行數字編碼的方法,通過高分辨率計數器的使用,方波的占空比被調制用來對一個具體模擬信號的電平進行編碼。PWM信號仍然是數字的,因為在給定的任何時刻,滿幅值的直流供電或者完全有,或者完全無。電壓或電流源是以一種通或斷的重復脈沖序列被加到模擬負載上。通即是直流供電被加到負載上,斷即是供電被斷開。只要帶寬足夠,任何模擬值都可以使用PWM進行編碼。

2.1硬件設計

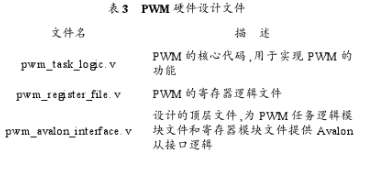

硬件文件指的是HDL文件,由以下幾個模塊組成:

邏輯模塊:描述設備的邏輯功能;

寄存器映射模塊:為內部邏輯模塊和Avalon總線提供了通信接口;

Avalon總線接口模塊:使Avalon總線訪問寄存器從而完成相應的邏輯功能。

2.1.1邏輯結構

對于自定義的PWM也是由以上幾部分模塊組成。PWM按照以下要求設計:

(1)任務邏輯按一個簡單時鐘進行同步操作。

(2)任務邏輯使用32位計數器為PWM提供一個一定范圍的周期和占空比,最大周期可設為232個clk。

(3)可以使用微控制器來設置PWM的周期和占空比的值,因此要提供一個可對寄存器進行讀寫的接口和控制邏輯。

(4)定義寄存器來存儲PWM周期和占空比的值。

(5)微控制器可以通過控制寄存器的禁止位關閉PWM輸出。

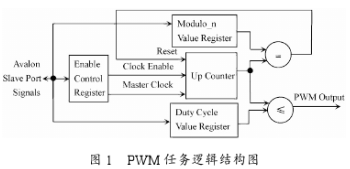

PWM任務邏輯的結構圖如圖1所示。

PWM任務邏輯由輸入時鐘(clock)、輸出信號端口(pwm_out)、使能位、32位計數器以及一個32位比較電路組成。clk作為32位計數器的時鐘信號,32路比較電路比較32位計數器的當前值與占空比設定寄存器(DutyCycleValueRegister)中的值來決定pwm_out的輸出為高或低。當當前計數器中的值小于或等于占空比寄存器中的值時,pwm_out輸出低電平,否則輸出高電平。PWM周期設定寄存器(Modulo_nValueRegister)用來設置pwm_out的信號周期,當當前計數器的值等于周期設定寄存器中的設定時,產生一個復位信號來清除計數器中的值。使能控制寄存器(EnableControlRegister)能使時鐘信號有效或無效,即控制計數器是否計數,從而保持pwm_out輸出保持當前不變。

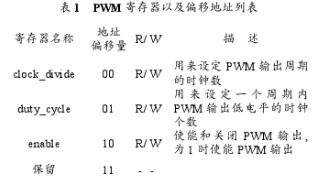

PWM內部包括使能控制寄存器(EnableControlRegister)、周期設定寄存器(Modulo_nValueRegister)以及占空比設定寄存器(DutyCycleValueRegister),如圖1所示。設計中將各寄存器映射成Avalon從端口地址空間內一個單獨的偏移地址。每個寄存器都能進行讀/寫訪問,軟件可以讀回寄存器中的當前值。表1是PWM寄存器以及偏移地址列表。

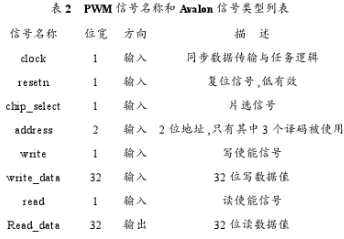

PWM的Avalon接口需要一個簡單的從端口,該端口使用Avalon總線信號完成寄存器的讀/寫傳輸。PWM與Avalon總線接口所需的信號如表2所示。

圖2中:clock_divide信號設定PWM輸出周期的時鐘數,dutv_cycle信號設定一個周期內PWM輸出低電平的時鐘個數,兩個信號設定值決定PWM信號的占空比和周期。

2.2軟件設計

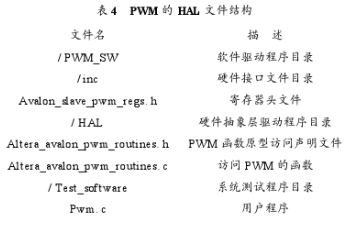

如果要使Nios軟核能夠訪問自定義的設備,就必須根據先前的硬件設計按照硬件提取層的文件結構編寫設備驅動程序。以PWM為例說明HAL的文件結構,如表4所示。

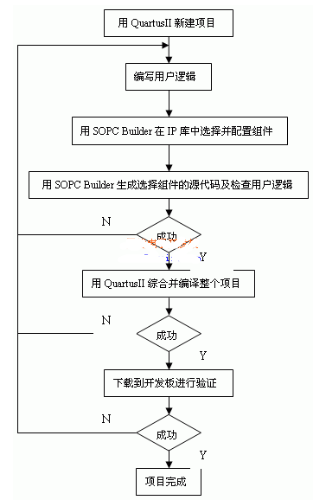

2.3將PWM設計封裝為SoPCBuilder元件

當硬件文件和軟件文件都已建立好后,便可以通過SoPCBuilder中帶有的設備編輯器將自定義設備封裝到開發環境內部,在構建NiosⅡ系統時可以對其直接調用。在SoPCBuilder中單擊CreatNewComponent,創建新元件向導添加HDL文件、設置信號和接口添加軟件,最終生成包含描述文件、用戶存放硬件描述文件的文件夾以及用來包含HAL軟件文件的HAL文件夾。

2.4構建Nios系統

構建好的內核文件在QuartusⅡ中編譯,生成pof配置文件下載到E2PROM芯片中,接下來就可以使用NiosIDE開發環境編輯用戶程序,以及通過JTAGBlaster或者USBBlaster在目標板上對應用程序進行調試。

3、自定制外設PWM在嵌入式智能小車監控系統中的應用

智能小車監控系統設計應用周立功公司SmartSoPC核心板,FPGA為Altera公司的EPlC12,NiosⅡ處理器作為嵌入式CPU,機器人車電機共有兩個,左輪電機和右輪電機。該部分包括電機驅動電路和電機控制電路,即左電機的驅動與控制以及右電機的驅動與控制。驅動電路采用CTMicroelectronics公司的大功率直流電機驅動芯片L289,調速控制采用PWM來控制汽車的前進速度,由FPGA寫入控制字,可得到不同占空比的PWM驅動信號,此PWM信號送人電機驅動芯片的控制端來調節速度。調用電機驅動程序,改變PWM占空比,輸出PWM波,實現電機的速度控制。用PWM信號控制直流電動機速度,頻率較低時,電動機不會穩定運轉,頻率較高時,PWM信號的驅動效率降低。經過多次實際電路的測試,調試結果顯示當頻率在500~1000Hz時,效果較好。部分C語言控制代碼如下:

4、結語

NiosⅡ嵌入式處理器是用戶可配制的通用RISC嵌入式處理器,是一個非常靈活和強大的處理器。基于此種技術的嵌入式系統設計可以方便地將一般設備和自定義設備模塊集成到系統中,豐富了接口資源,從而能使用戶快速地開發一個自定制片上系統,提高了效率,縮短了開發周期。本文通過自定制PWM外圍設備的方法,并通過硬件測試證明了方案的可行性和正確性,希望能夠為采用NiosⅡ處理器的開發人員提供一些方法和建議。

責任編輯:gt

-

處理器

+關注

關注

68文章

19409瀏覽量

231207 -

嵌入式

+關注

關注

5094文章

19178瀏覽量

307732 -

總線

+關注

關注

10文章

2903瀏覽量

88402

發布評論請先 登錄

相關推薦

采用nios和μClinux實現嵌入式系統設計

Cyclone II FPGA和Nios II嵌入式處理器的優勢

Avalon設備怎么定制?

Nios II入門起步-創建一個嵌入式處理器系統

基于Chirp函數的Nios Ⅱ嵌入式實現

介紹如何用Nios II 軟核處理器來開發FPGA嵌入式系統軟件

基于Nios II實現AVALON總線與USB控制器的接口設計

NiOSⅡ處理器的Avalon總線架構資料下載

基于Avalon總線的PWM外設實現NiosⅡ嵌入式處理器的設計

基于Avalon總線的PWM外設實現NiosⅡ嵌入式處理器的設計

評論