引言

PCIE總線是由Intel公司提出用來取代現(xiàn)行PCI總線的下一代總線技術(shù),被公認(rèn)為未來總線的發(fā)展方向,目前已經(jīng)成功應(yīng)用在了商業(yè)機(jī)上。相對于目前流行的PCI總線,它具有如下特點(diǎn):

采用了串行點(diǎn)對點(diǎn)模式,數(shù)據(jù)總線從并行走回向串行無疑是一個趨勢,如現(xiàn)在流行的SATA總線、PCIE總線和rapidIO總線都是串行總線。現(xiàn)在串行總線在速度上的優(yōu)勢可以說是毋庸置疑的。PCIE總線在每個方向上都有X1,X2,X4,X8,X16或X32個信號對,用戶可根據(jù)不同的需求采用不同的配置。同時串行信號還具有管教更少,便于調(diào)試的優(yōu)點(diǎn)。

PCIE采用了基于數(shù)據(jù)包的協(xié)議來編碼事物,而不是PCI體系結(jié)構(gòu)的總線周期。數(shù)據(jù)包被串行發(fā)送和接受,并被字節(jié)拆分來通過物理鏈路。鏈路上實現(xiàn)的通道越多,數(shù)據(jù)包發(fā)送的數(shù)據(jù)越快,鏈路的帶寬也越寬。同時PCIE還定義了各種類型的數(shù)據(jù)包,如存儲器讀/寫請求、I/O讀/寫請求、配置讀/寫請求、消息請求和完成數(shù)據(jù)包等。

PC/104標(biāo)準(zhǔn)是一種嵌入式的總線標(biāo)準(zhǔn),具有功耗低,尺寸小,堆棧式結(jié)構(gòu)的特點(diǎn)。隨著目前各種應(yīng)用數(shù)據(jù)傳輸量的增大,現(xiàn)行的PCI總線在帶寬方面已經(jīng)略顯疲態(tài),而新近瑞士邏輯提出的PC/104 Express標(biāo)準(zhǔn),使得PCIE總線技術(shù)被成功地應(yīng)用在了PC/104標(biāo)準(zhǔn)的板卡上。本文采用了PLX公司的PEX8311橋接芯片,完成了PCIE到局部總線接口的轉(zhuǎn)換,應(yīng)用PLX公司提供的開發(fā)工具在Linux操作系統(tǒng)下實現(xiàn)了板卡的驅(qū)動應(yīng)用。在軟硬件兩方面進(jìn)行了設(shè)計,完成了PCIE/104板卡的功能,升級了系統(tǒng)的總線。

1、 PCIE/104高速信號接口卡的系統(tǒng)

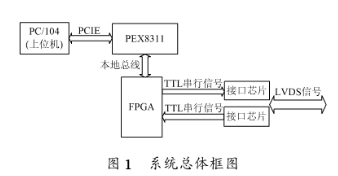

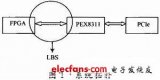

PCIE/104高速信號接口卡的系統(tǒng)設(shè)計方案如圖1所示。

外部傳感器采集到的數(shù)據(jù)通過LVDS,RS 422等電平方式,以固定的不同串口波特率傳到FPGA內(nèi)部集成的各自對應(yīng)的雙口RAM中。當(dāng)寫入了固定字節(jié)后,設(shè)定標(biāo)志位stage為1,同時發(fā)出中斷信號LINT#給PEX8311。PEX8311產(chǎn)生了assert_INT1信息,并通過PCIE接口發(fā)給上位機(jī)。上位機(jī)保存好現(xiàn)在的任務(wù)后,通過PCIE開始發(fā)出存儲器讀命令給PEX8311。PEX8311獲得命令后,向FPGA發(fā)出本地總線申請信號,F(xiàn)PGA作為本地端的控制器將本地總線控制權(quán)交給PEX8311。PEX8311開始讀數(shù)據(jù),首先要進(jìn)行的是讀取標(biāo)志位,在讀取了標(biāo)志位后,上位機(jī)就知道是哪幾路串口信號需要讀入。然后,把標(biāo)志位清掉,這樣相當(dāng)于清掉了中斷信號。接著,中斷服務(wù)程序在進(jìn)入到各個串口的RAM中,來讀取相應(yīng)的數(shù)據(jù)。在多路串口信號傳輸過來時,針對該系統(tǒng),采用的是優(yōu)先滿足高速串口的原則,也就是采用高速串口的標(biāo)志位作為中斷信號,每次產(chǎn)生中斷后查詢其他標(biāo)志位。數(shù)據(jù)到上位機(jī)后待處理。該系統(tǒng)目前實現(xiàn)的是兩路串口,而多路串口原理相同。

1.1 硬件總體概述

主要包括以下幾部分,PEX8311橋接芯片負(fù)責(zé)完成本地總線和PCIE總線的相互裝換;FPGA選用了spartan-3an 1400K。這里在內(nèi)部實現(xiàn)了3個模塊,首先完成雙口RAM模塊;其次完成了多路串口數(shù)據(jù)的接受與協(xié)調(diào)模塊;最后還要實現(xiàn)PEX8311芯片本地端控制器模塊。

1.1.1 PEX8311芯片介紹

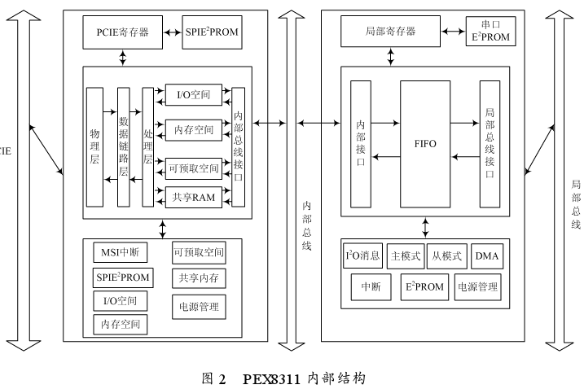

PEX8311是PLX Technology公司推出的一款專用于將DSP,F(xiàn)PGA等處理器總線接口升級為PCIE的橋接器件。利用PEX8311靈活的局部總線可以方便地連接多種存儲器、緩存器及。FPGA,DSP等邏輯芯片,使復(fù)雜的PCI-E接口設(shè)計簡單化。PEX8311兼容PCI Express 1.0標(biāo)準(zhǔn),其本地總線和寄存器與PCI9056兼容,能夠提供完整的本地總線到PCI-E的接口,包括地址轉(zhuǎn)換、包生成與解碼、信號中斷支持及并/串轉(zhuǎn)換等。

PEX8311的特點(diǎn)如下:

(1)集成了單通道、全雙工2.5 Gb/s傳輸?shù)腜CI Express端口;

(2)可配置局部總線寬度,支持8位、16位和32位的總線方式;

(3)支持單路和多路總線操作模式;

(4)高性能的DMA數(shù)據(jù)傳輸,支持?jǐn)?shù)據(jù)塊模式、集散模式、循環(huán)隊列管理模式和命令模式;

(5)支持端點(diǎn)和根復(fù)合體模式;

(6)芯片小型封裝,適合緊湊的電路板設(shè)計;

(7)芯片低功耗設(shè)計;

(8)3.3 V的I/O并兼容5 V系統(tǒng);

(9)啟動配置的串行E2PROM支持(SPI和Microwire接口);

(10)有8 KB的通配共享RAM。

PEX8311的內(nèi)部結(jié)構(gòu)如圖2所示。

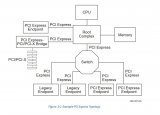

1.1.2 PCIE/104總線標(biāo)準(zhǔn)介紹

PC/104是最早由瑞士邏輯提出的一種工業(yè)總線標(biāo)準(zhǔn),它由最早的PC/104總線發(fā)展到PC/104+總線,直到目前的PC/104 Express,分別對應(yīng)ISA總線、PCI總線和PCIE總線。由于它是一種堆棧型的嵌入式總線,所以將PCIE總線應(yīng)用在這個標(biāo)準(zhǔn)上與普通的PCIE金手指有一些不同。為了滿足PC/104的嵌入式堆棧結(jié)構(gòu),使其能夠?qū)崿F(xiàn)從板子上、下都可以連接,必須采用PCIE Switch芯片,這里使用的是PERICOM公司

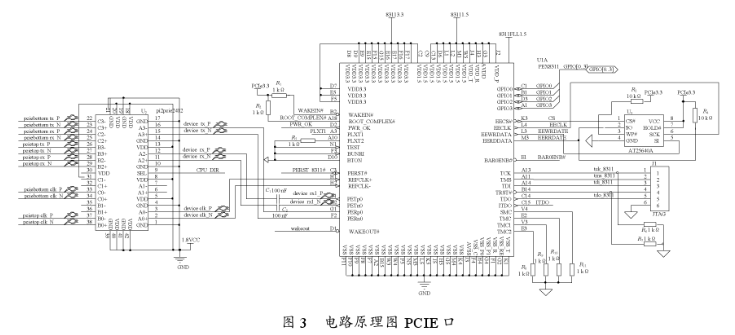

制造的PI2PCIE2412款Switch芯片。電路原理圖如圖3所示。

圖3中接受、發(fā)送和差分時鐘這3對差分信號線通過轉(zhuǎn)接芯片變成了6對差分信號線。由主機(jī)板卡發(fā)出選擇信號(cpu_dir),分別控制設(shè)備板卡是在主機(jī)板卡的上面還是下面。同時采用MAX6306芯片來鏈接PEX8311的復(fù)位端和PCIE接插件的復(fù)位端,同時實現(xiàn)了手動復(fù)位和LOCAL端的復(fù)位。

1.1.3 PEX8311的外圍電路配置與LOCAL端接口的控制

PEX8311有幾個類別的模式選擇,分別是根聯(lián)合體模式(Rootcomplex)與終端模式(Endpoint),根據(jù)需要這里選擇了終端模式。此外PEX 8311還區(qū)分C模式,J模式,M模式。這三種模式解釋如下:C模式的地址線與數(shù)據(jù)線是分開的,J模式下地址線與數(shù)據(jù)線是復(fù)用的,而M模式是針對了Motor的本地端CPU設(shè)置的。三種模式通過模式選擇管腳選擇,這里選擇C模式作為工作模式。PEX8311有1.5 V,2.5 V,3.3 V三種電源供電以及一個模擬電源1.5VPLL。在配置寄存器方面,PEX8311有兩個配置寄存器,分別是采用Spi-Compatible接口的PCIE配置寄存器和采用了Micro-Wire-Compatibel接口的本地配置寄存器。采用了Spartan-3an 1400 k來提供控制接口與高速緩存,選擇這款FPGA主要因為它是有內(nèi)部FLASH,不用再加外部的E2PROM。

由于PC/104是一種嵌入式的板卡,體積比較小,所以用這款FPGA是可以節(jié)省板上的空間。FPGA內(nèi)部程序的編寫是關(guān)鍵之一。這里采用Verilog,實現(xiàn)對PEX8311的控制,當(dāng)上位機(jī)響應(yīng)了中斷后,對PEX8311發(fā)出讀數(shù)信號。PEX8311通過LHOLD申請控制本地總線,待收到FPGA發(fā)出的LHOLDA響應(yīng)信號后獲得本地總線的控制權(quán),并立即啟動4 B突發(fā)模式。FPGA在收到有效的LW/R讀信號和ADS地址選通信號后,發(fā)出Ready本地準(zhǔn)備好應(yīng)答信號。PEX8311開始從雙口中讀取數(shù)據(jù),傳輸最后一個數(shù)據(jù)時,PEX8311發(fā)出BLAST信號,雙口RAM使得讀使能和輸出使能無效。

1.2 系統(tǒng)軟件部分的實現(xiàn)

該系統(tǒng)的軟件部分是在Linux下實現(xiàn)的,在Linux中所有的設(shè)備都被看成文件來對待。在Linux內(nèi)核中,設(shè)備驅(qū)動作為文件系統(tǒng)的一個模塊存在。它向下負(fù)責(zé)與硬件系統(tǒng)的交互,向上通過一個通用的接口掛接到文件系統(tǒng)上面。從而和系統(tǒng)的內(nèi)核鏈接起來。設(shè)備驅(qū)動為應(yīng)用程序屏蔽了很多細(xì)節(jié)。使得應(yīng)用程序?qū)ν庠O(shè)的操作就和操作普通的文件是一個樣子的。利用PLX公司提供的開發(fā)工具,驅(qū)動的開發(fā)是比較方便的,本文系統(tǒng)中主要用到的是要編寫一個中斷服務(wù)程序:系統(tǒng)在收到中斷,保存現(xiàn)場。進(jìn)入中斷服務(wù)程序。首選讀取標(biāo)志位,再馬上清中斷,之后讀取響應(yīng)RAM中的數(shù)據(jù)。最后恢復(fù)現(xiàn)場,完成操作。

2、 系統(tǒng)PCB設(shè)計和高速信號的完整性分析

由于PCIE的傳輸速率較高,單向速率達(dá)到2.5 Gb/s。所以對板子的布線有嚴(yán)格的要求。疊層這里選用了8層PUCB板,有4個電源層,使得每個信號都能夠屏蔽在電源層與地層中間。從而減少了信號的電磁輻射。對于PCIE的差分線部分:微帶線要求差分線寬5 mil,間距小于12 mil,差分線間距離大于20 mil,同時與地層間距為3.5~5.5 mil。帶狀線要求線寬4 mil,間距小于11 mil,間距大于20 mil。且對于收發(fā)差分線,差分線長差距不能大于5 mil。這些都是為了能達(dá)到PCIE規(guī)范的要求,即單端阻抗55 Ω,差分阻抗100 Ω(偏差10%)而設(shè)置的。

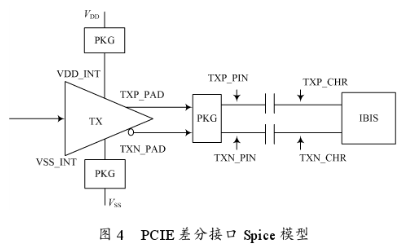

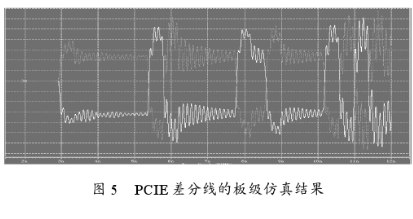

經(jīng)過ploar軟件計算,將以上的數(shù)據(jù)輸入進(jìn)去,再加入PCB廠家提供的介電常數(shù)等參數(shù),最后得出的阻抗完全滿足設(shè)計需求。多層板的高速信號設(shè)計很有必要進(jìn)行信號完整性仿真,應(yīng)用廠家提供的IBIS模型,采用Hyperlynx對板子進(jìn)行了本地端和時鐘端的信號完整性仿真。并根據(jù)仿真對布線提供了約束條件。而針對PCIE的高速差分端總線,因為在高速信號仿真方面IBIS模型還不夠精確,所以,PLX公司對其兩對收發(fā)端口提供SPice模型,如圖4所示。

將上訴模型導(dǎo)入HSpice中,同時引入PCIESwitch芯片給出的IBIS模型與板子上面的差分線trace的rglc模型。輸出端的仿真效果圖如下,可以看出差分信號的幅值是可以滿足PCIE規(guī)范的電氣要求的。

3、 結(jié)語

PC/104作為一種嵌入式總線標(biāo)準(zhǔn)已經(jīng)被很多控制系統(tǒng)所采用,而PCIE/104接口的提出將未來最為流行的串行差分總線結(jié)構(gòu),引入到了這種嵌入式總線標(biāo)準(zhǔn),從而為各種高速、高帶寬的嵌入式系統(tǒng)提供了選擇。目前該系統(tǒng)由于采用了PCIE總線,相比采用PLX9054實現(xiàn)的PCI接口具有明顯的優(yōu)勢。

責(zé)任編輯:gt

-

芯片

+關(guān)注

關(guān)注

456文章

51192瀏覽量

427300 -

Linux

+關(guān)注

關(guān)注

87文章

11345瀏覽量

210404 -

操作系統(tǒng)

+關(guān)注

關(guān)注

37文章

6896瀏覽量

123751

發(fā)布評論請先 登錄

相關(guān)推薦

基于PCIE總線的PLX8311橋芯片硬件設(shè)計原理圖

【FPGA干貨分享三】基于FPGA的LBS控制器設(shè)計

自己做的PXIe板卡,插在NI的PXIe-1082背板上不識別

PEX8311 DMA 沒反應(yīng)?

如何構(gòu)建一個PCI-E架構(gòu)的實時海量存儲系統(tǒng)?

PEX8311 pdf datasheet

基于Linux操作系統(tǒng)的嵌入式網(wǎng)關(guān)的實現(xiàn)

Linux操作系統(tǒng)

Linux操作系統(tǒng)原理及應(yīng)用

Linux操作系統(tǒng)實現(xiàn)了在PC104 上的裁減和移植

基于FPGA的PEX8311的LBS控制器的實現(xiàn)

PEX 8311 x1 Lane PCI Express Bridge,21 x 21mm PBGA

采用PEX8311橋接芯片和Linux操作系統(tǒng)實現(xiàn)PCIE/104板卡的設(shè)計

采用PEX8311橋接芯片和Linux操作系統(tǒng)實現(xiàn)PCIE/104板卡的設(shè)計

評論