引 言

隨著電子技術、計算機技術和EDA技術的不斷發展,利用FPGA/CPLD進行數字系統的開發已被廣泛應用于通信、航天、醫療電子、工業控制等領域。與傳統電路設計方法相比,FPGA/CPLD具有功能強大,開發周期短,投資少,便于追蹤市場變化及時修改產品設計,以及開發工具智能化等特點。近年來,FPGA/CPLD發展迅速,隨著集成電路制造工藝的不斷進步,高性價比的FPGA/CPLD器件推陳出新,使FPGA/CPLD成為當今硬件設計的重要途徑。在FPGA/CPLD的應用設計開發中,VHDL語言作為一種主流的硬件描述語言,具有很強的電路描述和建模能力,能從多個層次對數字系統進行建模和描述,從而大大簡化了硬件設計任務,提高了設計效率和可靠性,并在語言易讀性和層次化、結構化設計方面。表現出了強大的生命力和應用潛力。

QuartusⅡ是Altera公司在21世紀初推出的FPGA/CPLD集成開發環境,是Altera公司前一代FPGA/CPLD集成開發環境Max+PlusⅡ的更新換代產品,其界面友好,使用便捷,功能強大,為設計者提供了一種與結構無關的設計環境,使設計者能方便地進行設計輸入、快速處理和器件編程。

計數器是數字系統中使用最多的時序電路之一,不僅能用于對時鐘脈沖計數,還可以用于分頻、定時、產生節拍脈沖和脈沖序列以及進行數字運算等。可變模計數器由于計數容量可以根據需要進行變化,為其廣泛使用創造了便利。這里在QuartusⅡ開發環境下,用VHDL語言設計了一種具有清零、置數、使能控制、可逆計數和可變模功能的計數器。

1 基本可變模計數器設計

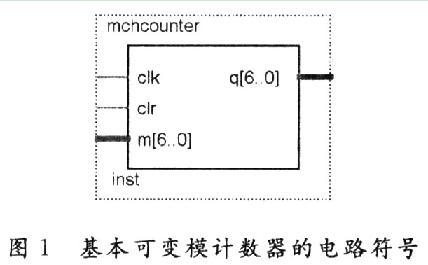

可變模計數器是指計數/模值可根據需要進行變化的計數器。電路符號圖1所示,clk為時鐘脈沖輸入端,clr為清零端,m為模值輸入端,q為計數輸出端。

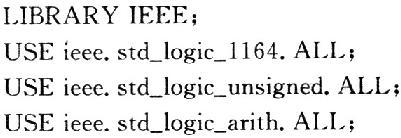

基本可變模計數器的VHDL代碼如下所示:

說明:上述代碼設計采用了常用的if語句結構,即“if條件句then順序語句elsif條件句then順序語句else順序語句end if”結構,實現模值小于99的可變模計數。

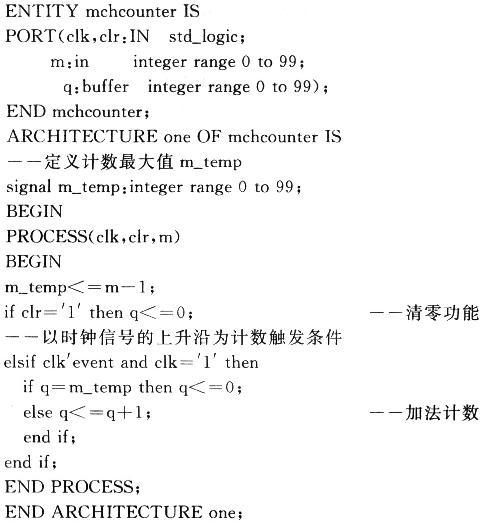

從上述的代碼可以看出,基本的可變模計數器的功能單一。仿真驗證則表明在進行模值變換時,基本的可變模計數器存在一些功能上的缺陷:計數器若是由較小的模值變化為較大的模值時,能正常的進行變模計數;但當其由較大的模值變化為較小的模值,則可能出現計數失控,如圖2所示,圖中顯示了當模值由12變換為7時,即發生了計數失控。失控的原因是大于當模值由12變換為7時,計數輸出為q為11,大于當前模值7的計數最大值6,由此產生了計數失控。

2 改進的多功能可變模計數器

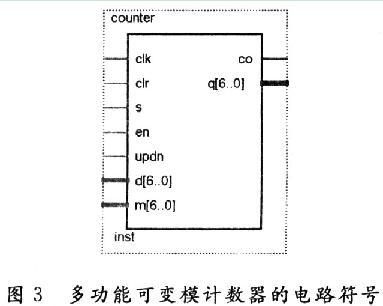

為了克服上述基本可變模計數器的缺陷,并增加更多的控制功能,在此設計了一種改進的多功能可變模計數器,具有清零、置數、使能控制、可逆計數和可變模功能。其電路符號如圖3所示,clk為時鐘脈沖輸入端,m為模值輸入端,clr為清零控制端,s為置數控制端,d為置數輸入端,en為使能控制端,updn為計數方向控制端,q為計數輸出端,co為進位輸出端。

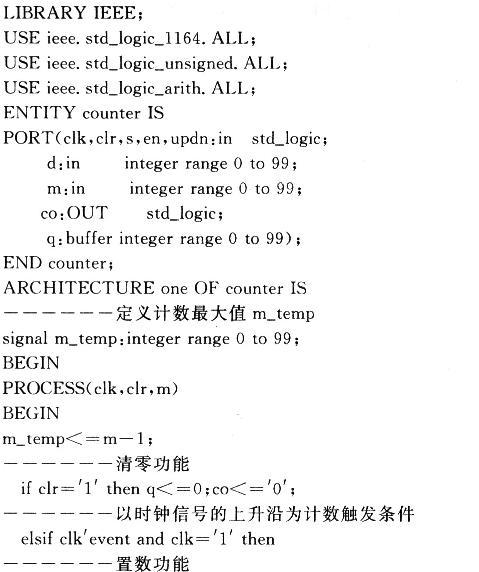

這里所設計的多功能可變模計數器的VHDL代碼如下所示:

LIBRARY IEEE;

值得注意的是,這里所設計的多功能可變模計數器具有如下特點:

(1)該設計的多功能可變模計數器具有多個功能控制端。因此各個控制端的優先權順序就成為設計的關鍵,經過理論分析和仿真調試,最終確認的優先權順序為:clr(清零)→clk(時鐘觸發)→s(置數)→en(使能)→updn(計數方向)。這個優先權順序可以有效地保證各個功能的完整實現,以及技術器的穩定運行。

(2)為了防止出現計數失控,大多數計數器采用給計數器增加一個復位控制端的辦法,當發現計數輸出q發生了計數失控時,通過復位控制端將計數器復位來排除計數失控。這種方法雖然有效,但是每次出現計數失控都要手動控制復位,給實際使用帶來了不便。該設計的多功能可變模計數器中,將當前的計數輸出q與當前的計數最大值m_temp進行比較,如果q比m_temp大,則強制將m_temp賦給q,這樣就可以自動避免計數失控,不必再增加手動的復位控制端。

3 仿真結果分析

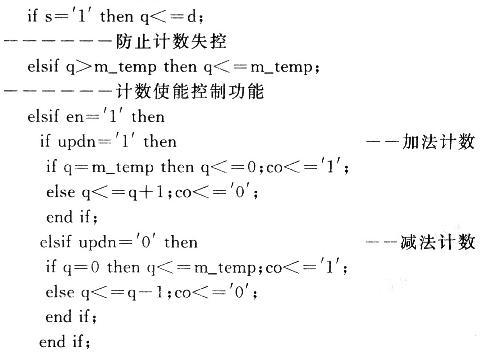

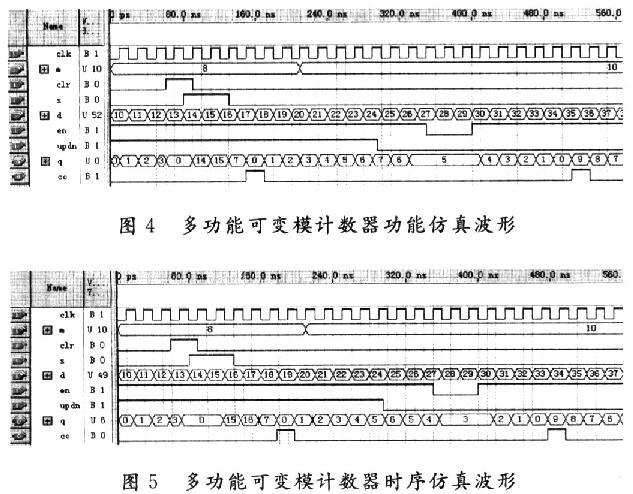

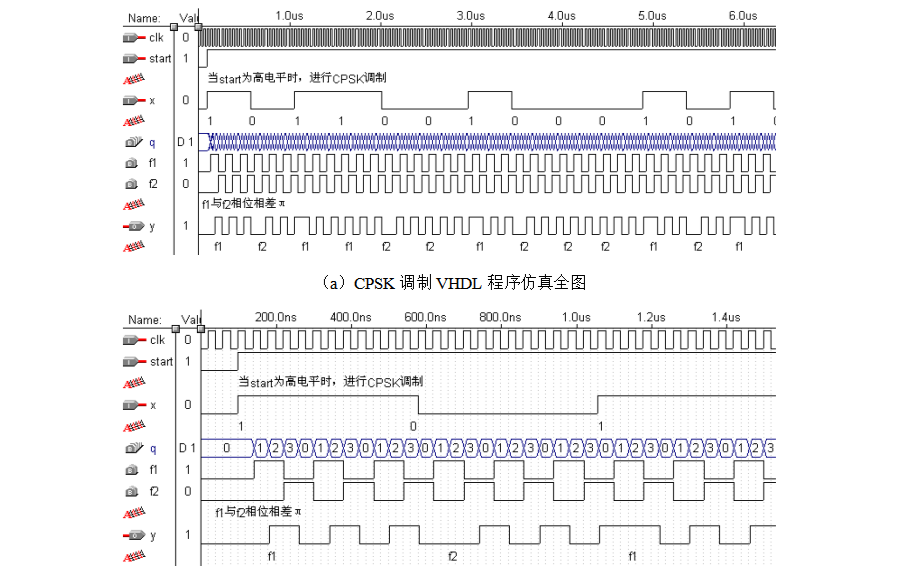

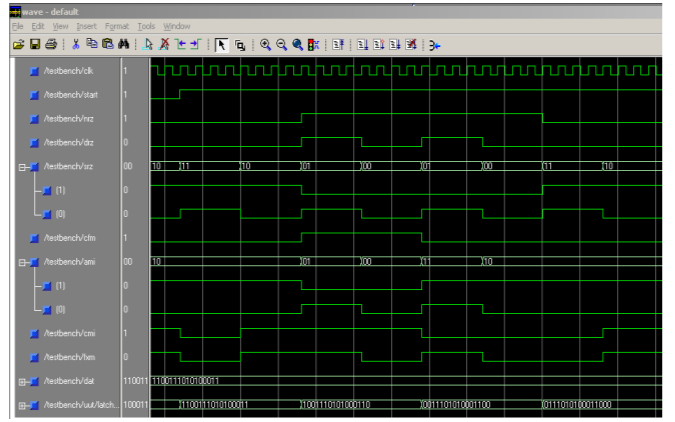

該多功能可變模計數器在QuartusⅡ開發環境下進行了仿真驗證,功能仿真波形如圖4所示,時序仿真波形如圖5所示。

仿真結果分析如下:

(1)clk為時鐘信號,由時鐘信號的上升沿觸發計數;

(2)m為模值輸入端,當其變化時,計數容量相應發生變化;

(3)clr為清零控制端,當其為高電平時清零;

(4)s為置數控制端,當其為高電平時將置數輸入端d的數據加載到輸出端q;

(5)en為使能控制端,當其為高電平時正常計數,當其為低電平時暫停計數;

(6)updn為計數方向控制端,當其為高電平時計數器加法計數,當其為低電平時計數器減法計數。

4 結 語

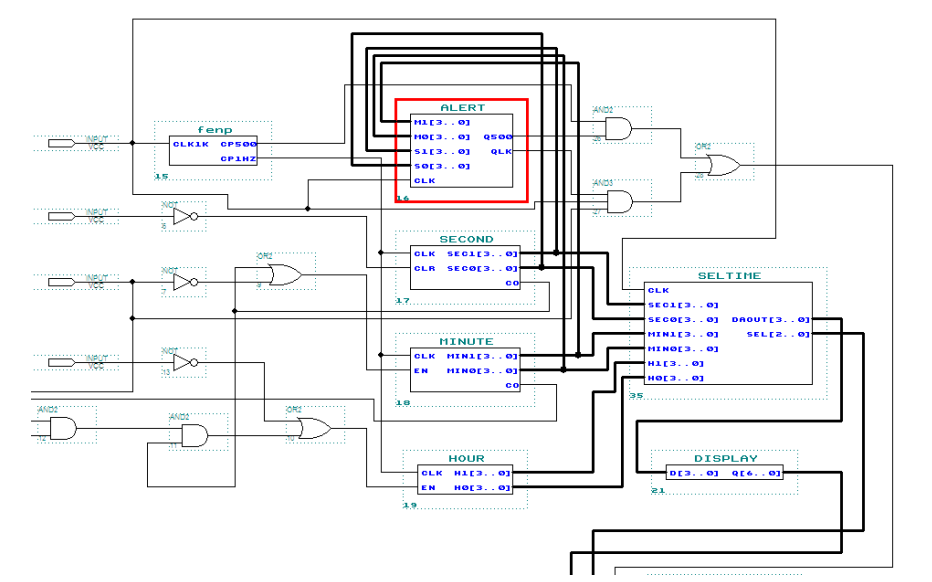

這里所設計的多功能可變模計數器在QuartusⅡ開發環境下進行了仿真驗證后,下載到湖北眾友科技實業股份有限公司的ZY11EDA13BE實驗箱中進行了硬件驗證。該實驗箱使用ACEX1K系列EP1K30QC208芯片作為核心芯片.實驗證明設計正確,功能完整,運行穩定。另外,該設計的多功能可變模計數器可根據需要將模值的最大值由99進一步擴展,獲得更高的計數模值。

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606067 -

cpld

+關注

關注

32文章

1257瀏覽量

169637 -

vhdl

+關注

關注

30文章

817瀏覽量

128346

發布評論請先 登錄

相關推薦

在QuartusⅡ開發環境下怎么用VHDL語言設計可變模功能的計數器?

基于Multisim的計數器設計仿真

基于Proteus的任意進制計數器設計與仿真

采用VHDL預言實現基于Petri網的并行控制器設計并進行仿真驗證

如何使用FPGA進行多功能實驗板的設計與實現

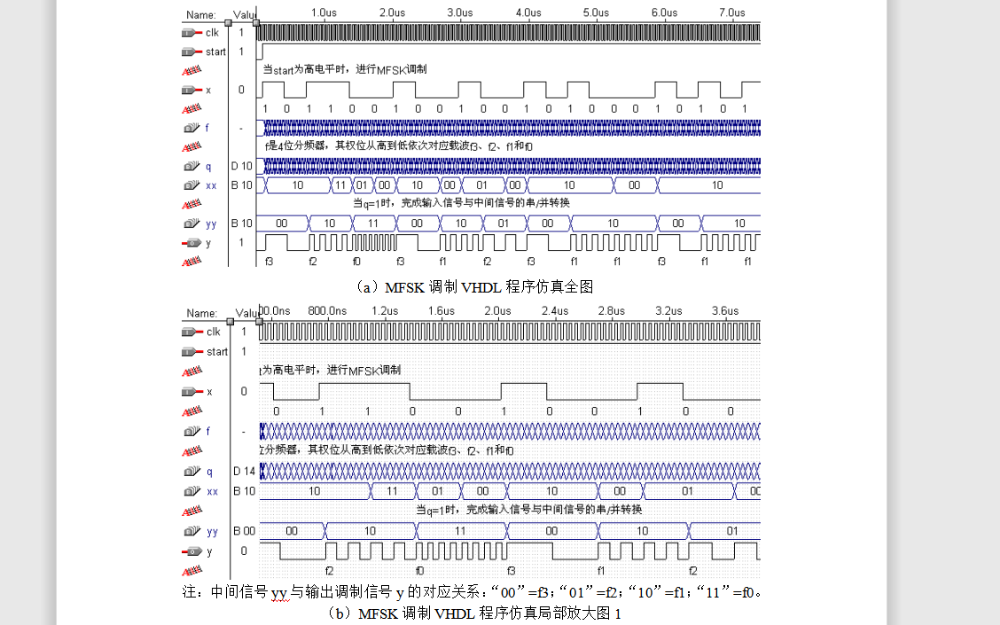

使用VHDL硬件描述語言實現基帶信號的MFSK調制的程序與仿真

采用VHDL語言實現多功能可變模計數器設計并進行仿真驗證

采用VHDL語言實現多功能可變模計數器設計并進行仿真驗證

評論