在便攜式數字衛星通信系統中,為了擴大傳輸容量和提高傳輸效率,滿足同時傳輸幾種業務的需求,通常采用時分復用的方法,將若干個低速數字碼流按一定格式合并成一個高速數據碼流,以便在一條信道中傳輸,使各個業務信號互相不產生干擾,實現此功能的設備就是數字復接系統。

便攜式衛星通信,要求實現平臺集成度高、速度快、功耗小、體積小和成本低。現場可編程門陣列(FPGA) 在結構上由邏輯功能塊排列為陣列,并由可編程的內部連線連接這些功能塊,來實現一定的邏輯功能。特別適合上述要求的產品開發與小批量生產。

FPGA 的開發環境在電路設計階段,可實時地對設計電路進行各種仿真分析,提高電路設計的靈活性和可靠性,特別是還可在成品上直接進行二次開發和功能擴展,靈活且可移植。后期還可以在線對任意一邏輯信號進行實時仿真,該文利用軟件Quartus II 5. 1 和VHDL 硬件語言進行設計和仿真,實現一個基于FPGA 的衛星便攜站的同步數字復接系統的設計。

1 設計和實現

同步數字復分接器完成以下業務的復分接:3 路音頻合計48 kbps 數據; 1 路64 kbps 同步數據;1 路9. 6 kbps 異步數據; 1 路128 kbps LAN 數據; 1 路517. 2 kbps 視頻數據。采用同步、固定時隙分配和按位復接方式的設計方法。

1.1 準同步時延

因為數字復接器與音頻的接口關系最為復雜,所以設計要點著重放到了與音頻接口的處理。

1. 1. 1 音頻接口的乒乓操作

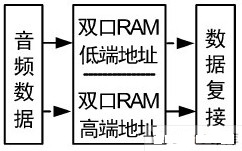

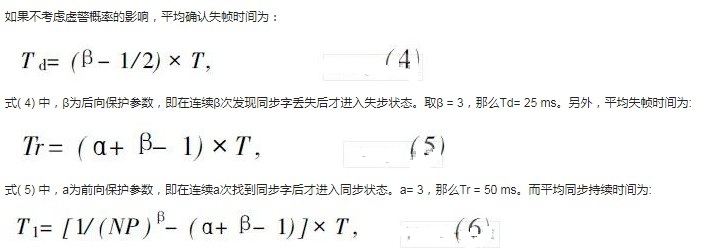

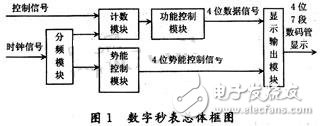

如圖1 所示,采用雙口RAM 完成音頻數據和復分接器的接口。音頻數據接口是一種DSP 總線接口,在第1 個緩沖周期,音頻數據緩存到雙口RAM的低端地址存儲區,同時數據復接單元讀取雙口RAM 的高端地址存儲區的音頻數據; 在第2 個緩沖周期,音頻數據緩存到雙口RAM 的高端地址存儲區,同時數據復接單元讀取雙口RAM 的低端地址存儲區的音頻數據。如此循環,周而復始。

圖1 乒乓操作示意圖

這樣經過緩沖的數據流沒有時間停頓的送到復接器中,屬于一種流水線式處理,完成數據的無縫緩沖和處理,節約緩沖區的空間,達到利用低速模塊處理高速數據流的結果,實現了數據流的并串轉換。

如果音頻數據和復分接器的接口采用傳統的緩存方式,很容易造成復接器讀數據的時候音頻數據還沒有寫到緩存中,很容易造成聲音的“咔咔聲”,采用音頻接口的乒乓操作避免了此問題的產生。

1. 1. 2 提供唇音同步機制

在數字衛星傳輸系統中,有一個獨特的音視頻同步問題,即通常說的唇音同步。由于圖像壓縮編碼所需之信號處理時間一般慢于聲音壓縮編碼所需之信號處理時間,那么在收端將視頻及音頻信號解碼出來后,就會發現音頻比視頻快半拍。通常見到的情況是,或者口動時聽不到聲音,或者口不動時卻有聲音出來,即唇音不同步,給觀眾較差的主觀感覺。為了避免出現這一問題,分接器中提供了唇音同步單元,把音頻數據程序上進行延時,通過調整就可保證接收端的音和視頻同步。

1. 1. 3 解決FPGA 電路設計中的毛刺問題

在FPGA 中當多路信號同時發生跳變的瞬間,往往會出現一些不正確的尖峰信號,這些尖峰信號就是“毛刺”。組合邏輯電路中競爭冒險現象的出現也會出現“毛刺”。它的出現會影響電路工作的穩定性和可靠性,導致數字系統的誤操作和邏輯紊亂。

設計中利用D 觸發器對輸入信號的毛刺不敏感的特點,去除信號中的毛刺,但是只是對信號中發生在非時鐘跳變沿的毛刺信號去除明顯,并且有一定延時。因此設計中盡量采用同步時序電路來實現各個進程模塊的功能,同時對輸入輸出的數據進行高倍時鐘的采樣,達到去除電路中毛刺的目的。

1.2 設計方案

1.2.1 幀結構

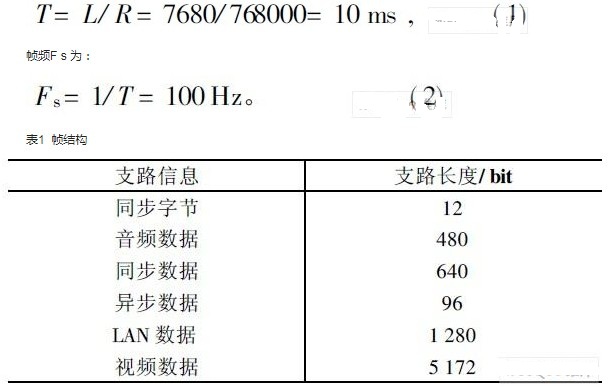

該單元不要求與其他復分接設備互聯互通,所以采用自定義的幀結構。幀頭采用集中幀碼,幀頭固定為12 bits。幀結構如表1 所示。

根據表1 可以計算出每幀的幀長L 為7 680 bit,線路速率R 為768 kbps 時,幀周期T 為:

1. 2. 2 復接器

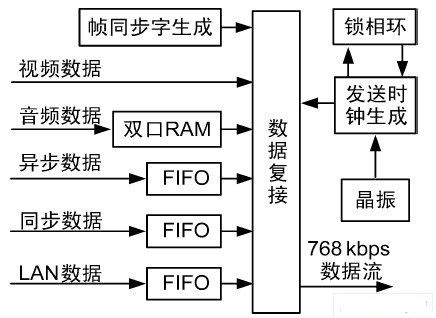

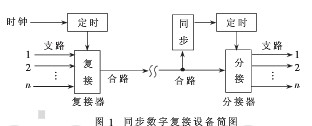

復接器部分負責將各支路信息數據和幀頭合成一路數據流。它由時鐘發送電路、數據接收存貯器、數據緩沖單元和數據復接電路組成。時鐘發送電路產生復接各支路信息數據所需的時隙,時鐘通過使用內部時鐘源或由接收時鐘鎖相得到; 數據接收存貯器為一雙口RAM,用來接收數字音頻數據; 數據緩沖單元用來把同步數據等數據的相位調整到滿足可以進行復接的相位; 數據復接電路將上述數據合成一路線路數據; 復接器的組成框圖如圖2 所示。

圖2 復接器組成框圖

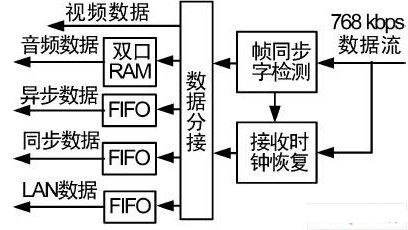

1. 2. 3 分接器

分接器負責將一路數據流分解成各個支路信息數據。它包括數據分接電路、時鐘恢復電路、數據接收存貯器和數據緩沖單元等部分。時鐘恢復電路產生解幀所需的各種時鐘和相應的支路時隙,這些時鐘和接口接收的數據一起送入數據分接電路,搜索幀同步字,當滿足同步規則后判為同步,同時強迫時序與數據幀同步對應,將各支路信息數據分接,并送相應的解碼單元,不同步給出同步/ 失步告警信號;數據接收存貯器為一雙口RAM,用來發送數字音頻數據; 數據緩沖單元用來把分接的同步數據的相位調整到滿足數據接口的相位。復接器的組成框圖如圖3 所示。

圖3 分接器組成框圖

1. 2. 4 幀同步字檢測

對于集中幀同步字方式,幀同步字在數據流中是若干個連續的碼元,占據相鄰的時隙,因此幀碼檢測電路比較簡單,可由位數等于幀碼個數的D 觸發器和與門構成。數據由時鐘逐位打入D 觸發器中,一旦12 位幀碼都移入D 觸發器中,即12 個D 觸發器輸出為幀同步字,則與門輸出一個脈沖,否則與門沒有輸出。為防止假同步,連續3 次搜索到幀同步字才認為設備同步,否則重新搜索。當信道誤碼率較高時,為避免設備頻繁失步,當連續3 次失步才認為設備失步。

采用上述方法既可以防止假鎖,又可以避免啟動不必要的同步搜索,使設備工作更加穩定可靠。

所有以上功能除接口轉換及時鐘鎖相外,全部使用FPGA 器件,采用硬件設計語言實現。并按功能模塊化設計,具有很好的重用性,可以方便地進行移植。

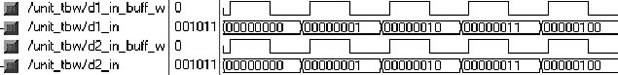

1. 2. 5 仿真與實現

該復接器是在Altera 公司的QuartusII5. 1 作為硬件開發平臺,完全采用VHDL 硬件描述語言編寫,并在QuartusII5. 1 的開發環境下進行時序仿真,系統仿真波形良好,除了允許范圍內的信號延遲外,能準確實現數字信號的復接和分接,經過編譯下載到可編程器件中,程序已通過了綜合實驗,獲得很好的效果,滿足了工程的需要。

2 系統同步性能分析

在傳輸過程中,由于信道噪聲的影響,不可避免地將在傳輸碼流中引入誤碼,從而導致系統同步的丟失。同步丟失是一個非常嚴重的問題,它將導致主觀質量的嚴重下降,甚至使得整個系統不能正常工作。因此,復分接系統同步性能的好壞,是影響整個系統性能的關鍵環節。

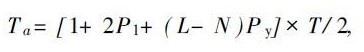

在發送端,復分接系統輸出數據流幀長為L =7 680 bit。在每幀的起始,是固定數值的同步幀頭,碼長為N = 12 bit,根據文獻[ 3] ,有平均搜捕時間:

式( 3) 中,P 1 為同步字上的虛漏概率; Py 為非同步字上的虛警概率; T 為數據幀周期。如果信道的平均比特誤碼率,傳送流的速率R =768 kbit / s,那么P1 = NP = 0. 001 2,P y = 2-12=0. 000 2, T = L / R, 于是Ta = 12. 68 ms。

所以T1= 1 607 h。從上面的分析中可以看出復分接系統即使在不進行誤碼保護的情況下,也能在較短的時間內確認失幀,并很快搜捕到同步; 同時在同步狀態保持很長的時間。因此,該復分接系統具有較好的同步性能,在一定的誤碼保護措施下能夠滿足實際要求。

3 結束語

設計的數字復接系統的各個部分,都可以在FPGA 芯片上用VHDL 編程實現。整個復分接系統功能就可以集成在一塊芯片上,既節省了硬件資源,減少外部走線,簡化了系統,而且該設計便于擴展,方便反復編寫和修改程序,只需修改FPGA 中相應控制參數和外接的監控信息就可以實現速率可變和幀結構可變的復接與分接。實驗表明,該系統在FDMA 便攜式衛星傳輸平臺中起到了重要作用,可提高信道的利用率和傳輸容量。

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606067 -

衛星

+關注

關注

18文章

1722瀏覽量

67343 -

vhdl

+關注

關注

30文章

817瀏覽量

128346

發布評論請先 登錄

相關推薦

基于FPGA 的光電經緯儀中低速數字信號復接設計

采用CPLD/FPGA的VHDL語言電路優化原理設計

基于VHDL和FPGA的非對稱同步FIFO設計實現

基于FPGA的PCM30/32路系統信號同步數字復接設計

基于FPGA和數字復接技術實現數字分接與復接設計

采用VHDL語言與FPGA實現衛星同步數字復接系統的設計

采用VHDL語言與FPGA實現衛星同步數字復接系統的設計

評論