先提一下位寬的概念,對于具體器件而言,它的位寬是一定的,所謂位寬,指的是“讀/寫操作時,最小的數(shù)據(jù)單元”──別說最小單元是“位”,一般設(shè)備上沒有單獨的“位操作”,修改位時通過把整個字節(jié)、字或雙字讀出來、修改,再回寫。AM29L800BB這種nor flash位寬是16位。K4S561632C這種SDRAM位寬是32位。

對于CPU來說,一個地址對應(yīng)的是一個字節(jié)(8位),也就是說CPU的地址線(A0~A20)對應(yīng)的最小數(shù)據(jù)單元是字節(jié)。

這里需要注意的是,不要把“外設(shè)的位寬”和“CPU的位數(shù)”這兩個概念混淆了。外設(shè)的位寬是讀寫外設(shè)的最小數(shù)據(jù)單元,CPU位數(shù)是CPU可以一次處理的字節(jié)數(shù),32位CPU可以一次處理4字節(jié)數(shù)據(jù)。

好了,相信你也已經(jīng)發(fā)現(xiàn)問題了吧。既然CPU最小數(shù)據(jù)單元是8位,flash位寬是16位,那在我們寫程序時會特意進行16位操作嗎?顯然不會,我們寫代碼時,可不管外設(shè)到底是多少位。這是如何實現(xiàn)的呢?原因在于存儲控制器(Memory Controller)這個中間層。

存儲控制器根據(jù)NOR FLASH的位寬,每次總是讀/寫16位數(shù)據(jù)。

以讀操作為例:

CPU進行8位操作時,它選擇其中的8位返回給CPU;

CPU進行16位操作時,它直接把這16位數(shù)據(jù)返回給CPU;

CPU進行32位操作時,它發(fā)起2次讀/寫,把結(jié)果組合成32位返回給CPU。

現(xiàn)在的連線是:CPU的(ADDR1-ADDR20)接到 16位的NOR FLASH (A0-A19),即CPU的ADDR0不接──這說明:不管ADDR0是0還是1,NOR FLASH接收到的地址是一樣的。

CPU發(fā)出地址0bxxxxxxxxx0、0bxxxxxxxxx1時,NOR FLASH看到的都是0bxxxxxxxxx,返回給存儲控制器的都是同一個16位數(shù)據(jù)。再由Memory Controller選擇其中的低8位或高8位給CPU。

存儲控制器會做以下事情:

軟件要讀取地址0上的8位數(shù)據(jù)時,硬件是這樣進行的:

① Memory Controller發(fā)出0b000000000000000000000的地址信號,NOR FLASH的A0-A19線上的信號是:0b00000000000000000000

② NOR FLASH在數(shù)據(jù)總線D0~D15上提供一個16位的“最小數(shù)據(jù)單元”的數(shù)據(jù);

③ 存儲控制器讀入16位數(shù)據(jù);

④ 存儲控制器把16位數(shù)據(jù)的低8位返回給CPU,就得到了一個8位數(shù)據(jù)。

軟件要讀取地址1上的8位數(shù)據(jù)時,硬件是這樣進行的:

① 存儲控制器發(fā)出0b000000000000000000001的地址信號,NOR FLASH的A0-A19線上的信號是:

0b00000000000000000000

② NOR FLASH在數(shù)據(jù)總線D0~D15上提供一個16位的數(shù)據(jù),這是NOR FLASH中的第1個“最小數(shù)據(jù)單元”

③ 存儲控制器讀入這個16位數(shù)據(jù)

④ 存儲控制器把這個16位數(shù)據(jù)的高8位(注意,前面的低8位)返回給CPU,這就是一個8位數(shù)據(jù)。

所以:

外設(shè)位寬是8時,CPU的A0~AXX與外設(shè)的A0~AXX直接相連

外設(shè)位寬是16時,CPU的A1~AXX與外設(shè)的A0~AYY直接相連,表示不管CPU的A0是0還是1,外設(shè)看到的都是同一個地址,

對應(yīng)16位的數(shù)據(jù),存儲控制器對數(shù)據(jù)進行選擇或組合,再提供給CPU。

外設(shè)位寬是32時,CPU的A2~AXX與外設(shè)的A0~AZZ直接相連,表示不管CPU的A0A1是00,01,10還是11,外設(shè)看到的都是

同一個地址,對應(yīng)32位的數(shù)據(jù),“Memory Controller”對數(shù)據(jù)進行選擇或組合,再提供給CPU。

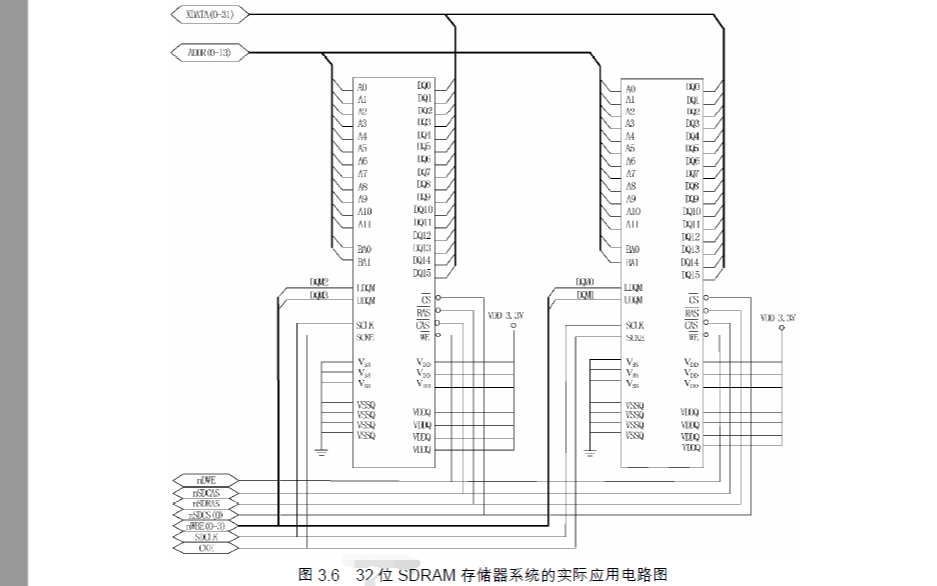

經(jīng)過以上分析,我們應(yīng)該知道了,為什么地址線要偏移幾位了。同樣的SDRAM因為是32位寬的,所以偏移2位。那為什么SDRAM要連ADDR2~ADDR14和ADDR24、ADDR25呢?同樣,我們先看下SDRAM的基本知識。

SDRAM的連接方式與上面FLASH的類似,但是要比其復雜些。因為SDRAM內(nèi)部是一個存儲陣列,如同表格一樣將數(shù)據(jù)填進去,因此得先指定一個行,再指定一個列,才可以找到所需的單元格。這個表格被稱為邏輯Bank(L-Bank),一般有4個Bank。可以想象,對SDRAM的訪問分為以下4個步驟:

① CPU發(fā)出片選信號nSCS0有效,選中SDRAM芯片;

② 選擇L-Bank,最開始說的ADDR24和ADDR25即此作用;

③ 進行統(tǒng)一行/列尋址;

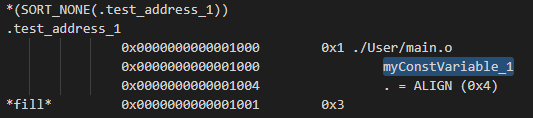

根據(jù)SDRAM芯片的列地址線數(shù)目設(shè)置CPU相關(guān)存儲器后,CPU就會從32位的地址中自動分出L-Bank選擇信號、行地址信號、列地址信號,然后先發(fā)出行地址信號、列地址信號。L-Bank選擇信號在發(fā)出行地址信號的同時發(fā)出,并維持到列地址信號結(jié)束。在本例中,行地址、列地址公用ADDR2~ADDR14。K4S561632行地址13,列地址9,所以nSRAS信號有效時,ADDR2~ADDR14發(fā)出行地址,對應(yīng)32位地址空間的bit[23:11];nSCAS有效時,ADDR2~ADDR10發(fā)出列地址,對應(yīng)32位地址空間的bit[10:2]。而bank選擇位對應(yīng)bit[25:24]。這樣就構(gòu)成了64M地址空間,及30000000到33ffffff。

-

ARM

+關(guān)注

關(guān)注

134文章

9169瀏覽量

369243 -

SDRAM

+關(guān)注

關(guān)注

7文章

430瀏覽量

55371 -

存儲器

+關(guān)注

關(guān)注

38文章

7528瀏覽量

164350 -

cpu

+關(guān)注

關(guān)注

68文章

10905瀏覽量

213032

發(fā)布評論請先 登錄

相關(guān)推薦

#硬聲創(chuàng)作季 #ARM ARM體系結(jié)構(gòu)與接口技術(shù)-07 FS-MP1A外設(shè)連接

STM32F429Disco SDRAM簡單讀寫操作

外設(shè)位寬為8、16、32時,CPU與外設(shè)之間地址線的連接方法

關(guān)于SDRAM的地址線復用

使用了C6713外設(shè)連接flash,sdram,看門狗芯片及FPGA等器件沒有燒錄的原因是什么?

有關(guān)arm裸機SDRAM的相關(guān)知識介紹

arm9片類flash啟動需要初始化sdram嗎

ARM存儲器

指定了SDRAM卻燒寫到了Nand flash的詳細分析

一文看懂ARM里的RAM和SDRAM有什么區(qū)別

SDRAM存儲器模塊的簡介

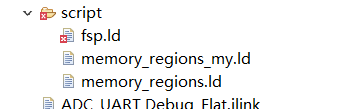

RISC-V MCU將常量定義到指定的Flash地址

分析ARM外設(shè)flash及SDRAM的地址連接

分析ARM外設(shè)flash及SDRAM的地址連接

評論