初識Verilog描述-1

“Verilog不同于C,Python,JAVA等軟件語言,Verilog是以數字電路知識為背景支撐,以對數字電路系統進行描述的一門語言。因此用Verilog描述數字電路,必須要有數字電路知識為背景支撐。否則描述出來的電路性能將會很差。本篇我們先了解一下最基本的Verilog對數字電路描述的方法與代碼風格,具體語法細節在這不做過多解釋。”

在了解Verilog基本構成之前,先要了解數字電路里面有什么元素需要被描述。

如下圖所示,為一個實例電路外部原理圖:

從外部看一個電路需要描述的元素如下:

電路名字

輸入端口以及位寬

輸出端口以及位寬

端口描述有兩種方式。

以上圖為例:

(1)

module share_1(

clk,

rst_n,

a,

b,

data_out

);

input clk;

input rst_n;

input[7:0] a;

input[7:0] b;

output[8:0] data_out;

(2)

module share_1(

input clk,

input rst_n,

input [7:0] a,

input [7:0] b,

output [8:0] data_out

);

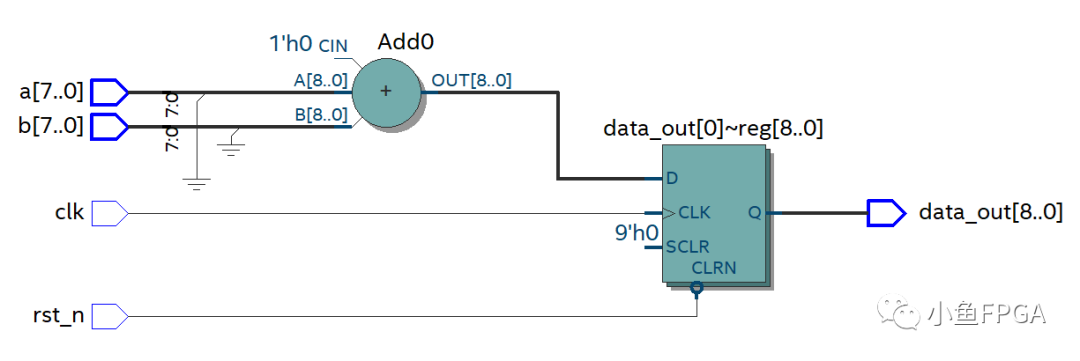

下圖為其內部電路結構:

電路內部需要描述元素有:

信號的類型:reg型(所有在always電路里面將要做改變的信號),wire型(電路信號連線)

如上例電路:輸入信號本來就為電路信號連線,且在端口聲明中已經聲明,無需再做wire 聲明。

輸出信號data_out是寄存器的輸出,因此聲明為: reg[8:0] data_out;

節點信號add_out(對應電路上的OUT),為加法器的輸出。如果加法器是用always塊實現的,如下:

always @( * ) begin

add_out = a+b;

end

則聲明為reg型: reg[8:0] add_out;

如果加法器是用assign語句實現的,如下:

assign add_out = a+b;

則聲明為wire型: wire[8:0] add_out;

注意:所有聲明必須帶上位寬,否則系統工具將其默認為單位寬,如上信號add_out為9位寬,因此聲明為 reg [8:0] add_out;

組合邏輯電路: 可以利用 assign 或者 always @(*) 語句描述。一般復雜的組合邏輯電路利用 always @(*)語句塊描述。如上加法器的實現既可以用always語句實現,也可以利用assign語句實現。

寄存器(有如下幾種常用的不同的寄存器模型):

(1) 時鐘信號上升沿驅動,復位信號低電平有效,與時鐘異步復位:

always @( posedge clk or negedge rst_n ) begin

if( !rst_n )

data_out <= 8h00;

else

data_out <= data_in;

end

(2)時鐘信號上升沿驅動,復位信號高電平有效,與時鐘異步復位:

always @( posedge clk or posedge rst ) begin

if( rst )

data_out <= 8h00;

else

data_out <= data_in;

end

(3) 時鐘信號下降沿驅動,復位信號高電平有效,與時鐘同步復位:

always @( negedge clk ) begin

if( rst_n )

data_out <= 8h00;

else

data_out <= data_in;

end

(4)時鐘信號上升沿驅動,復位信號低電平有效,與時鐘同步復位,并且帶有高電平使能信號:

always @( posedge clk ) begin

if( !rst_n )

data_out <= 8h00;

else if( enable )

data_out <= data_in;

else

data_out <= data_out;

end

給出兩種完整的描述方式,大家自行體會,電路功能為帶寄存器輸出的8位無符號數加法器:

(1)

module share_1(

clk,

rst_n,

a,

b,

data_out

);

input clk;

input rst_n;

input[7:0] a;

input[7:0] b;

output[8:0] data_out;

reg[8:0] data_out;

wire[8:0] add_out;

assign add_out = a+b;

always @( posedge clk or negedge rst_n ) begin

if( !rst_n )

data_out <= 9h00;? ? ? ? ? ? ? ? ? ? ? ? ??

else

data_out <= add_out;? ? ? ? ? ? ? ? ? ? ? ??

end

endmodule

(2)

module share_1(

input clk,

input rst_n,

input [7:0] a,

input [7:0] b,

output [8:0] data_out

);

reg[8:0] data_out ;

reg[8:0] add_out;

always @( * ) begin

add_out = a+b;

end

always @( posedge clk or negedge rst_n ) begin

if( !rst_n )

data_out <= 9h00;? ? ? ? ? ? ? ? ? ? ? ??

else

data_out <= add_out;? ? ? ? ? ? ? ? ? ? ??

end

endmodule

注:這里只是帶著大家從電路入手,宏觀的了解一下Verilog描述數字電路的結構與注意事項,具體語法可自行學習。

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42709 -

Verilog

+關注

關注

28文章

1351瀏覽量

110391 -

數字電路

+關注

關注

193文章

1629瀏覽量

80822

原文標題:初識Verilog描述-1

文章出處:【微信號:LF-FPGA,微信公眾號:小魚FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

數字電路和模擬電路的工作各有何特點?

數字電路的應用介紹

新編數字電路與數字邏輯

《VHDL與數字電路設計》

什么是模擬電路 什么是數字電路

VHDL概述及在描述數字電路時的結構

數字電路里面有什么元素需要被描述?

數字電路里面有什么元素需要被描述?

評論