前面在介紹PCIe物理層邏輯子層的文章中,有提到過彈性緩存(Elastic Buffer,又稱為CTC Buffer或者Synchronization Buffer)。其本質上是一種FIFO,主要用于解決跨時鐘域問題。當然,PCIe的彈性緩存還用于補償時鐘誤差(Compensate for the clock differences)。實際上,除了PCIe,彈性緩存還廣泛應用于其它的高速串行接口——USB、InfiniBand、Fibre Channel、Gigabit Ethernet等基于SerDes的應用。

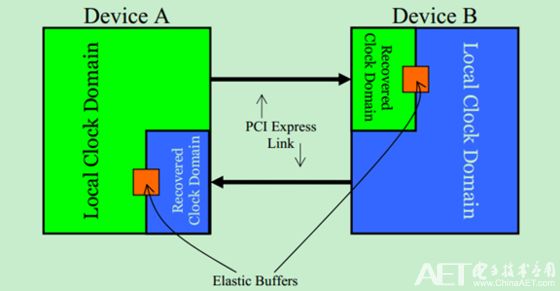

由于PCIe采用的基于8b/10b的嵌入式源同步時鐘,接收端存在兩個時鐘域:一個是通過CDR從數據流中解析出來的時鐘,用該時鐘對數據進行采樣;另一個是本地時鐘域,用于其他的邏輯的。借助彈性緩存(FIFO),可以實現數據在這兩個時鐘域的轉換。

以PCIe Gen1為例,鏈路上的數據速率為2.5Gbps。但實際上,任何晶振(或者其他頻率發生器)都是有誤差的,PCIe Spec允許的誤差范圍為±300ppm(Parts Per Million)。即,鏈路上實際的頻率范圍為2.49925GHz~2.50075GHz。借助彈性緩存,通過刪除或者插入SKP Ordered Set可以消除鏈路頻率誤差的影響。如下圖所示:

需要注意的是PCIe Spec并沒有規定彈性緩存的具體位置,設計者可以將彈性緩存放在8b/10b解碼器之前,也可以把彈性緩存放在8b/10b解碼器之后。不過,Mindshare的建議是將彈性緩存放置于8b/10b解碼器之前的。

當本地時鐘域的時鐘(Local Clock)的速度比數據流通過CDR解析出的時鐘(Recovered Clock)的時鐘要快時,且彈性緩存即將被讀空之前,可以向SKP Ordered Set中插入1~2個SKP。如下圖所示:

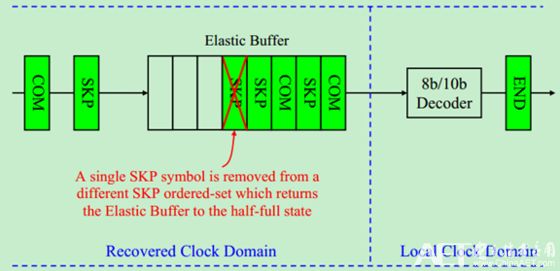

當本地時鐘域的時鐘(Local Clock)的速度比數據流通過CDR解析出的時鐘(Recovered Clock)的時鐘要慢時,且彈性緩存即將溢出之前,可以從SKP Ordered Set中移除1~2個SKP。如下圖所示:

需要特別注意的是,Intel提出的PIPE規范(并非PCI-SIG強制的規范,具體參考前面關于PIPE的文章)中,只允許每次從一個SKP Ordered Set中插入或者移除一個SKP。如果需要插入或者移除兩個SKP,則需要對兩個SKP Ordered Set進行操作。如下圖所示:

-

解碼器

+關注

關注

9文章

1147瀏覽量

40933 -

PCIe

+關注

關注

15文章

1260瀏覽量

83193

原文標題:【博文連載】PCIe掃盲——彈性緩存(Elastic Buffer,or CTC Buffer)

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCIe彈性緩存主要用于解決跨時鐘域問題

PCIe彈性緩存主要用于解決跨時鐘域問題

評論