使用vivado也能學(xué)習(xí)Verilog描述,你造嗎

前幾天搞數(shù)學(xué)建模好幾天沒更新文章了,大家沒忘了我吧,趕緊發(fā)一篇。

在有了電路設(shè)計(jì)的概念的之后我們可能苦于不能靈活運(yùn)用Verilog去對(duì)電路進(jìn)行描述。然后苦于到處找資料,這里我們告訴你們一個(gè)非常好的Verilog實(shí)例描述學(xué)習(xí)工具,Vivado。

不知情者:呀,Vivado不是FPGA的設(shè)計(jì)EDA工具嘛?用它還能來來學(xué)習(xí)Verilog描述,你確定?

答:是的,你沒聽錯(cuò),可以的。這個(gè)Vivado工具就是這么體貼。

1. 打開Vivado工具,隨便先新建一個(gè)工程。然后進(jìn)入下頁面。

2. 在界面最上面一行菜單欄找到 “Tools”,點(diǎn)擊 Tools-> Language Templates

3. 點(diǎn)擊 Tools-> Language Templates后,出現(xiàn)如下界面。可以看到,這里有Verilog,VHDL, systemVerilog, XDC,Debug的語言模板。這里我們先只看Verilog。

4. 將上圖中的Verilog欄展開,在Synthesis Constructs欄就是我們可綜合的常見Verilog描述。可以看到 Always ,Conditional里的case,條件選擇賦值語句,if-else等常見的語法模型他都列出來了。在Coding Example里面有一些基礎(chǔ)的電路模塊的Verilog描述示例。

5. 展開Coding Example,可看到基礎(chǔ)的電路,如累加器,基礎(chǔ)算術(shù)電路,邏輯門,輸入輸出端口,比較器,計(jì)數(shù)器,解碼器,常見的數(shù)字信號(hào)處理電路,譯碼器,寄存器(flip flops),邏輯移位器,Misc(有七段式數(shù)碼管驅(qū)動(dòng),同步電路,防抖電路, 開漏輸出端口,脈沖調(diào)制電路),多路選擇器,RAM,ROM,移位寄存器,狀態(tài)機(jī),三態(tài)緩沖器等等的Verilog描述示例。

6. 在Example Module里面有更多的設(shè)計(jì)示例,如一些算法電路的設(shè)計(jì)。有了一些基礎(chǔ)之后,就可以把這里的設(shè)計(jì)示例都看看。

對(duì)于初學(xué)者可以好好利用這個(gè)。把上面這些示例模板和示例設(shè)計(jì)學(xué)習(xí)仿真一遍。主要是將Verilog描述與電路對(duì)應(yīng)起來,在Vivado里面可以使用Schematic,把Verilog描述的電路原理圖顯示出來。后面我們也會(huì)以這個(gè)為資料發(fā)一些文章。

原文標(biāo)題:使用vivado也能學(xué)習(xí)Verilog設(shè)計(jì),你造嗎

文章出處:【微信號(hào):LF-FPGA,微信公眾號(hào):小魚FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

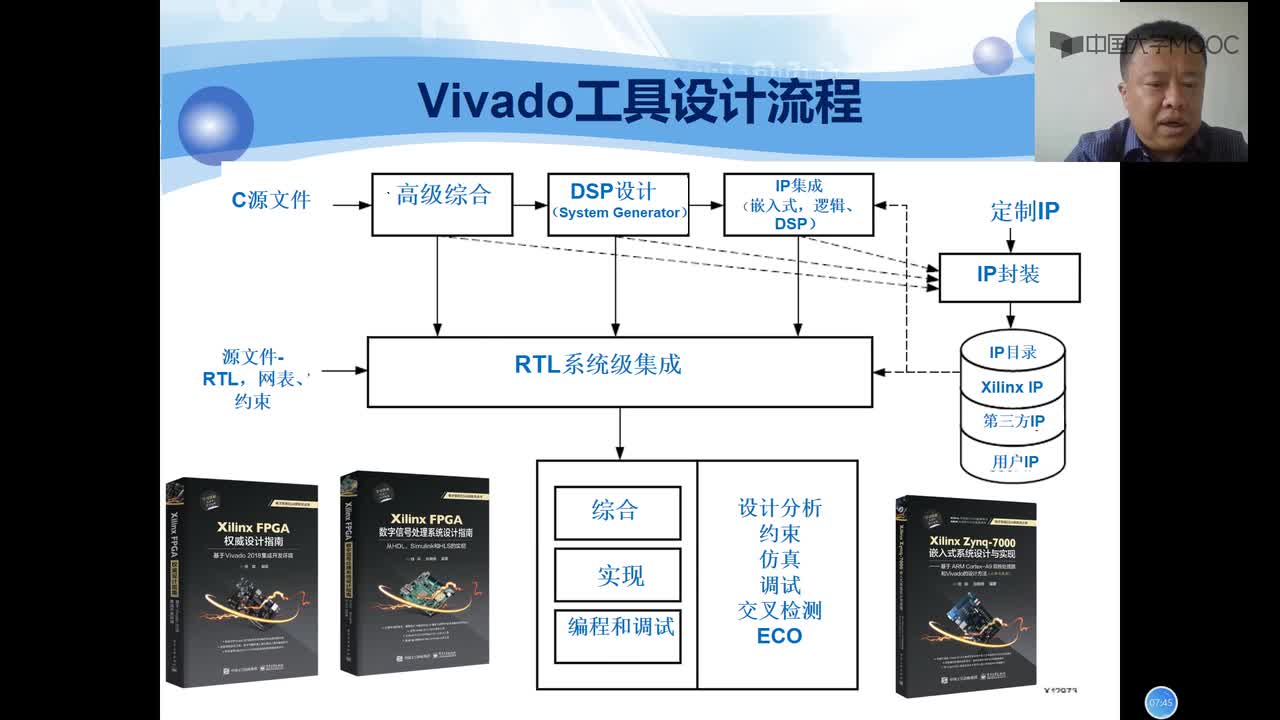

#硬聲創(chuàng)作季 #EDA EDA原理及應(yīng)用-04.02 Vivado工具設(shè)計(jì)流程-1

#硬聲創(chuàng)作季 #EDA EDA原理及應(yīng)用-04.02 Vivado工具設(shè)計(jì)流程-2

EDA工具

EDA Tools in FPGA

基于多種EDA工具的FPGA設(shè)計(jì)

多種EDA工具的FPGA協(xié)同設(shè)計(jì)

基于多種EDA工具的FPGA設(shè)計(jì)

多種EDA工具的FPGA設(shè)計(jì)方案

使用VIVADO對(duì)7系列FPGA的高效設(shè)計(jì)心得

賽靈思推出首個(gè)基于機(jī)器學(xué)習(xí)優(yōu)化算法 FPGA EDA 工具套件

賽靈思Vivado ML版優(yōu)化應(yīng)用設(shè)計(jì)

【FPGA Vivado】基于 FPGA Vivado 的流水燈樣例設(shè)計(jì)

智多晶EDA工具HqFpga軟件實(shí)用小功能

Vivado不是FPGA的設(shè)計(jì)EDA工具嘛?

Vivado不是FPGA的設(shè)計(jì)EDA工具嘛?

評(píng)論