本文闡述了一種芯片時鐘與功耗管理控制器的工作原理,進行了模塊劃分,采用硬件描述語言實現(xiàn)了設計,并利用Synopsys公司的EDA工具進行了仿真和綜合。該控制器已成功應用于東南大學ASIC中心研制的嵌入式處理器芯片Garfield4Plus中,并通過了實際的流片和測試。 在SoC芯片設計中,功耗是微處理器芯片是否成功的重要標準之一。同時,作為一個龐大的數(shù)字電路系統(tǒng),處理器芯片的時鐘架構及其控制也將變得尤為重要,將直接影響到芯片的功耗。基于以上考慮,整個芯片的時鐘和功耗必須得到統(tǒng)一的管理和控制。包括核與總線在內(nèi)的各功能模塊的時鐘應當能夠跟據(jù)具體工作需要自由開關,以保證芯片盡可能地減小功耗。因此,處理器中需要一個專門的時鐘與功耗管理控制器(以下統(tǒng)稱PMC)來實現(xiàn)這些功能。PMC控制著整個芯片的工作模式和系統(tǒng)時鐘頻率,其穩(wěn)定和完善將影響整個芯片的性能。

本文通過對PMC工作原理的分析確定了設計的總體結構并進行了具體的模塊劃分,使用基于硬件描述語言的邏輯綜合方式進行了設計實現(xiàn),并成功應用于東南大學ASIC工程中心研制的嵌入式處理器芯片Garfield4Plus中,通過了實際的流片和測試。

PMC功能描述

PMC負責管理整個芯片工作模式的切換和系統(tǒng)時鐘頻率的設定,并負責管理芯片上各功能模塊的時鐘信號和復位信號。通過設定PMC的功能寄存器,可以控制芯片在SLOW、NORMAL、IDLE、SLEEP四種工作模式間進行切換。

系統(tǒng)啟動后默認工作在SLOW模式下,時鐘頻率較低,系統(tǒng)時鐘由外部晶振直接提供,并且可以通過設置PMC相關控制寄存器,得到分頻后更低速的時鐘。

NORMAL模式是系統(tǒng)最常用的正常工作模式,系統(tǒng)工作在較高的頻率上。外部晶振時鐘通過DPLL數(shù)字鎖相環(huán)倍頻后,還可以再次被分頻,得到一個可選頻率范圍較寬的高速時鐘。數(shù)字鎖相環(huán)倍頻值和穩(wěn)定時間等參數(shù)可以通過PMC進行設置。

當內(nèi)核空閑時可以設置系統(tǒng)進入IDLE模式。當總線也空閑時,內(nèi)核時鐘將被關閉,同時停止對外部存儲設備的操作,可以大大減小系統(tǒng)功耗。這種模式可以被各種內(nèi)外部中斷信號喚醒,喚醒后的系統(tǒng)將恢復到進入此狀態(tài)之前的工作模式繼續(xù)工作。

如果系統(tǒng)當前工作全部完成,整個系統(tǒng)都空閑的時候,可以設置系統(tǒng)進入SLEEP模式。PMC將會關閉除實時控制模塊RTC以外的所有模塊,系統(tǒng)功耗降低到最小。系統(tǒng)將會等待外部喚醒信號或RTC的定時喚醒信號來恢復系統(tǒng)時鐘。被喚醒的系統(tǒng)將會首先進入SLOW模式。為了確保實現(xiàn)系統(tǒng)的喚醒,RTC和系統(tǒng)時鐘喚醒模塊使用獨立的電源和晶振。

PMC還可以自由控制各功能模塊時鐘的開關。在正常的工作模式下,可以關閉暫時不用的模塊以減小系統(tǒng)的功耗。另外,PMC還管理系統(tǒng)的復位信號并實現(xiàn)軟件復位功能。

模塊劃分及實現(xiàn)

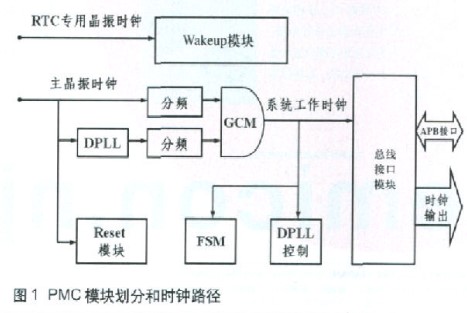

根據(jù)以上對于PMC工作原理和欲實現(xiàn)功能的分析,可將PMC劃分為6個功能模塊:PMC控制器狀態(tài)機(FSM)、數(shù)字鎖相環(huán)控制器(DPLL控制)、時鐘分頻選擇模塊(包括兩個時鐘分頻器和一個無毛刺時鐘切換專用電路GCM)、復位信號控制模塊(Reset)、系統(tǒng)時鐘喚醒模塊(Wakeup)和總線接口模塊,如圖1所示。另外,數(shù)字鎖相環(huán)DPLL為硬件宏模塊,其性能經(jīng)過專門的調試和驗證以保證符合使用要求;GCM用于保證時鐘切換時電路能夠穩(wěn)定工作。

從圖1中還可以清晰看出PMC的時鐘結構。Wakeup模塊使用RTC的專用晶振時鐘,以保證主時鐘關閉后還能正常工作。Reset模塊使用主晶振時鐘。主晶振時鐘經(jīng)過可選分頻得到較慢的時鐘,同時主晶振時鐘經(jīng)過DPLL倍頻,再經(jīng)過可選分頻得到較快的時鐘。兩路時鐘經(jīng)過GCM的平穩(wěn)切換可獲得整個系統(tǒng)所使用的工作時鐘,該時鐘將會分別提供給內(nèi)核、總線和各功能模塊(包括PMC自身的控制和接口模塊)。

PMC控制器狀態(tài)機

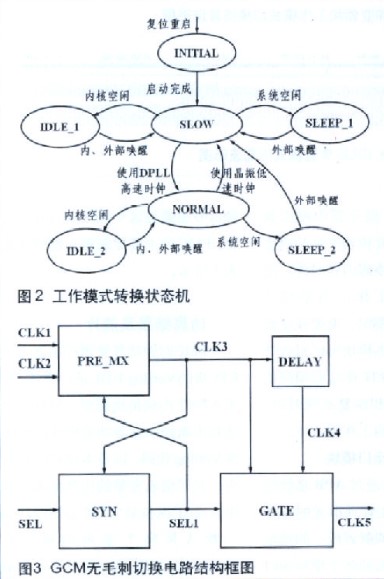

PMC控制器狀態(tài)機的功能是決定系統(tǒng)的工作狀態(tài)變化,并根據(jù)所處工作狀態(tài)輸出控制信號以及與其它模塊的握手信號。此模塊是整個PMC的控制核心,它可以分析軟件命令,根據(jù)軟件命令改變系統(tǒng)當前的工作模式,并收集總線、存儲器、中斷控制器等其他功能模塊的工作狀態(tài)信息;再根據(jù)這些信息控制工作模式的改變,輸出包括開啟晶振時鐘、開啟數(shù)字鎖相環(huán)、時鐘源選擇、SDRAM自刷新等控制信號,以及與總線、中斷控制器等模塊的握手信號。系統(tǒng)工作模式轉換的狀態(tài)機如圖2所示。

數(shù)字鎖相環(huán)控制器

數(shù)字鎖相環(huán)控制器負責根據(jù)PMC的相關控制寄存器配置數(shù)字鎖相環(huán)DPLL,并通過硬件計數(shù)實現(xiàn)用戶設定的穩(wěn)定過渡時間,以保證DPLL有足夠的穩(wěn)定時間來鎖定所設置的工作頻率。控制器狀態(tài)機發(fā)出的時鐘選擇命令和用戶發(fā)出的頻率重配命令都要經(jīng)過此模塊的管理,以保證切換過程中的時鐘穩(wěn)定。

時鐘分頻選擇模塊

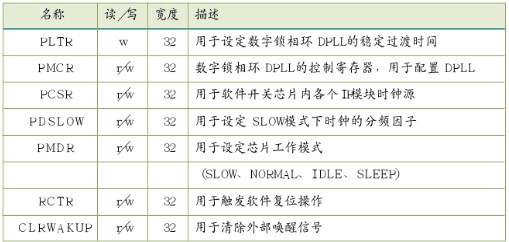

時鐘分頻選擇模塊負責選擇和產(chǎn)生整個系統(tǒng)工作所需的時鐘信號。時鐘的可選范圍和時鐘切換的穩(wěn)定,對于 PMC和整個芯片都十分重要。本文采用2MHz“5MHz的主晶振時鐘和經(jīng)過DPLL倍頻后的100MHz”300MHz時鐘作為時鐘源,再經(jīng)過多種倍率的可選分頻,最終獲得一個比較寬的可選時鐘范圍。為了提高時鐘切換的穩(wěn)定性,還專門設計了一種無毛刺時鐘切換電路GCM(專利電路),可以在三個周期之內(nèi)平穩(wěn)切換兩路各種周期差異的時鐘,并同時改善輸出時鐘的質量。在本設計中,GCM用以實現(xiàn)晶振和DPLL兩路時鐘的平穩(wěn)切換。

GCM的原理框圖如圖3所示。用普通二選一電路(PRE_MX)初步切換得到的時鐘CLK3同步外界輸入的時鐘選擇信號SEL;得到的同步選擇信號SEL1實際控制時鐘的切換,同時SEL1再經(jīng)過進一步同步得到屏蔽殘缺周期的門控信號;最后用門控信號去除時鐘切換中的不穩(wěn)定部分,得到平穩(wěn)的時鐘輸出。

復位信號控制模塊

復位信號控制模塊負責接收外部復位信號和軟件復位信號,并按照工作時序的需要,分別向芯片的各個功能模塊發(fā)出復位信號。可以向某些對復位有特定時序和順序要求的模塊單獨發(fā)送復位信號。并且可以區(qū)分軟、硬件復位,對不同的模塊集合進行復位。

系統(tǒng)時鐘喚醒模塊

系統(tǒng)時鐘喚醒模塊負責恢復關閉的系統(tǒng)時鐘,并保證時鐘穩(wěn)定可用。在系統(tǒng)從節(jié)能模式(IDLE或SLEEP)恢復到正常工作模式(NORMAL或SLOW)的過程中,系統(tǒng)必須將已關閉的時鐘恢復到正常穩(wěn)定的狀態(tài)。當系統(tǒng)從IDLE模式下喚醒時,需要恢復內(nèi)核的時鐘。本模塊可以接收外部的喚醒信號形成一個喚醒中斷,提交到中斷控制器,這與其他所有模塊產(chǎn)生的內(nèi)部中斷一樣,可以喚醒內(nèi)核時鐘,使系統(tǒng)恢復正常工作。當系統(tǒng)從SLEEP模式下喚醒時,需要恢復整個系統(tǒng)的時鐘。本模塊可以接收外部喚醒信號或者RTC的定時喚醒信號,并穩(wěn)定開啟和恢復系統(tǒng)時鐘,最終切換到正常的工作模式下。

AMBA總線接口模塊

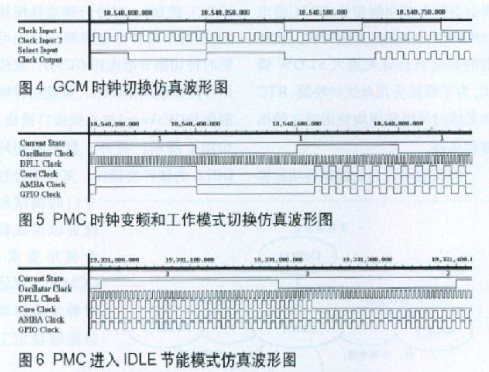

RISC的內(nèi)核通過APB總線讀寫PMC時鐘功耗管理單元的寄存器,這些寄存器映射到統(tǒng)一的地址空間。另外,輸出到各個模塊的時鐘信號也通過這個模塊進行開關控制。PMC的主要控制寄存器描述如表1所示。

仿真結果及流片

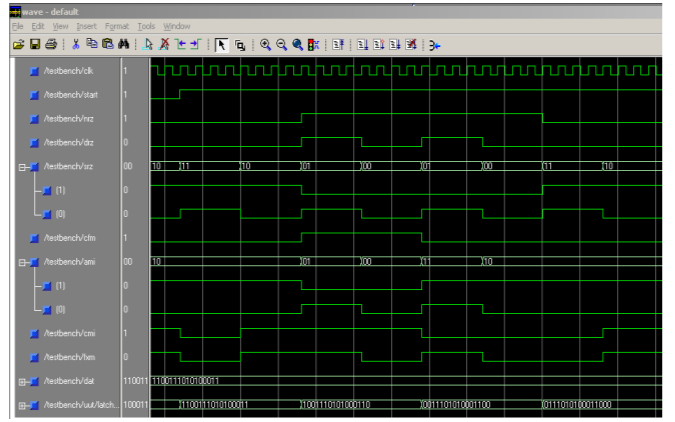

PMC時鐘功耗管理控制器采用RTL級的Verilog HDL進行描述。使用A720T內(nèi)核仿真模型、AMBA總線和中斷控制器等功能模塊的RTL級Verilog代碼,以及本設計的源代碼,共同組成完整的仿真環(huán)境。其中A720T內(nèi)核是ARM公司設計的一款ARM7系列內(nèi)核,在ARM7TDMI基礎上增加了虛擬地址與物理地址轉換器MMU、指令Cache和數(shù)據(jù)Cache。A720T內(nèi)核仿真模型是ARM公司提供給授權開發(fā)機構用以完成仿真的功能模型,它不能被綜合,只能用于功能驗證。使用Synopsys公司的EDA工具VCS對本設計的功能進行仿真和驗證。其中GCM模塊還使用HSIM進行了SPICE晶體管級的模型仿真。GCM時鐘切換的仿真結果如圖4所示,PMC時鐘變頻和工作模式切換的仿真結果如圖5所示,PMC進入IDLE節(jié)能模式的仿真波形如圖6所示。從仿真結果可以看出,PMC能夠正常完成預計功能,可以穩(wěn)定地改變時鐘頻率,并根據(jù)工作模式開關時鐘。

PMC時鐘功耗管理控制器已成功應用于東南大學ASIC工程中心自主開發(fā)的基于ARM7的嵌入式處理器Garfield4Plus中。通過該芯片的實際流片,PMC獲得實片測試的機會。測試結果表明,PMC能夠正常穩(wěn)定地完成預計功能,包括工作頻率的實時配置、工作模式的切換以及芯片的節(jié)能和喚醒。

結語

本文描述的PMC設計的特點在于工作時鐘的統(tǒng)一和時鐘結構的清晰簡潔。GCM無毛刺時鐘切換電路,使得多個時鐘源(包括每個時鐘源的各種不同的頻率配置)在真正提供給系統(tǒng)使用之前就得到了很好的統(tǒng)一。這種時鐘結構可以帶來更好的系統(tǒng)穩(wěn)定性和時序上的余量,也就代表著可以使用更高的系統(tǒng)時鐘頻率。

今后對PMC的優(yōu)化應當重點關注以下兩點。一方面,應當使PMC在針對不同系統(tǒng)的具體特點時,能夠對功耗的實時管理進行更靈活的配置。既要保證最大限度的節(jié)能,又要增加PMC本身的可移植性。另一方面,應當進一步探索更科學的結構,使提供給系統(tǒng)的時鐘在更靈活的配置方式下,仍然能夠保證安全和穩(wěn)定。

-

芯片

+關注

關注

456文章

51192瀏覽量

427325 -

控制器

+關注

關注

112文章

16448瀏覽量

179480 -

soc

+關注

關注

38文章

4204瀏覽量

219110

發(fā)布評論請先 登錄

相關推薦

如何使用VHDL硬件描述語言實現(xiàn)的十六路彩燈控制系統(tǒng)?

VHDL語言實現(xiàn)DDR2 SDRAM控制

基于Verilog硬件描述語言的IEEE標準硬件描述語言資料合集免費下載

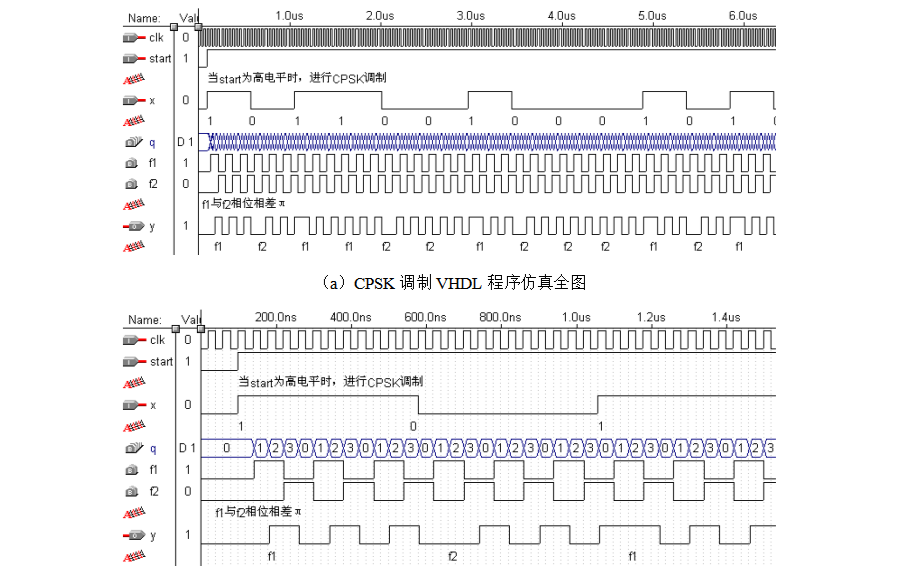

基于VHDL硬件描述語言實現(xiàn)CPSK調制的程序及仿真

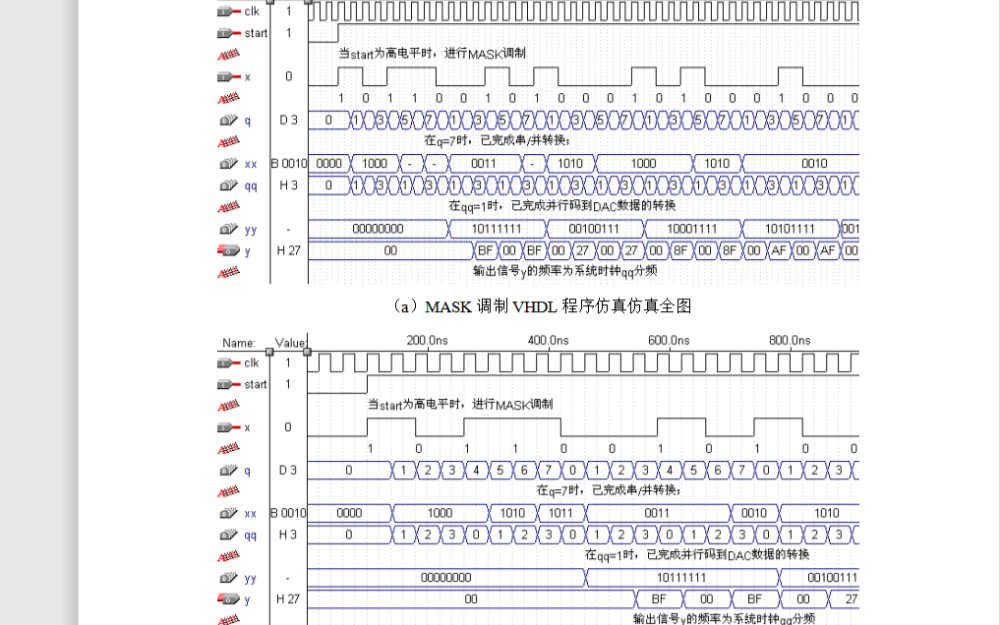

使用VHDL硬件描述語言實現(xiàn)基帶信號的MASK調制的程序與仿真

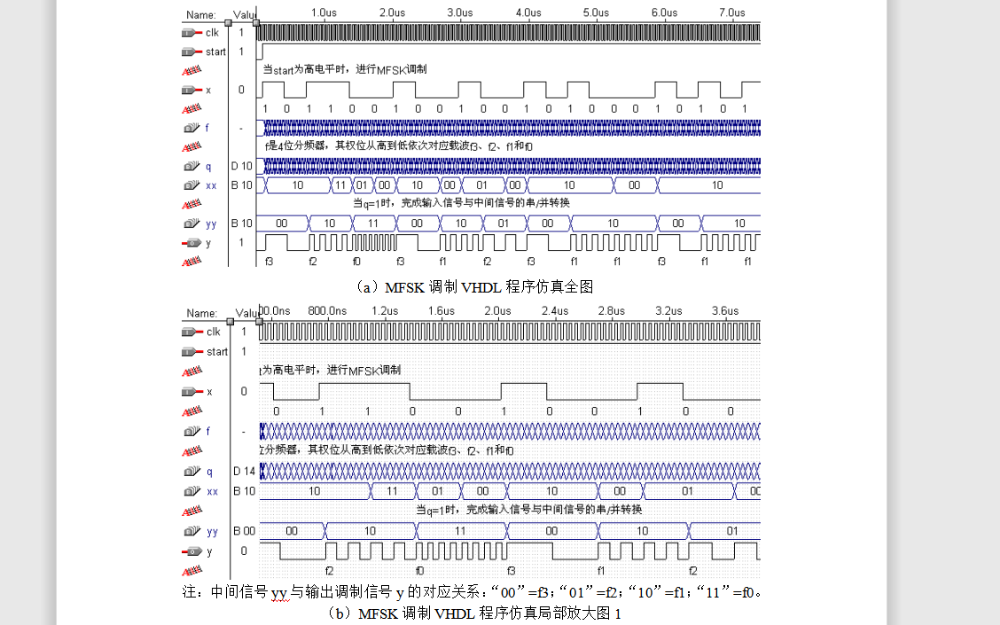

使用VHDL硬件描述語言實現(xiàn)基帶信號的MFSK調制的程序與仿真

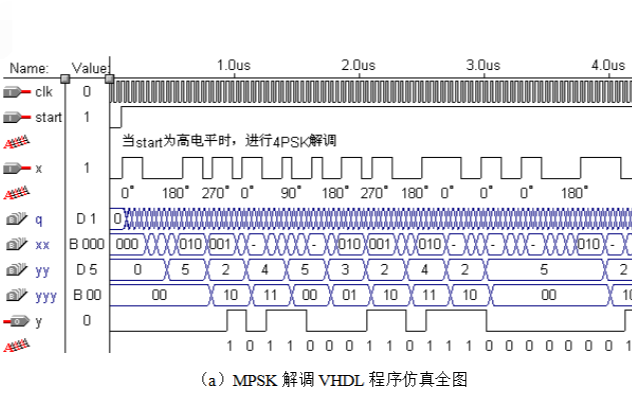

如何使用VHDL硬件描述語言實現(xiàn)基帶信號的MPSK調制

使用VHDL硬件描述語言實現(xiàn)基帶碼發(fā)生器的程序設計與仿真

采用硬件描述語言實現(xiàn)PMC時鐘功耗管理控制器的設計

采用硬件描述語言實現(xiàn)PMC時鐘功耗管理控制器的設計

評論