當(dāng)英特爾在1988年推出第一批NOR芯片時,閃存開始聲名鵲起。并且,NOR為三年后的NAND閃存鋪平了道路。在所有半導(dǎo)體技術(shù)中,NAND的部署速度史無前例,在短短十年內(nèi),從18億美元增長到180億美元。到2017年,該技術(shù)創(chuàng)造500億美元收入,這是創(chuàng)歷史記錄,相當(dāng)于1990年全球半導(dǎo)體市場的總和。NAND閃存無疑是大市場。

但隨著業(yè)界開發(fā)出多種新的存儲技術(shù)作為潛在替代品,這種局面即將發(fā)生改變。

NAND閃存面臨限制

在過去40年里,根據(jù)摩爾定律,通過平均每年減少30%單個比特的大小,每年或每兩年半導(dǎo)體芯片上的晶體管數(shù)量翻一番。這反過來又可降低成本,推動芯片更廣泛的部署。這種30%的減少被稱為工藝縮減,而這種持續(xù)的尺寸和成本降低的現(xiàn)象被稱為縮放。

大多數(shù)半導(dǎo)體都可以持續(xù)縮小,但閃存不是這樣:在閃存中,位作為電子存儲在浮動?xùn)艠O上,浮動?xùn)艠O可承載的電子數(shù)量與晶體管的大小成正比。在15納米(nm)工藝幾何結(jié)構(gòu)中,1和0之間的差異僅為幾十個電子,這在數(shù)字芯片內(nèi)的噪聲中極其難以檢測。如果制造商將晶體管的尺寸減小30%%,正如他們一直做的那樣,那么,電子的數(shù)量就會低于可檢測的水平。

整個半導(dǎo)體市場一直建立在持續(xù)降低成本的期望之上。如果閃存價格不再下降,這顯然行不通。面對平面NAND縮放限制,我們應(yīng)該怎樣做來繼續(xù)降低成本?

3D NAND登場

在2006年,東芝(Toshiba)推出了一個聰明的解決方案。他們不是繼續(xù)縮小芯片表面的晶體管,而是創(chuàng)建垂直結(jié)構(gòu)并沿著塔璧建造晶體管,類似于城市辦公樓墻壁的垂直花園。如果地球表面沒有足夠的種植面積來種植花園,那么就在建筑物的墻壁種植吧。

即使晶體管無法縮放,通過利用這種方法來增加芯片上的晶體管數(shù)量,東芝計劃繼續(xù)降低閃存單元的成本。他們將這種方法稱為Bit Cost Scaling,或者說BiCS,這是3D NAND閃存的基礎(chǔ)。

BiCS不僅可以繼續(xù)降低成本,還可支持繼續(xù)使用NAND閃存,因為3D NAND和平面NAND非常相似,只需很少或者根本不需要重新設(shè)計就可互換使用。消費者可能會使用兩個USB閃存驅(qū)動器,一個采用3D NAND,另一個是平面NAND,但他們無法區(qū)分二者。這比其它一些新的存儲技術(shù)更具優(yōu)勢。 目前業(yè)界采用東芝的方法。通過BiCS,通過填充半導(dǎo)體層中的孔,在形成的列中構(gòu)建位。那問題就變成:我們可以構(gòu)建多高的垂直位塔?現(xiàn)在還不清楚。

當(dāng)東芝首次開發(fā)BiCS時,人們普遍認為列中位數(shù)將受到芯片中層數(shù)的限制,以及用于創(chuàng)建列的孔的寬度和深度的限制。制造商不能使這個孔小于20nm,因為一些同心層材料必須涂覆在內(nèi)部,而這些同心層具有最低厚度要求。同時,深度與垂直層的數(shù)量成比例,而這些垂直層也有最低厚度要求。考慮到這些限制,孔的縱橫比(深度除以直徑)由閃存中的垂直層數(shù)決定。

構(gòu)建3D NAND

3D NAND采用相對簡單的方法以將更多晶體管放在芯片上:在側(cè)向構(gòu)建晶體管,而完全不同于此前的方式。

大多數(shù)芯片通過光刻工藝制造。在這里,制造數(shù)十億晶體管的模式被映射到硅晶片表面,通過類似于照片底片被稱為mask的方法照射光線,然后處理未曝光的硅片部分。這本質(zhì)上是一種平面方法;照片總是二維的。

那么,我們?nèi)绾螌⑵滢D(zhuǎn)變?yōu)?D?在創(chuàng)建3D NAND時,創(chuàng)造者意識到他們可通過另一種方法來構(gòu)建他們需要的高度重復(fù)的模式。如果他們在芯片表面制造很多層材料,例如夾心蛋糕,然后他們可在所有這些層蝕刻孔。這產(chǎn)生的結(jié)構(gòu)類似于在孔壁側(cè)面打印照片。同時,這不需要采用照相過程就可完成,因為這種模式已存在于圖層中。當(dāng)然,除此之外還有更多細節(jié),但這基本就是3D NAND的秘密。

40比1的縱橫比難以制造,60比1則極具挑戰(zhàn)性。但隨著層數(shù)增加,則需要更高的縱橫比。這似乎意味著3D NAND將限制為三代,或者說大約100層,然后它會被新技術(shù)取代。

半導(dǎo)體研究人員是非常創(chuàng)新的群體,他們又提出新的想法,被稱為字符串堆疊,可支持更高的層數(shù)。通過字符串堆疊,可制造一定層數(shù)的3D NAND,然后在其上方構(gòu)建另一組層級。每組新的層,會形成新的孔,但這個孔是通過較少層數(shù)來蝕刻,因此其縱橫比保持適中。例如,Micron Technology通過32層兩次蝕刻來產(chǎn)生當(dāng)前的64層3D NAND,而不是通過64層來蝕刻具有挑戰(zhàn)性的孔。這相當(dāng)于兩個30比1縱橫比孔和一個60比1縱橫比孔之間的差異。

沒有人知道字符串可堆疊多少次會達到極限。普遍的觀點是500層限制,但這無法確定。在半導(dǎo)體世界中,常識通常被證明是錯誤的。

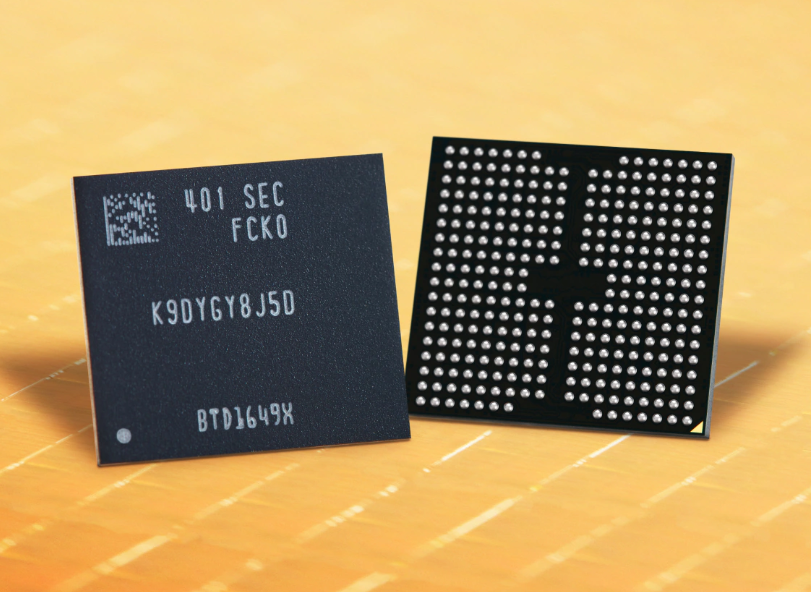

現(xiàn)在的64層芯片的密度高達1太字節(jié)(128GB),而500層芯片可能可存儲幾乎10倍多數(shù)據(jù)。我們當(dāng)然可以想象太字節(jié)芯片。如果太字節(jié)芯片構(gòu)建在500層工藝上,這相當(dāng)于64層128GB。 字符串堆疊的影響意味著3D NAND可能還會存在很長一段時間時間。

3D XPoint呢?

在2015年,英特爾和Micron推出名為3D XPoint的新型內(nèi)存。這項新技術(shù)承諾提供類似RAM的動態(tài)速度,價格點在DRAM和NAND閃存之間。這里的目標是在DRAM主存儲和NAND SSD之間提供新的存儲層,以提高計算機的性價比。

3D XPoint并不會取代NAND閃存或DRAM,盡管它可能會用于減少系統(tǒng)所需的DRAM數(shù)量以達到任何給定的性能水平。這完全不同于很多新存儲技術(shù),因為很多新存儲技術(shù)旨在取代閃存或DRAM—當(dāng)達到擴展限制時。

到目前為止,3D XPoint只能在PCIe非易失性存儲器快速(NVMe)接口中使用。雖然NVMe是SSD最快的接口,但與3D XPoint內(nèi)存的固有速度相比,它速度仍然較慢。事實上,雖然英特爾和Micron公司認為3D XPoint的速度是NAND閃存的1000倍,但事實上,英特爾Optane固態(tài)硬盤的速度只有NAND閃存的六到八倍。

顯然,這里需要DIMM接口來釋放3D XPoint的速度以及充分利用其性價比優(yōu)勢。英特爾承諾以DIMM格式發(fā)布3D XPoint內(nèi)存,但他們尚未公開推出這樣的產(chǎn)品。不過,英特爾透露,他們已經(jīng)在2018年8月的閃存峰會上向谷歌提供這些DIMM。

Objective Analysis的2015年3D XPoint報告預(yù)測,3D XPoint內(nèi)存最重要的市場是用于服務(wù)器的DIMM。我們也認同這一結(jié)論。現(xiàn)在的3D XPoint內(nèi)存市場規(guī)模相對較小,主要包括愿意花費大量資金來小范圍提升性能的客戶。

英特爾的3D XPoint戰(zhàn)略

讓英特爾頭痛的是,3D XPoint市場規(guī)模仍然很小,這讓他們無法將該產(chǎn)品大批量生產(chǎn)。如果沒有高產(chǎn)量,其生產(chǎn)成本將會保持很高,可能高于DRAM。然而,英特爾必須以低于DRAM的價格出售3D XPoint,才會吸引消費者。這意味著英特爾必須賠錢來建立市場。

這種方法可能不會吸引其他公司,但對于英特爾來說則不同。3D XPoint內(nèi)存使該公司可銷售價格更高的處理器,以幫助他們賺回在3D XPoint銷售中損失的資金。

其他新興內(nèi)存技術(shù)

3D XPoint只是眾多正在研發(fā)的新內(nèi)存技術(shù)之一。有些內(nèi)存技術(shù)已經(jīng)開發(fā)相當(dāng)長的時間,例如相變存儲器(PCM),英特爾的Gordon Moore早在1970年就寫過相關(guān)文章。

這些新技術(shù)可實現(xiàn)高性能、低功耗、非易失性以及最重要的是,超越DRAM和NAND閃存的擴展限制。但NAND閃存和DRAM開發(fā)商仍在繼續(xù)想辦法繞過障礙,從而推遲新技術(shù)取代NAND和DRAM的時間。

嵌入式存儲市場最有可能成為這些新技術(shù)的溫床。但這些新技術(shù)可能需要很長時間才有機會取代DRAM或者NAND閃存。嵌入式內(nèi)存將更快采用新技術(shù),因為邏輯芯片上的內(nèi)存必須簡單且經(jīng)濟地用于制造ASIC、微控制器和微處理器。

NOR閃存是這些芯片上最常見的非易失性內(nèi)存,它難以擴展超過45納米,雖然實驗室原型可達到最低14納米。同樣的,即使是靜態(tài)RAM也很麻煩,SPAM位的大小無法成比例地縮放。這可能導(dǎo)致芯片的SPAM部分膨脹,并限制成本優(yōu)勢,這是縮放ASIC、微控制器和微處理器到更小工藝可實現(xiàn)的成本優(yōu)勢。

NOR和SRAM都是是新存儲技術(shù)可取代的對象,新技術(shù)還包括:

磁性RAM(MRAM)是基于磁性技術(shù),目前已經(jīng)在大批量生產(chǎn)中,用于制造HDD中的磁頭。五年來,Everspin Technologies一直在生產(chǎn)這種非易失性技術(shù)作為獨立內(nèi)存,并且正在開發(fā)嵌入式版本。MRAM是基于類似DRAM的但晶體管單元,使其能夠在成本上與DRAM競爭,而不是NAND閃存。

相變內(nèi)存是英特爾和Micron的3D XPoint內(nèi)存的基礎(chǔ)。大約在10年前,它作為NOR閃存的替代品投入生產(chǎn),但只有英特爾、三星和STMicroelectronics推出該技術(shù),現(xiàn)在這些廠商已經(jīng)放棄該產(chǎn)品。

鐵電RAM(FRAM)已經(jīng)投入生產(chǎn)長達20多年,但由于它依賴鉛材料而破壞底層硅的完整性,因而人們對其認可度有限。盡管如此,富士通生產(chǎn)的基于FRAM芯片幾乎超過所有替代內(nèi)存替代品的總和。新的研究已經(jīng)確定一種更友好和更好理解的材料:氧化鉿,可作為鐵電層,使得人們重新關(guān)注這項技術(shù)。

導(dǎo)電橋接RAM(CBRAM)是基于通過硫系玻璃對金屬絲的遷移。Adesto Technology是唯一一家提供這種內(nèi)存類型的公司。

電阻式RAM(ReRAM)采用一種類似的技術(shù),其中納米金屬絲通過硫系玻璃層生長。ReRAM開發(fā)了一種位單元,其中包含內(nèi)部選擇器機制,可簡化生產(chǎn)過程,同時無需開發(fā)單獨的選擇器。

耗氧RAM(OxRAM)是基于類似CBRAM的現(xiàn)象,其中氧離子從硫系玻璃中移除以形成導(dǎo)電通路。該技術(shù)尚未投入生產(chǎn)。惠普企業(yè)計劃在其高級計算機The Machine中使用OxRAM,但這種方法(被稱為Memristor)被推遲到最近。

Nanotube RAM, or NRAM,by Nantero is based on a layer of carbon nanotubes that can be electrically compressed or expanded to create a high- or low-resistance state.

納米管RAM或者NRAM是基于碳納米管層的技術(shù),它可被電力壓縮或擴展以產(chǎn)生高阻抗或低阻抗狀態(tài)。

除MRAM外,所有這些技術(shù)都是基于雙端選擇器。這些選擇器支持微小的單元尺寸–4f2,或者是光學(xué)印刷在芯片的最小特征尺寸的四倍。它們也可采用3D XPoint內(nèi)存類似的方法進行堆疊以降低成本。

直到最近研究才發(fā)現(xiàn),我們可利用氧化鉿來制造FRAM,所有上述技術(shù)都需要使用新材料,這些材料并不像硅那么好理解。這無疑阻礙這些新技術(shù)的部署,因為這些新材料可能會阻礙大規(guī)模生產(chǎn)。

成本是阻止這些技術(shù)取代現(xiàn)有內(nèi)存技術(shù)的最重要因素。所有這些存儲技術(shù)都比DRAM或NAND閃存貴幾個數(shù)量級,使它們只能用于小眾應(yīng)用。FRAM,可在低功耗下快速寫入的技術(shù)。而MRAM,可快速寫入并具有非易失性,而無需不可靠的電池。PCM因其高輻射耐受性而被選用于衛(wèi)星,而CBRAM出于類似的原因,用于高劑量X射線滅菌的外科手術(shù)器械中。

在這些技術(shù)投入批量生產(chǎn)前,沒有哪項技術(shù)可實現(xiàn)低成本以取代現(xiàn)有內(nèi)存技術(shù)。除非有市場,否則不會大量生產(chǎn),而在價格下降之前市場不會發(fā)展。這是雞與雞蛋的關(guān)系。

展望未來十年

至少在未來十年,NAND閃存仍然將占主導(dǎo)地位,隨后是DRAM。如果英特爾實現(xiàn)其3D XPoint目標,那么它將投入批量生產(chǎn)—盡管英特爾最初將賠錢賺吆喝。在短期內(nèi),其他新內(nèi)存技術(shù)將作為片上內(nèi)存獲得成功,但它們將在相當(dāng)長的時間內(nèi)無法與獨立的DRAM和NAND閃存芯片相競爭。鄒錚翻譯

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27703瀏覽量

222637 -

NAND

+關(guān)注

關(guān)注

16文章

1690瀏覽量

136462 -

晶體管

+關(guān)注

關(guān)注

77文章

9745瀏覽量

138896

原文標題:新存儲技術(shù)挑戰(zhàn)NAND閃存主導(dǎo)地位

文章出處:【微信號:D1Net11,微信公眾號:存儲D1net】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

【半導(dǎo)體存儲】關(guān)于NAND Flash的一些小知識

英特爾考慮出售Altera股權(quán)

英特爾至強品牌新戰(zhàn)略發(fā)布

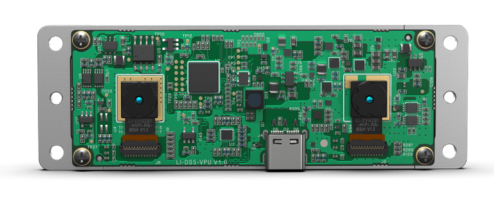

英特爾推出全新實感深度相機模組D421

立體視覺新手必看:英特爾? 實感? D421深度相機模組

曝Apollo擬向英特爾投資50億美元

英特爾IT的發(fā)展現(xiàn)狀和創(chuàng)新動向

鎧俠瞄準2027年:挑戰(zhàn)1000層堆疊的3D NAND閃存新高度

3D NAND閃存來到290層,400層+不遠了

NAND閃存面臨限制,英特爾的3D XPoint戰(zhàn)略

NAND閃存面臨限制,英特爾的3D XPoint戰(zhàn)略

評論