通常,我們優先解決建立時間違例。Setup slack與邏輯延遲、布線延遲、時鐘歪斜和時鐘不確定性有關。因此,首先要明確這幾個因素中哪個因素對建立時間違例起關鍵作用。具體的衡量標準可由如下幾個數值確定。這也是ug1292第三頁的主題。

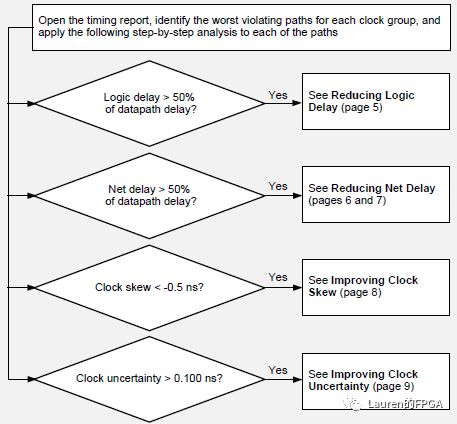

ug1292第三頁也給出了建立時間違例分析流程,如下圖所示。當邏輯延遲占比超過50%時,要著重降低邏輯延遲;當布線延遲占比超過50%時,要把焦點放在布線延遲上;同時,也要關注一下時鐘歪斜和時鐘不確定性。當時鐘歪斜小于-0.5ns或時鐘不確定性大于0.1ns時,兩者將成為時鐘違例的主要“貢獻者”。

圖片來源, page 3, ug1292

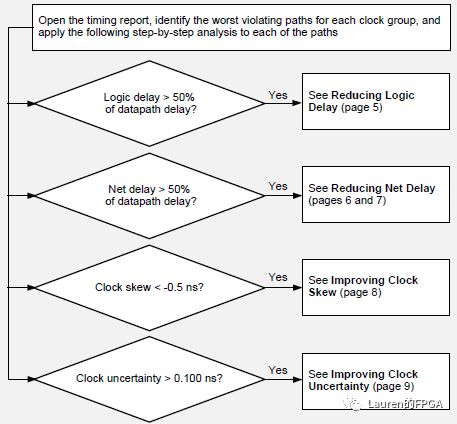

上述四個數值,無論是在timing report(通過report_timing_summary生成)還是design analysis report(通過report_design_analysis生成)中都有所體現。以timingreport為例,如下圖所示,可清晰地顯示上述四個數值。

圖片來源, page 3, ug1292

注:上述數據只針對UltraScale系列芯片。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:深度解析ug1292(3)

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

相關推薦

靜態時序分析包括建立時間分析和保持時間分析。建立時間設置不正確可以通過降低芯片工作頻率解決,保持

![的頭像]() 發表于

發表于 08-22 10:38

?4356次閱讀

建立時間(setup time)和保持時間(hold time)是時序分析中最重要的概念之一,深入理解建立時間和保持時間是進行時序

發表于 06-21 10:44

?1913次閱讀

有沒有人遇到在DC綜合后分析建立時間時序,關鍵路徑時序違例是因為起始點是在時鐘的下降沿開始驅動的,但是設計中都是時鐘上升沿觸發的。在線等待各位大牛解惑!很急 求大神幫忙!

發表于 01-04 15:17

本帖最后由 虎子哥 于 2015-3-12 21:24 編輯

建立時間(Setup Time):是指在觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間,如果建立時間不夠,數據將不能在這個時鐘

發表于 03-10 23:19

ADC時延和建立時間的區別是什么?以及ADC時延和建立時間將會如何影響您的應用電路?

發表于 04-12 07:19

該文簡要討論了環路性能(建立時間,相位噪聲和雜散信號)和環路參數(帶寬,相位裕度等)的相互關系。提出并分析了一種自適應的具有快速建立時間的鎖相環結構及其關鍵模塊(鑒相

發表于 04-23 08:33

?20次下載

時延和建立時間setup在ADC電路中的區別:對于大多數 ADC 用戶來說,“時延”和“建立時間”這兩個術語有時可以互換。但對于 ADC 設計人員而言,他們非常清楚

發表于 11-22 23:33

?1614次閱讀

初始設計檢查流程如下圖所示。對象是綜合后或opt_design階段生成的dcp。會依次執行三個命令(圖中紅色標記),生成三個報告:FailFast報告、時序報告和UFDM(UltraFast Design Methodology)報告。

![的頭像]() 發表于

發表于 10-12 11:19

?3700次閱讀

UG1292第一頁是針對綜合后或者opt_design階段的使用說明。vivado的基本流程有5步(其實不同策略可以更多,具體使用方法和好處以后講),分別是synth_design

![的頭像]() 發表于

發表于 10-30 10:25

?3432次閱讀

本篇仿真介紹放大器的建立時間,也稱為上升時間。它是高速放大電路、或在SARADC驅動電路設計時,需要謹慎評估的參數。

![的頭像]() 發表于

發表于 02-15 16:37

?6475次閱讀

AN-359:運算放大器的建立時間

發表于 04-29 15:28

?4次下載

??本文主要介紹了建立時間和保持時間。

![的頭像]() 發表于

發表于 06-21 14:38

?2877次閱讀

建立時間和保持時間是SOC設計中的兩個重要概念。它們都與時序分析有關,是確保芯片正常工作的關鍵因素。

![的頭像]() 發表于

發表于 08-23 09:44

?1062次閱讀

信號經過傳輸線到達接收端之后,就牽涉到建立時間和保持時間這兩個時序參數,它們表征了時鐘邊沿觸發前后數據需要在鎖存器的輸入持續時間,是接收器本身的特性。簡而言之,時鐘邊沿觸發前,要求數據必須存在一段

發表于 09-04 15:16

?959次閱讀

電子發燒友網站提供《UltraFast設計方法時序收斂快捷參考指南(UG1292).pdf》資料免費下載

發表于 09-15 10:38

?0次下載

深度解析ug1292建立時間違例分析流程

深度解析ug1292建立時間違例分析流程

評論