一. 概述

這里以7系列的FPGA為例,先從整體上去了解一下FPGA內部可編程邏輯資源的結構。了解FPGA器件的內部資源與結構有利于我們優化設計與評估設計資源。

現在的FPGA里面有很多存儲資源,DSP(數字信號處理)資源,布線通道,I/O資源,當然最根本的還是CLB(Configurable Logic Block)。Xilinx的資源分布采用ASMBL架構。下圖是一個抽象的結構圖,相同資源以列方式排布。這篇文章主要講解CLB資源。

二. CLB資源介紹

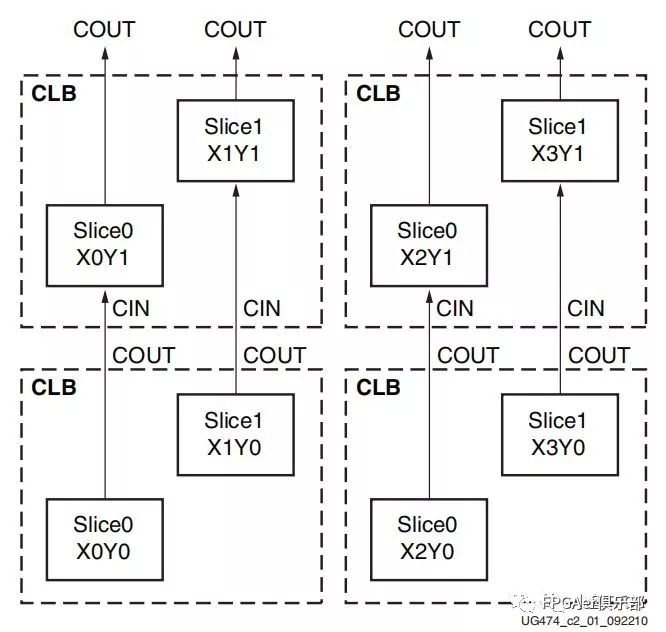

CLB資源的分布以縱向相連,如下圖所示。每個CLB由兩個Slice組成。同一個CLB里面的兩個Slice之間沒有互連線。

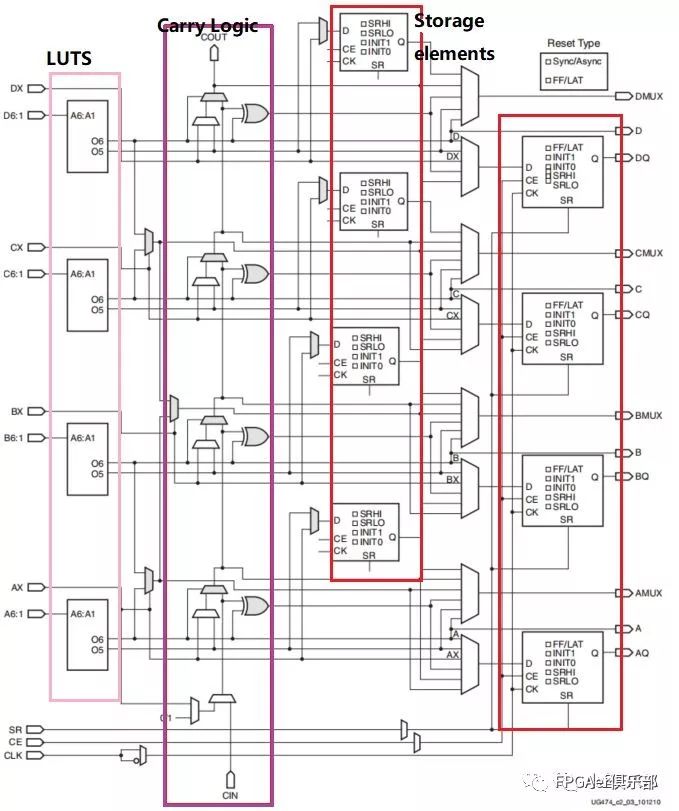

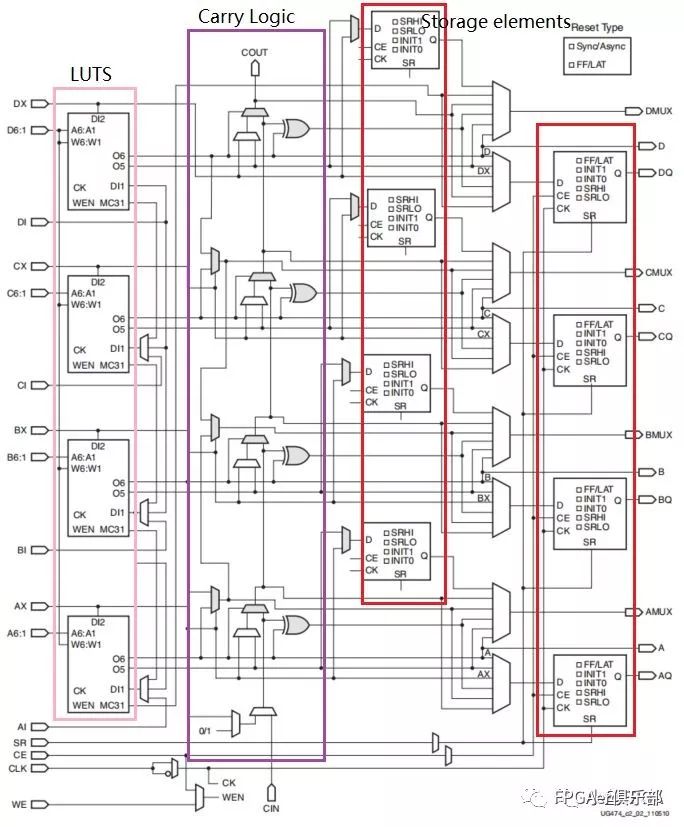

每個Slice里面有4個6輸入的LUT(look-up tables(查找表))和8個存儲單元(Storage)以及進位邏輯(Carry Logic)和多路選擇器(Multiplexers)。同時Slice有兩種。

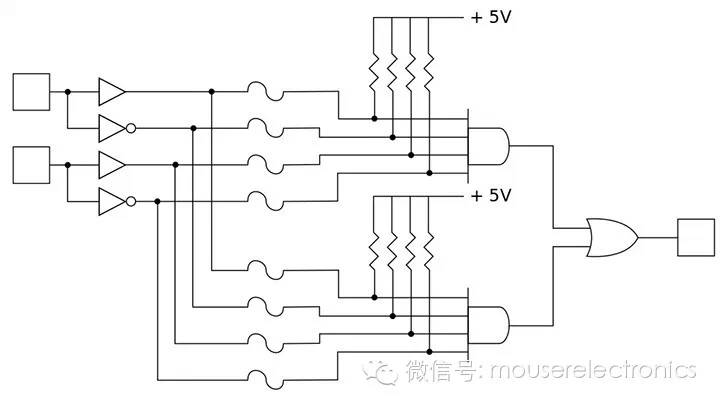

普通的Slice叫SLICEL,電路結構如下,最左邊一列就是4個LUT,第二列為Carry Logic,以及紅色框框出來的存器單元。

第二種Slice叫SLICEM,電路結構如下。除了LUTS與SLICEL的LUTS不同之外,其余結構都一樣。這就是SLICEM與SLICEL之間的區別,利用SLICEM的LUTS還可以構成RAM,ROM,以及Shift Registers(移位寄存器)。

一個CLB里面含有一個SLICEM和SLICEL或者含有兩個SLICEL。

Slice就是通過LUTS以及Carry Logic和Multiplexers之間的互連來形成組合邏輯,再通過Storage elements構成寄存器以形成時序邏輯。

同時借助SLICEM的LUTS,還可以構成RAM,ROM,Shift Registers資源。

下表是一個CLB可以擁有的資源數以及可以形成大小為多少的RAM與Shift Registers。我們可以借助這些信息去評估設計需要多少資源和選擇什么型號的FPGA器件。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605996 -

CLB

+關注

關注

0文章

29瀏覽量

5981

原文標題:FPGA內部可編程邏輯資源的結構,CLB資源介紹

文章出處:【微信號:FPGAer_Club,微信公眾號:FPGAer俱樂部】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

什么是可編程邏輯

可編程邏輯器件

【FPGA - 基礎知識(零)】FPGA芯片資源介紹 精選資料推薦

什么是PLD(可編程邏輯器件)

基于FPGA進行可編程邏輯設計

FPGA CPLD可編程邏輯器件的在系統配置方法

FPGA內部可編程邏輯CLB資源分析

FPGA內部可編程邏輯CLB資源分析

評論