過大的Clock Skew也可能導致時序違例,尤其是其數值超過0.5ns時。如下三個命令生成的報告中均可顯示Clock Skew的具體數值。

report_design_analysis

report_timing_summary

report_timing

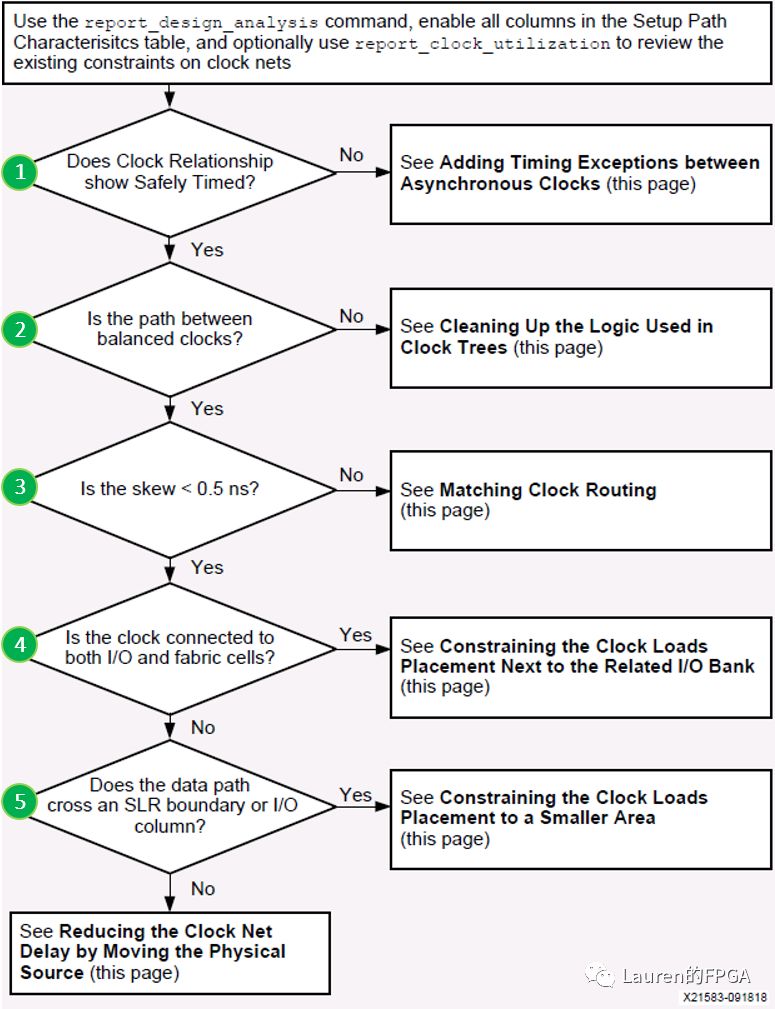

降低Clock Skew可采用如下流程操作。

圖片來源: page 8, ug1292

1

異步跨時鐘域路徑是否被安全合理地約束

時鐘關系有兩種:同步時鐘和異步時鐘。如果發送時鐘和接收時鐘是同源的,例如來自于同一個MMCM,則認為二者是同步時鐘,否則就按異步時鐘處理。對于異步跨時鐘域路徑,可采用如下三者之一進行約束:

set_clock_groups

set_false_path

set_max_delay -datapath_only

2

發送時鐘和接收時鐘的時鐘樹結構是否平衡

時鐘樹結構其實就是時鐘的拓撲結構。從發送時鐘和接收時鐘的角度看,平衡的時鐘樹結構是指二者“走過相同或等效的路徑”。如下圖所示,發送時鐘和接收時鐘來自級聯的BUFG的不同位置上,這就是典型的不平衡時鐘樹。在設計中要避免這種情形。通過Tcl命令report_methodology可檢查出設計中級聯的BUFG。

<不推薦>

同時,還要利用好BUFG_GT和BUFGCE_DIV,兩者均可實現簡單地分頻。如下圖所示,利用BUFG_GT實現二分頻,從而節省了MMCM。

此外,還要保持時鐘路徑“干凈”,即不能在時鐘路徑上存在組合邏輯。在時序報告中,點擊如下圖標記的按鈕,按下F4,在顯示時序路徑的同時也會顯示該路徑的時鐘拓撲結構。

3

檢查Clock Skew是否小于0.5ns

CLOCK_DELAY_GROUP可有效改善同步跨時鐘域路徑的Clock Skew,因此,Xilinx建議對于關鍵的同步跨時鐘域路徑,可通過設置該屬性降低Clock Skew,即使發送時鐘和接收時鐘具有相同的CLOCK_ROOT值。CLOCK_DELAY_GROUP的具體使用方法如下圖所示,其中clk1_net和clk2_net是Clock Buffer的輸出端連接的net。但是,避免過多使用該屬性,否則會適得其反。

4

時鐘是否同時驅動I/O和Slice中的邏輯資源

如果時鐘同時驅動I/O和Slice中的邏輯資源,且負載小于2000時,可通過CLOCK_LOW_FANOUT屬性對相應的時鐘net進行設置,最終可使工具將該時鐘驅動的所有負載放置在同一個時鐘域內。通過命令report_clock_utilization生成的報告可查看每個時鐘的負載,如下圖所示。

CLOCK_LOW_FANOUT的具體使用方法如下圖所示。

5

檢查數據路徑是否穿越SLR或I/O Column如果時鐘負載較小且穿越SLR或I/O Column時,可通過Pblock實施位置約束,將負載限定在一定區域內,例如在一個SLR內,以避免穿越一些特殊列,例如I/O Column。相反地,如果數據路徑并未穿越SLR或I/O Column,可嘗試對相應的MMCM或PLL做位置約束,使其位于這些負載的中央。

-

時鐘

+關注

關注

11文章

1746瀏覽量

131799 -

CLOCK SKEW

+關注

關注

0文章

2瀏覽量

1567

原文標題:深度解析ug1292(8)

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

時鐘向導中是否有一個功能可以指導兩個PLL生成沒有偏斜的時鐘?

非常高效三個linux shell命令分享

Skew Correction Using Delay Li

使用NoKia手機的三個技巧

電腦木馬識別的三個小命令(不可不知)

DSP硬件課程的三個實驗報告資料合集免費下載

同步電路設計中CLOCK SKEW的分析說明

三個命令生成的報告中均可顯示Clock Skew的具體數值

三個命令生成的報告中均可顯示Clock Skew的具體數值

評論