最新版英特爾?SoC FPGA 嵌入式開發(fā)套件(SoC EDS)是一套全面的工具套件,它能夠在英特爾系統(tǒng)芯片FPGA上進(jìn)行嵌入式軟件開發(fā)工作,幫助您快速固件以及加速您的嵌入式軟件開發(fā)。

那么SoC EDS具體能支持您什么呢?

利用 ARM* Development Studio 5* (DS-5*) 英特爾? SoC FPGA 版進(jìn)行應(yīng)用編碼、構(gòu)建、調(diào)試和優(yōu)化

借助實(shí)用程序和運(yùn)行時(shí)軟件,加速 SoC FPGA 嵌入式系統(tǒng)開發(fā)

借助裸機(jī)和 Linux* 應(yīng)用示例,快速開始開發(fā)

“New特性”助力,開發(fā)&調(diào)試更輕松

英特爾還更新了英特爾? SoC EDS v18.1的新增特性,包括FPGA自適應(yīng)調(diào)試、應(yīng)用性能分析和更新至SD卡映像等。

FPGA自適應(yīng)調(diào)試

在 CPU-FPGA 邊界之間進(jìn)行交叉觸發(fā)與調(diào)試,以發(fā)現(xiàn)隱藏的漏洞

關(guān)聯(lián) FPGA 和 CPU 之間的事件與時(shí)間戳數(shù)據(jù)

使用內(nèi)置于英特爾? SoC FPGA 開發(fā)套件(也可以用作外部 JTAG 調(diào)試線纜)的英特爾? FPGA Download Cable II 執(zhí)行裸機(jī)調(diào)試

從 Platform Designer(原 Qsys)和英特爾? Quartus? Prime 軟件導(dǎo)入自定義知識(shí)產(chǎn)權(quán) (IP) 寄存器定義,以提高生產(chǎn)效率

應(yīng)用性能分析

使用 Streamline* 直觀了解嵌入式軟件的性能瓶頸

支持裸機(jī)、Linux* 和安卓* 應(yīng)用

設(shè)置并配置 ARM 性能計(jì)數(shù)器,以便深入了解您的嵌入式設(shè)計(jì)

優(yōu)化代碼,以實(shí)現(xiàn)最佳性能

更新至SD卡映像

目前,SD 卡映像可以單獨(dú)下載,并用于黃金系統(tǒng)參考設(shè)計(jì) (GSRD) 和 SoC EDS。在 Rocketboards.org 上可免費(fèi)下載。

固有優(yōu)勢(shì),持續(xù)助力您的設(shè)計(jì)

英特爾借助 v18.1的全新改進(jìn)特性,也將能夠繼續(xù)支持 SoC FPGA 嵌入式軟件設(shè)計(jì)。當(dāng)然,除了新特性,它本身還有以下幾個(gè)固有特性:

ARM Development Studio 5 英特爾? SoC FPGA版:基于ARM DS-5的強(qiáng)大Eclipse IDE具備全面功能,支持您在一個(gè)IDE中進(jìn)行編碼、構(gòu)建、調(diào)試和優(yōu)化!

硬件庫:輕松訪問底層硬件以進(jìn)行配置和控制。

配置工具:英特爾? FPGA 特定的系統(tǒng)芯片配置工具可提升工作效率。

設(shè)計(jì)示例:面向 SoC FPGA 開發(fā)套件的黃金硬件參考設(shè)計(jì) (GHRD)。U-Boot、Linux* 和裸機(jī)參考示例支持您快速開始開發(fā)。

-

英特爾

+關(guān)注

關(guān)注

61文章

10009瀏覽量

172340 -

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

121192 -

嵌入式軟件

+關(guān)注

關(guān)注

4文章

240瀏覽量

26733

原文標(biāo)題:嵌入式軟件開發(fā)方法再升級(jí),全新“英特爾? SoC EDS v18.1”

文章出處:【微信號(hào):FPGAer_Club,微信公眾號(hào):FPGAer俱樂部】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

使用英特爾哪吒開發(fā)套件部署YOLOv5完成透明物體目標(biāo)檢測(cè)

萊迪思Propel工具套件加速FPGA應(yīng)用開發(fā)

【xG24 Matter開發(fā)套件試用體驗(yàn)】深入了解Silicon Labs xG24 Matter開發(fā)套件

聚焦嵌入式開發(fā)中的合規(guī)性工具、項(xiàng)目管理工具、版本迭代工具應(yīng)用

嵌入式開發(fā)前景怎么樣?

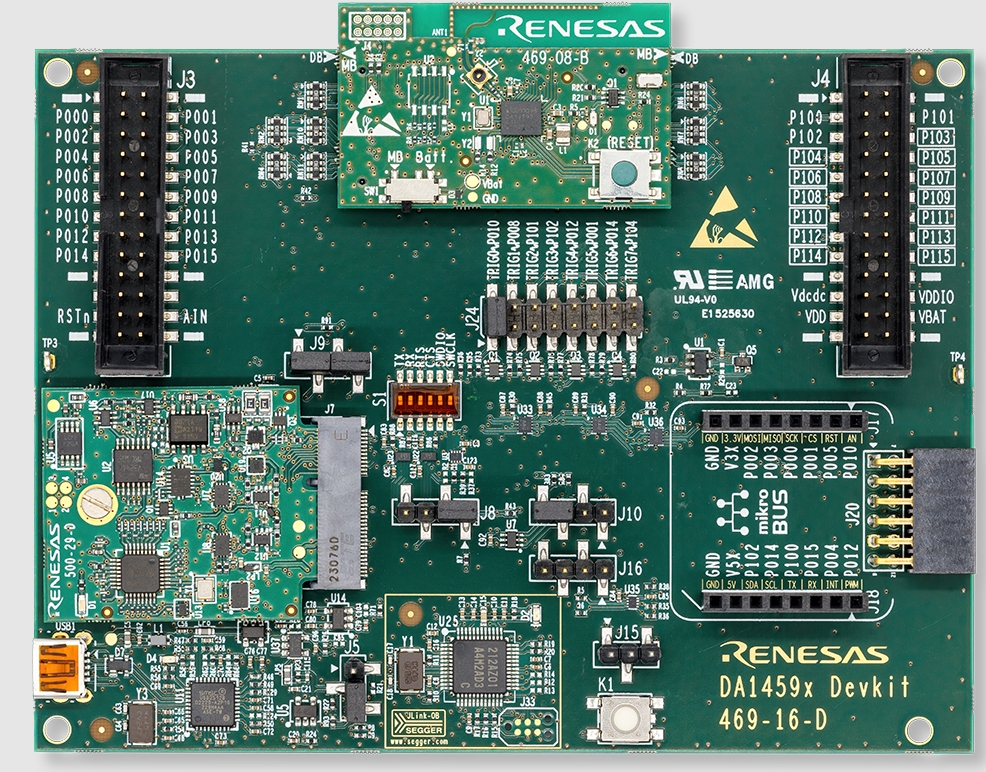

SmartBond? DA14592低功耗藍(lán)牙? 5.2 SoC 開發(fā)套件 Pro數(shù)據(jù)手冊(cè)

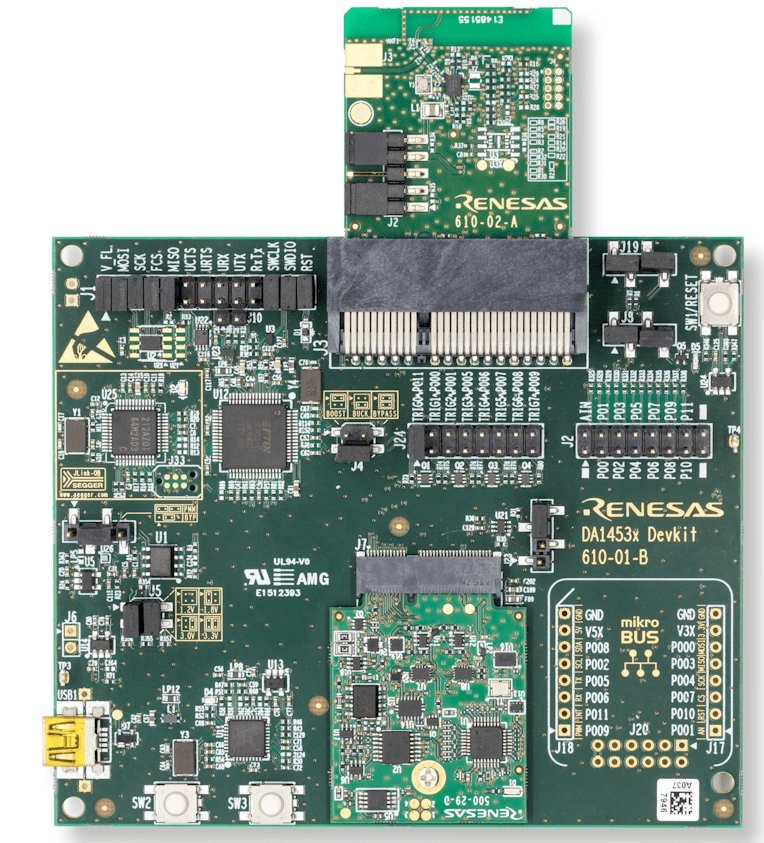

DA14535 SmartBond TINY? SoC開發(fā)套件數(shù)據(jù)手冊(cè)

聯(lián)發(fā)科發(fā)布天璣AI開發(fā)套件,賦能終端生成式AI應(yīng)用

英特爾開發(fā)套件『哪吒』在Java環(huán)境實(shí)現(xiàn)ADAS道路識(shí)別演示 | 開發(fā)者實(shí)戰(zhàn)

AMD Vitis? Embedded嵌入式軟件開發(fā)套件的功能和特性概述

SC171開發(fā)套件V1 硬件平臺(tái)介紹及使用

英特爾宣布AI PC加速計(jì)劃新增兩項(xiàng)AI舉措

【轉(zhuǎn)載】英特爾開發(fā)套件“哪吒”快速部署YoloV8 on Java | 開發(fā)者實(shí)戰(zhàn)

基于英特爾哪吒開發(fā)者套件平臺(tái)來快速部署OpenVINO Java實(shí)戰(zhàn)

最新版英特爾? SoC FPGA 嵌入式開發(fā)套件(SoC EDS)全面的工具套件

最新版英特爾? SoC FPGA 嵌入式開發(fā)套件(SoC EDS)全面的工具套件

評(píng)論