該演示展示了Zynq-7000 All Programmable SoC及其使用NEON引擎或硬件加速來(lái)加速軟件的能力。 查看Zynq-7000 SoC的靈活性,以加速軟件和利用......

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

dsp

+關(guān)注

關(guān)注

554文章

8059瀏覽量

350413 -

賽靈思

+關(guān)注

關(guān)注

32文章

1794瀏覽量

131505 -

soc

+關(guān)注

關(guān)注

38文章

4204瀏覽量

219091

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于Xilinx ZYNQ7000 FPGA嵌入式開發(fā)實(shí)戰(zhàn)指南

電子發(fā)燒友網(wǎng)站提供《基于Xilinx ZYNQ7000 FPGA嵌入式開發(fā)實(shí)戰(zhàn)指南.pdf》資料免費(fèi)下載

發(fā)表于 12-10 15:31

?2次下載

dac3174與xilinx zynq7000系列連接,fpga的案例參考代碼有沒有?

dac3174與xilinx zynq7000系列連接,fpga的案例參考代碼有沒有?

tsw1400_lvds_dac_sample_wise_restored的代碼寫的實(shí)在太難度了,一句注釋都沒有

發(fā)表于 11-25 06:04

當(dāng)ADC3663的LVDS輸出給到ZYNQ-7000的LVDS接收這兩者之間可以直連嗎?

ADC3663的LVDS差分輸出與xilinx的ZYNQ-7000的LVDS輸入的電平匹配問題

ADC3663的供電是1.8V,ADC3663的LVDS輸出給到ZYNQ-7000的BANK12

發(fā)表于 11-14 07:43

正點(diǎn)原子fpga開發(fā)板不同型號(hào)

ZYNQ-7000系列 ZYNQ-7000系列是正點(diǎn)原子的入門級(jí)FPGA開發(fā)板,適合初學(xué)者和教育用途。這些開發(fā)板搭載了Xilinx的Zynq-7000系列SoC芯片,集成了ARM C

zynq7000 BSP無(wú)法在u-boot加載運(yùn)行怎么解決?

1、硬件配置zynq7000 zedboard

2、下載git,回退到支持zynq7000 的bsp包

3、采用xilinx sdk工具可以運(yùn)行thread-zynq7000.elf

4、采用u-boot tftp下載到板子th

發(fā)表于 09-27 09:26

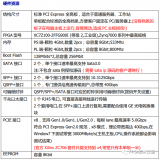

正點(diǎn)原子ZYNQ7015開發(fā)板!ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2,性能強(qiáng)悍,資料豐富!

本帖最后由 jf_85110202 于 2024-9-14 10:33 編輯

正點(diǎn)原子ZYNQ7015開發(fā)板!ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2,性能強(qiáng)悍,資料豐富

發(fā)表于 09-14 10:12

zynq7000 BSP無(wú)法在u-boot加載運(yùn)行,為什么?

1、硬件配置zynq7000 zedboard

2、下載git,回退到支持zynq7000 的bsp包

3、采用xilinx sdk工具可以運(yùn)行thread-zynq7000.elf

4、采用u-boot tftp下載到板子th

發(fā)表于 09-13 07:06

[XILINX] 正點(diǎn)原子ZYNQ7035/7045/7100開發(fā)板發(fā)布、ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

正點(diǎn)原子FPGA新品ZYNQ7035/7045/7100開發(fā)板,ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

正點(diǎn)原子Z100 ZYNQ開發(fā)板,搭載Xilinx

發(fā)表于 09-02 17:18

STM32CubeIDE環(huán)境下使用DSP加速運(yùn)算,但不能下載DSP庫(kù),為什么?

STM32CubeIDE 環(huán)境下使用DSP 加速運(yùn)算,但不能下載DSP庫(kù)!(芯片為STM32G474RBT6)

copy all used libraries into the pro

發(fā)表于 07-05 07:35

簡(jiǎn)談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

、觸發(fā)器和互聯(lián)資源,實(shí)現(xiàn)一個(gè)處理器的功能,這就是軟核處理器,對(duì)于軟核處理器,他通過HDL語(yǔ)言或者網(wǎng)表進(jìn)行描述 ,通過通過綜合后才能被使用。

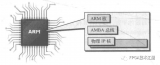

3、ZYNQ-7000 SoC

發(fā)表于 05-08 16:23

Xilinx ZYNQ 動(dòng)手實(shí)操演練

系列。可編程邏輯可由用戶配置,并通過“互連”模塊連接在一起,這樣可以提供用戶自定義的任意邏輯功能,從而擴(kuò)展處理系統(tǒng)的性能及功能。不過,與采用嵌入式處理器的FPGA不同,Zynq-7000產(chǎn)品

發(fā)表于 05-03 19:28

Zynq-7000為何不是FPGA?

Zynq-7000可擴(kuò)展處理平臺(tái)是采用賽靈思新一代FPGA(Artix-7與Kintex-7FPGA)所采用的同一28nm可編程技術(shù)的最新產(chǎn)品系列。

發(fā)表于 04-26 11:30

?1358次閱讀

簡(jiǎn)談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

到PL和PS中,這樣就可實(shí)現(xiàn)獨(dú)一無(wú)二和差異化的系統(tǒng)功能。與傳統(tǒng)的FPGA方法不同的是,ZYNQ 7000 SoC總是最先啟動(dòng)PS內(nèi)的處理器,

發(fā)表于 04-10 16:00

Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)簡(jiǎn)述

以傳統(tǒng)的現(xiàn)場(chǎng)可編程門陣列結(jié)構(gòu)(Field Programmable Gate Array,F(xiàn)PGA)為基礎(chǔ),將專用的中央處理器單元(Central Processing Uint,CPU)和可編程邏輯資源集成在單個(gè)芯片中。

發(fā)表于 04-06 12:40

?672次閱讀

使用Zynq-7000 All Programmable SoC實(shí)現(xiàn)DSP功能的軟件加速

使用Zynq-7000 All Programmable SoC實(shí)現(xiàn)DSP功能的軟件加速

評(píng)論