集成電路的歷史從1958年TI的第一顆Flip-Flop電路開始,那時候只有兩個晶體管組成一個反相器而已。發(fā)展至今已有十億個晶體管的CPU了,而這些都不得不來自于半導(dǎo)體制造業(yè)的技術(shù)推進得以持續(xù)scalable。

半導(dǎo)體能夠變成現(xiàn)實主要是它能夠?qū)崿F(xiàn)“0”和“1”的二進制轉(zhuǎn)換,而在硬件上就是從真空二極管(Vacuum Tube)開始的。大概在第二次世界大戰(zhàn)的時候,電子計算機開始投入適用主要用于通信密碼破譯,但是這些晶體管的性能會很快退化增加Trouble shooting的時間,間接阻礙了半導(dǎo)體行業(yè)的發(fā)展。

直到1947年,貝爾實驗室的三位前輩其中一位是William Shockley他們發(fā)明了點接觸的Ge晶體管,然后1950年,Shockley又發(fā)明了第一個BJT。這些和真空二極管比起來,可靠性和功耗以及尺寸都得到了很搭提高。尤其是BJT是三端晶體管可以當(dāng)作電控開關(guān)(electrical switch),其中一個端子就可以作為控制端。1958年,TI的Jack Kilby在Silicon上做出了兩個BJT,開啟了“Silicon Age”。早期的電路都是用BJT做的,從BJT的原理可以直到,BJT是靠電流驅(qū)動的(Base加電流),而Ice又是雙載流子器件,所以它除了驅(qū)動電流大之外,還有個問題就是靜態(tài)漏電也大,所以如果你的電路非常龐大你的漏電功耗損失將無法接收,所以限制了它的適用。

再到1963年,仙童公司(Fairchild)公司發(fā)明了NMOS和PMOS對稱互補器件組成的CMOS電路,這就是現(xiàn)在我們耳熟能詳?shù)腃MOS技術(shù)。由于它的控制極Gate是靠柵極跨過Gate Dielectric電場耦合實現(xiàn)的,所以沒有控制電流產(chǎn)生的靜態(tài)功耗,所以理論靜態(tài)功耗可以到“0” (當(dāng)然實際上還是有Gate leakage)。實際上早期IC都是只用NMOS+BJT實現(xiàn)電路的,而沒有用PMOS,因為那個時候沒有Twin Well技術(shù)。直到1980年代CPU的晶體管已經(jīng)到了幾千個了,而這時候的功耗已經(jīng)無法接收了,才不得不走入CMOS (Twin Well)時代。

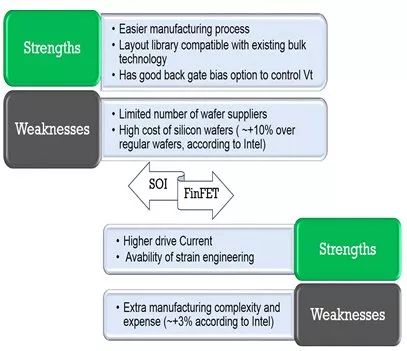

接下來的年代就一直沿著1965年誕生的摩爾定律循規(guī)蹈矩的scaling了,帶來速度、密度、性能的一次次提升。一路從Bulk-Si走到32nm走不下去了,才開始從Planar走向3D FinFET以及SOI技術(shù)。

1、MOSFET器件:

MOSFET來自Metal-Oxide-SemiconductorFieldEffectTrasistor,Metal就是Gate柵極作為控制極的,而Oxide是柵氧作為場效應(yīng)感應(yīng)反型溝道的,Semiconductor自然就是襯底溝道的硅了,而Field Effect自然就是說它的工作原理了,它的控制極是靠柵極電壓通過柵極氧化層感應(yīng)產(chǎn)生反型溝道實現(xiàn)源漏導(dǎo)通,從而實現(xiàn)“0”和“1”的轉(zhuǎn)換。

a、MOS結(jié)構(gòu)

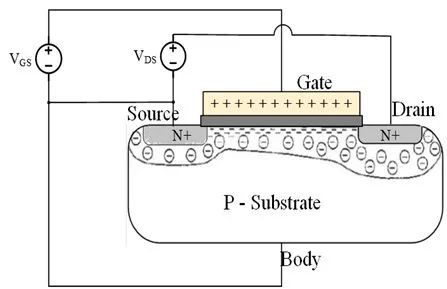

MOSFET是四端結(jié)構(gòu),分別是柵極、源極、漏極、和襯底(Body)。結(jié)構(gòu)上面的柵極是低電阻的材料形成,他與襯底的溝道之間還要有個薄的柵氧化層。一般情況,源漏極是和襯底以及溝道相反的摻雜類型(比如NMOS的源漏是N-Type,而襯底和溝道就是P-type),所以源漏極之間因為各自的PN節(jié)就關(guān)閉了。但是當(dāng)柵極加電壓(NMOS加正電壓,PMOS加負電壓),通過柵極氧化層感應(yīng)一個電場加在了溝道表面,所以襯底的少數(shù)載流子就被吸附到溝道表面累積并反型,最后變得和源漏極摻雜一樣了,從而實現(xiàn)了源漏極導(dǎo)通。一般柵極的開啟電壓(Vt)會收到柵極與襯底的功函數(shù)以及柵氧的厚度/質(zhì)量,還有襯底的摻雜濃度共同決定的。

b、為什么用Poly作為柵極材料

最原始MOSFET發(fā)明的時候用的柵極材料是金屬鋁,這就是為什么叫MOS,而不是POS了,哈哈。

后來才發(fā)展到Poly了。主要是由于Metal Gate都是“Gate Last”制程,先做Source/Drain然后用鋁做柵極gate,但是這樣的問題是柵極和源漏必須要有一定的overlap確保柵極和源漏必須是鏈接起來的(一般2.5um的鋁柵MOSFET的源漏Overlap是0.5um)。但是這樣的overlay電容(Cgs/Cgd)導(dǎo)致了總米勒電容的增加電路速度的降低等。

要解決柵極與源漏overlay電容的問題,就必須要用自對準的源漏,先做Gate然后用Gate做mask打Source/Drain的implant實現(xiàn)自對準,這就是“Gate-First”工藝。

但是“Gate-First”制程也有自身的問題,因為源漏極摻雜必須要經(jīng)過800C以上的高溫才能激活。而如果沿用原始的鋁柵,則無法承受800C的高溫(純鋁的熔點是660C,AlSiCu合金的熔點<500C)。所以才有了Poly作為“Gate-First”制程的柵極材料,但是Poly的電阻很高,所以后來有了doped poly。

也有說柵極材料換成poly的原因是功函數(shù),Metal的功函數(shù)太高,使得Vt可以達到3~5V,這在以前的MOSFET可以接收,但是到submicron時代肯定不能接受了,所以可以用Poly通過doping來調(diào)節(jié)功函數(shù)進而調(diào)整Vt。

c、MOSFET的工作原理

MOSFET的關(guān)鍵在于柵極,它控制著器件源漏的關(guān)閉和開啟,所以它如同水龍頭的開關(guān)。以NMOS為例(源漏為N-type,溝道和襯底是P-type),當(dāng)柵極加正電壓則襯底耦合感應(yīng)出少數(shù)載流子到溝道表面直到溝道表面反型,使源漏連通起來。整個過程中源漏的N-type與襯底的P-type這兩個PN結(jié)必須零偏或反偏(Source和Body接地,Drain接正電壓),所以他屬于PN結(jié)隔離型器件。

2、Scaling Side Effect: Small dimention Effect

引用《微機電系統(tǒng)基礎(chǔ)》的一段話(Page-9),“不是所有的東西小型化之后性能都會變好,有些物理效應(yīng)當(dāng)尺寸變小之后性能反而變差。因為有些對于宏觀范圍器件可以忽略的物理效應(yīng)在微觀尺寸突然變得很突出,這就是比例尺定律。比如跳蚤可以跳過自身高度的幾十倍,而大象卻做不到”。

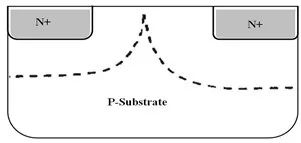

對于MOSFET來講,當(dāng)drain加反偏電壓的時候,PN結(jié)的耗盡區(qū)變寬會延伸到溝道區(qū),所以有效溝道長度Leff=Lpoly-2*Depletion,如果溝道長度足夠長則Leff近似等于Lpoly,可是當(dāng)Lpoly非常小的時候則耗盡區(qū)占Lpoly的比例則非常大而不可忽略,于是就有了短溝道效應(yīng)。

接下來我們討論等比例縮小帶來的一些列問題:

a、載流子速度飽和以及遷移率下降:

載流子在溝道里面的速度與溝道電場有關(guān),當(dāng)電場升高的時候,速度總會達到飽和的,這就是速度飽和效應(yīng),也就是為什么飽和區(qū)電流不隨Drain電壓的增加而增加了。而且在高電場下,載流子散射比較嚴重,也會導(dǎo)致遷移率下降,而且氧化層界面散射也會嚴重,所以載流子遷移率會進一步下降。

b、漏電壓導(dǎo)致勢壘降低:

另外一個短溝帶來的問題就是Drain端電壓改變了溝道表面勢壘,使得Vt降低。長溝器件的溝道勢壘是由柵極電壓Vg決定的,但是短溝器件的溝道勢壘是由柵源電壓(Vgs)和柵漏電壓(Vgd)決定的。如果漏極電壓升高,漏極PN結(jié)耗盡區(qū)會橫向延伸進入gate下面,所以在Vg比較低的情況下,溝道表面勢壘由于電場增加而降低,使得載流子還是能溜過去,這也叫亞閾值漏電(Subthreshold Leakage)。具體可見《MOS器件理論之–DIBL, GIDL》。

c、源漏穿通:

這個我感覺和DIBL沒什么差別,也是Drain端電壓帶來的問題,耗盡區(qū)寬度延伸進入溝道和源極的耗盡區(qū)不小心碰到一起了。和DIBL不一樣的是,一個是針對溝道勢壘而改變Vt,一個是針對源極導(dǎo)致漏電的。

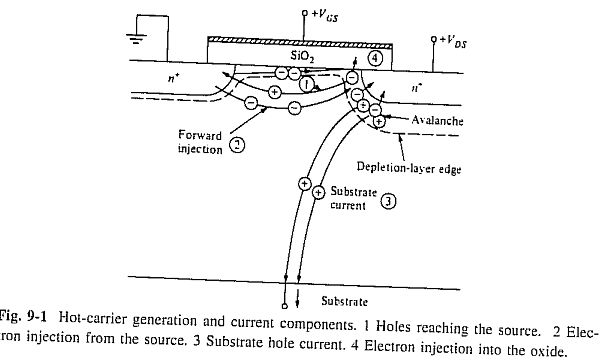

d、熱載流子效應(yīng):

這個也是一個道理了,溝道長度減小,溝道電場增加,如果Drain電壓增加,使得導(dǎo)致耗盡區(qū)延展,靠source更近了,也會進一步使得源漏橫向電場增強,所以溝道載流子碰撞激烈,產(chǎn)生很多的電子空穴對,而這些電子空穴對在柵極電壓下的驅(qū)使下進入襯底形成Isub。那為啥叫熱載流子呢?因為電場增加導(dǎo)致載流子加速,動能增加所以電子溫度升高了,只是你感受不到而已,那為什么通常都是NMOS比PMOS厲害呢,因為NMOS是電子,質(zhì)量小速度快,而PMOS是空穴質(zhì)量大速度小,而動能E=1/2*m*v^2,所以速度才是dominate。

3、Scaling時代的創(chuàng)新

a、遷移率加速器: 應(yīng)變硅(Strain Silicon)。

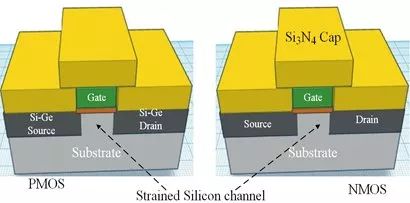

前面提到了當(dāng)器件縮小帶來的載流子遷移率下降問題,也不是無解。我們可以在溝道里用薄薄的鍺(Ge)材料來提高載流子遷移率,或者試用應(yīng)變硅引入溝道應(yīng)力來提升溝道載流子遷移率。而應(yīng)變硅技術(shù)包括使用張應(yīng)力(Tensile)和壓應(yīng)力(Compress)來提升載流子遷移率從而得到晶體管性能的提升,比如PMOS的空穴載流子就可以通過channel的壓應(yīng)力來實現(xiàn),這在45nm以下的時候就開始采用了 《Strained silicon — the key to sub-45 nm CMOS》。

對于制造溝道應(yīng)變硅,需要在源漏區(qū)域外延填充Si-Ge層(20%Ge + 80% Si混合),由于Ge原子比硅原子大,所以產(chǎn)生了推向溝道的壓應(yīng)力,從而使溝道的空穴載流子遷移率提高,進而提高了電流驅(qū)動能力和電路速度。這種技術(shù)最早是Intel在2003年用于90nm CMOS上,PMOS電流驅(qū)動能力提升25%。而這種源漏嵌入Si-Ge技術(shù)稱之為e-SiGe (Embedded-SiGe)技術(shù),但是Si-Ge應(yīng)變硅技術(shù)只能提升PMOS,而NMOS怎么辦呢?對于電子必須要有Tensile的Stress才能增強它的載流子遷移率,把SiGe嵌入到源漏肯定不行了,那就把他嵌入到溝道下面也可以產(chǎn)生Tensile應(yīng)力,但是這種工藝的實現(xiàn)難度幾乎不可能,所以后來就有了在NMOS周圍增加一個Si3N4,來產(chǎn)生額外的應(yīng)力。這種方法可以讓器件全部產(chǎn)生Compressive應(yīng)力也可以全部產(chǎn)生Tensile應(yīng)力,當(dāng)然也可以分別對PMOS產(chǎn)生Compressive而對NMOS產(chǎn)生Tensile,但是用這種SiN產(chǎn)生的應(yīng)力的晶體管對Poly Space的mismatch影響特別大(原因我還不知道。)

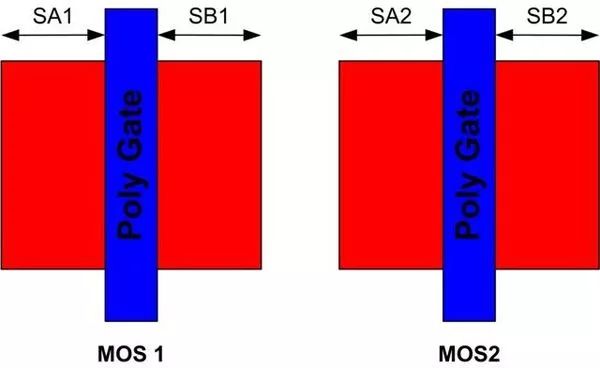

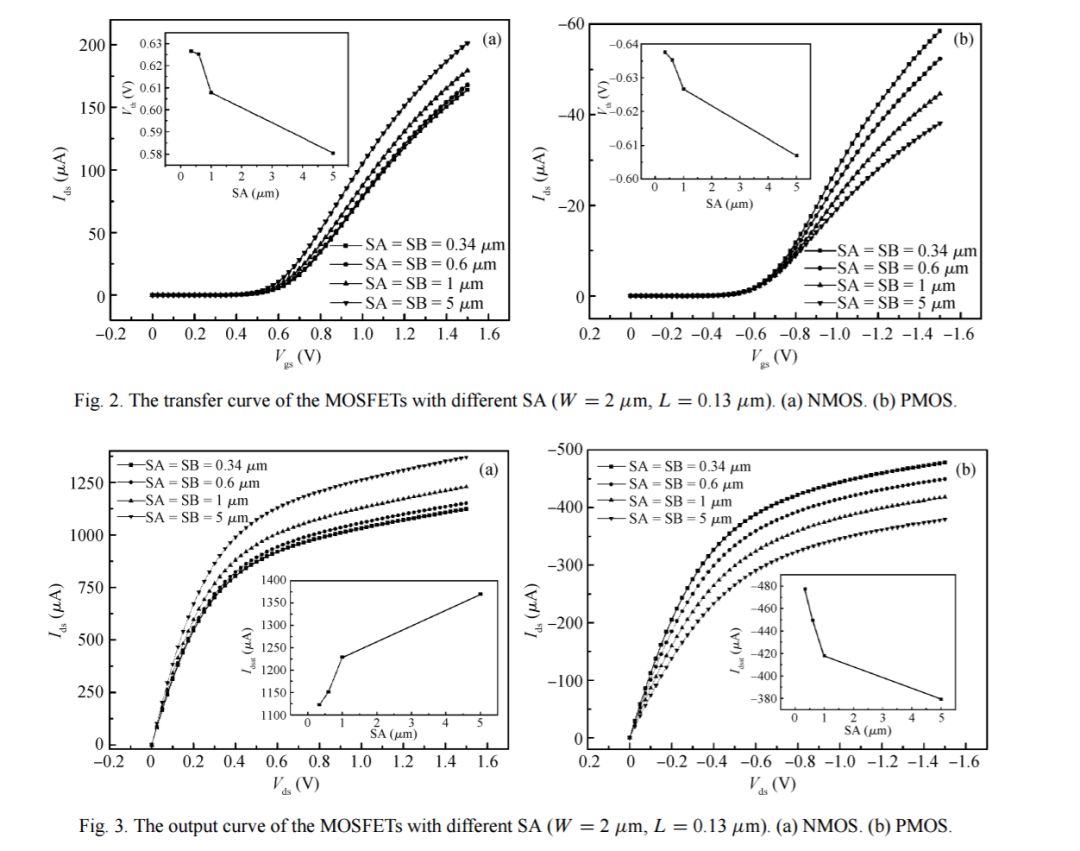

說到了應(yīng)變硅,這貌似都是12寸的理論,離我們很遙遠嗎?其實8寸也有這個問題,我們0.18um及其以下技術(shù)都有個效應(yīng)叫做LOD (Length of Drain/Diffusion),意思就是說溝道長度“L”的方向上有源區(qū)邊緣離溝道邊緣的距離對器件電流的影響,就是如下圖的SA和SB,這個器件影響在SPICE仿真里面在BSIM 4.0以上的模型就有了,所以在Analog電路仿真非常care mismatch的時候(如: Current mirror, Differential pair,ADC/DAC等電路)一定要帶入參數(shù)SA和SB,不要到時候又要來complain fab說mismatch不好。

原因是啥呢?主要是因為旁邊都是STI,里面的HDP Oxide產(chǎn)生了compressive應(yīng)力,所以按照e-SiGe的理論,PMOS的載流子遷移率會變大,而NMOS的載流子遷移率會變小,所以PMOS飽和電流會變大,NMOS的飽和電流會變小,如下圖I-V curve。

那接下來的問題是,如果我SA和SB全部畫成一樣不就好了嗎?模擬的世界你永遠不懂!

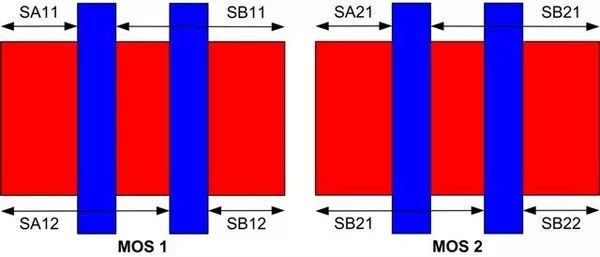

假設(shè)如下圖一個MOS有兩個Gate組成的multi finger呢?這里就更復(fù)雜了。。。。這里需要SA11=SA21、SB11=SB21、SA12=SA22且SB12=SB22,MOS1才能等于MOS2。

如果再進一步把MOS1和MOS放到一個大OD上去呢?里面就沒有問題了,可是最外面的SA和SB怎么辦?如何消除LOD的影響?只能把OD拉大了,通常是SA或SB>=5um即可,或者最外面的MOS不要用,也就是dummy gate。

所以說device里面STI的引入會帶來mismatch的原因知道了吧?

b、柵極漏電:High-K

柵極氧化層的厚度隨著等比例縮小也一直減薄,到65nm的時候需要有效柵氧厚度(EOT)接近23A( phsical 16A),再往下將就比自然氧化層還薄了,direct tunnel (Quantum Mechanical Tunneling)漏電根本無法承受。回過頭來想,我們?yōu)槭裁匆。恳驗槲覀円玫礁叩目鋵?dǎo)來感應(yīng)溝道反型,那夸導(dǎo)來自于什么?公式自己查一下就知道了來自于電容,要提升電容你要么降低厚度,要么提高介電常數(shù),既然降低厚度走不下去了,那就換介電常數(shù)吧。于是就有了High-K柵極介電材料。

High-K柵極材料的突破的突破來自于2007年,首次發(fā)明于Intel的45nm采用了HfO2 (Hafnium),它的介電常數(shù)是25,而我們的SiO2是3.9,自己比一下吧。

c、多晶耗盡效應(yīng): Metal Gate

我記得我以前的文章有講過HKMG,柵極材料如果是多晶,那么它的摻雜是隨著柵極電壓會發(fā)生改變的,柵極底部靠近柵氧的摻雜會被電場吸上去,而底部近似不摻雜的poly會變成絕緣體,被計入柵極氧化層厚度里,導(dǎo)致夸導(dǎo)降低。當(dāng)然除了改用High-K材料外,還有就是換金屬柵極,當(dāng)然不能是鋁,后面源漏激活的高溫受不了。所以必須是難熔金屬,而且必須有合適的功函數(shù),否則Vt就守不住了。

和High-K材料一樣,Metal Gate也是Intel率先在45nm上引入量產(chǎn)的,還是Intel牛啊。

4、器件結(jié)構(gòu)的創(chuàng)新

上面講的都是傳統(tǒng)的MOS結(jié)構(gòu),一直縮小遇到的各種問題及解法。但是總有黔驢技窮的時候,所以該結(jié)構(gòu)勢在必行!也就是現(xiàn)在流行的SOI和FinFET技術(shù)。主要目的就是最大化Gate-to-Channel電容并且最小化Drain-to-Channel電容。

a、SOI技術(shù):

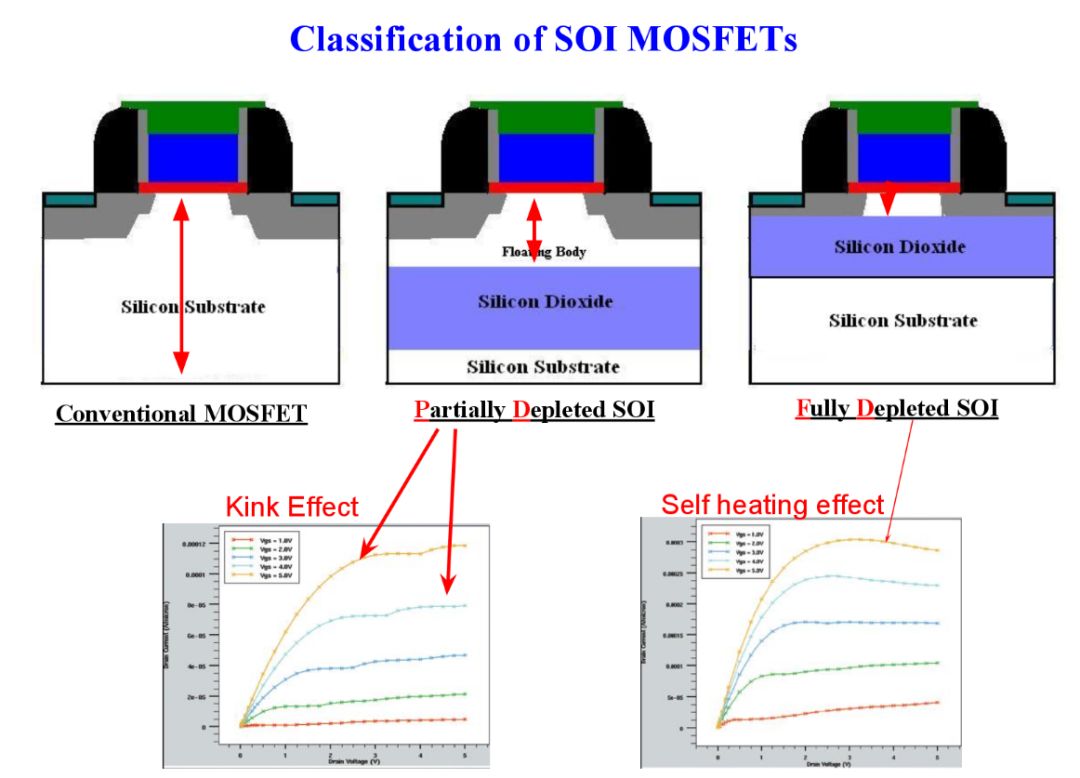

和傳統(tǒng)MOS最大不同是Well底部有個Oxide隔離著,所以叫做Silicon-on-Insulator (SOI),所以它還是傳統(tǒng)的Planar結(jié)構(gòu)。它的結(jié)構(gòu)分三部分,上面的Silicon是器件部分,中間的Oxide是Insulator隔離作用,底部的硅是支撐用的,也叫“Handle Silicon”。

MOS結(jié)構(gòu)上看有兩種,一種叫做PDSOI,一種叫FDSOI。前者是表面硅的厚度幾乎等于PN結(jié)深度,所以源漏PN結(jié)靠近Well的耗盡區(qū)就被Buried Oxide隔離掉了,所以傳統(tǒng)的PN結(jié)隔離該用了Oxide絕對隔離了,所以漏電非常小,寄生電容也變小了,所以電路變快了。但是這種器件當(dāng)柵極耗盡并反型的時候,表面溝道只有一兩百埃,所以溝道下面的硅還有一部分屬于Well/Bulk,所以這種SOI技術(shù)叫做部分耗盡SOI (PDSOI: Partial Depleted)。

那問題就來了,PDSOI的Bulk四周都被隔離了,Bulk的電極如果不接出去的話會帶來什么問題?對,浮體效應(yīng)(Floating Body Effect),所以Vt會拉低,電流會拉大,所以IV curve上你會看到包河區(qū)電流上翹,這就是Kink-Effect)。當(dāng)然如果要解決的話就是把襯底想法接出去即可,只是犧牲點面積而已。那么要解決襯底浮體的問題,又不想多接Bulk那怎么辦呢?也好辦,讓整個反型區(qū)全部耗盡即可,也就是FDSOI (Fully depleted),這樣結(jié)電容更小了,所以更快了,也叫RFSOI了。但是它也不是免費的午餐,這么薄的SOI (~200A)上的Silicon,制作工藝非常難,而且Silicon與下面的BOX的interface的漏電會導(dǎo)致溝道漏電的哦,還有這個溝道的self-heating會很嚴重。

b、FinFET:我不想再講了,太累了。大家自己看看我的前面文章吧 《FinFET-3D Transistor》。

最后講一下SOI和FinFET,SOI如果能夠取代FinFET,那自然是好,畢竟它還是Planar技術(shù),比較成熟。而且它還可以通過back-gate加上BOX來控制Vt,這在multi-Vt以及l(fā)ow power領(lǐng)域都是有優(yōu)勢的。

未來,讓我期待更先進的器件結(jié)構(gòu)及制造技術(shù),技術(shù)遠不止于此!比如碳納米管, nano-wire FET, FinFET+化合物半導(dǎo)體,等等。

-

IC

+關(guān)注

關(guān)注

36文章

5982瀏覽量

176224 -

cpu

+關(guān)注

關(guān)注

68文章

10904瀏覽量

213026 -

晶體管

+關(guān)注

關(guān)注

77文章

9746瀏覽量

138907

原文標(biāo)題:精華 | 關(guān)于集成電路制造“技術(shù)”的簡史

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

集成電路的技術(shù)和產(chǎn)業(yè)鏈的詳細資料大全

#硬聲創(chuàng)作季 #集成電路 集成電路制造工藝-01.1.2集成電路制造工藝發(fā)展歷史-發(fā)展歷史

#硬聲創(chuàng)作季 #集成電路 集成電路制造工藝-01.1.4集成電路制造工藝發(fā)展歷史-半導(dǎo)體集成電路介紹

集成電路制造技術(shù)的發(fā)展歷史詳細介紹

集成電路制造技術(shù)的發(fā)展歷史詳細介紹

評論