過(guò)去,設(shè)計(jì)人員傾向于使用現(xiàn)場(chǎng)可編程門陣列 (FPGA) 在硬件設(shè)計(jì)中提升計(jì)算密集型應(yīng)用的性能,例如計(jì)算機(jī)視覺(jué)、通信、工業(yè)嵌入式系統(tǒng),以及越來(lái)越多的物聯(lián)網(wǎng) (IoT)。然而,傳統(tǒng) FPGA 編程中涉及的繁瑣步驟一直讓人望而卻步,促使設(shè)計(jì)人員到目前都還在尋求替代處理解決方案。

基于 Jupyter 筆記本的 Python Productivity for Zynq (PYNQ) 開(kāi)發(fā)環(huán)境的問(wèn)世,解決了 FPGA 的可編程性問(wèn)題。使用專為支持 PYNQ 而設(shè)計(jì)的開(kāi)發(fā)板,即使 FPGA 經(jīng)驗(yàn)很少的開(kāi)發(fā)人員也可快速實(shí)現(xiàn)相關(guān)設(shè)計(jì),從而充分利用 FPGA 性能來(lái)加快計(jì)算密集型應(yīng)用。

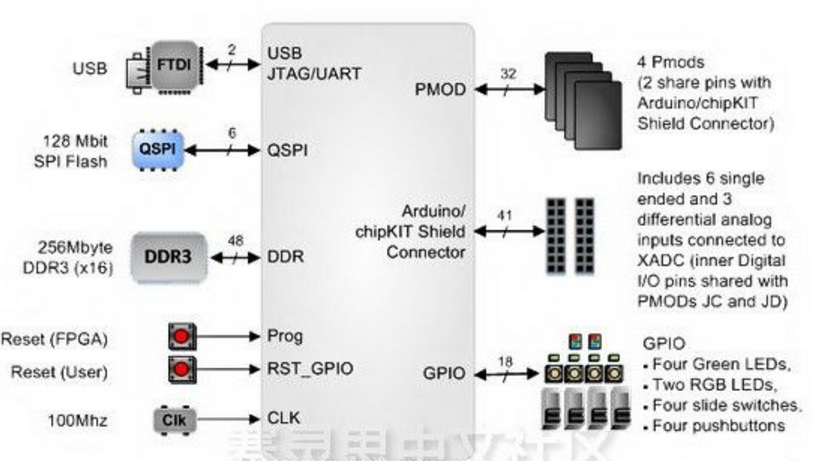

本文將說(shuō)明典型的 FPGA 方法,然后介紹并演示如何開(kāi)始使用 Digilent 的開(kāi)發(fā)板。該開(kāi)發(fā)板為快速開(kāi)發(fā)基于 FPGA 的系統(tǒng)提供了一種強(qiáng)大的開(kāi)源替代方法。

為何使用 FPGA?

若需要使用計(jì)算密集型復(fù)雜算法,工程師常常依賴 FPGA 提高執(zhí)行速度,同時(shí)又不影響緊張的功率預(yù)算。實(shí)際上,F(xiàn)PGA 已成為在邊緣計(jì)算系統(tǒng)中提高人工智能算法速度的主流平臺(tái)。

更先進(jìn)的 FPGA 片上系統(tǒng) (SoC) 器件專為嵌入式應(yīng)用而設(shè)計(jì),將可編程邏輯 (PL) 結(jié)構(gòu)與微控制器集成在一起。例如,Xilinx 的 Zynq-7000 SoC 在集成式可編程邏輯 (PL) 結(jié)構(gòu)中結(jié)合了一個(gè) Arm? Cortex?-A9 雙核處理器系統(tǒng),以及最多 444,000 個(gè)邏輯單元(圖 1)。除了內(nèi)置處理器和全套外設(shè)外,Zynq SoC 還提供最多 2,020 個(gè)數(shù)字信號(hào)處理 (DSP) 塊(或稱切片)。開(kāi)發(fā)人員使用這些資源,便可將 PL 結(jié)構(gòu)配置到專用的處理鏈中,以便在復(fù)雜的計(jì)算密集型算法中提高吞吐量。

圖 1:Xilinx 的 Zynq-7000 SoC 結(jié)合了 Arm Cortex-A9 雙核處理器、可編程邏輯結(jié)構(gòu),以及很多嵌入式應(yīng)用中所需的全套外設(shè)和接口。(圖片來(lái)源:Xilinx)

除了可減少元器件數(shù)量外,處理器與 PL 結(jié)構(gòu)的集成還允許通過(guò)片上總線而不是片外訪問(wèn)來(lái)執(zhí)行運(yùn)算。這種集成也進(jìn)一步簡(jiǎn)化了在上電或復(fù)位序列期間,加載 PL 結(jié)構(gòu)的關(guān)鍵任務(wù)。

在使用 FPGA 構(gòu)建的基于微控制器的典型系統(tǒng)中,開(kāi)發(fā)人員需要管理用于加載 FPGA 編程比特流的序列和安全性。在 Zynq SoC 中,集成的處理器負(fù)責(zé)執(zhí)行常規(guī)微控制器的任務(wù),包括管理 PL 結(jié)構(gòu)和其他片上外設(shè)。因此,與傳統(tǒng)的 FPGA 比特流初始化相比,該 FPGA 加載過(guò)程更接近于常規(guī)微控制器的引導(dǎo)過(guò)程。

該引導(dǎo)過(guò)程通過(guò)由其中一個(gè) Zynq 處理器管理的短步驟序列完成(圖 2)。上電或復(fù)位時(shí),如果 Zynq 處理器執(zhí)行其只讀 BootROM 中的一小段代碼,以從引導(dǎo)設(shè)備獲取實(shí)際引導(dǎo)代碼,則引導(dǎo)過(guò)程開(kāi)始。除了用于配置處理器系統(tǒng)組件的代碼外,引導(dǎo)代碼還包含 PL 比特流以及用戶應(yīng)用。當(dāng)引導(dǎo)代碼加載完成時(shí),處理器使用其中包含的比特流來(lái)配置 PL。而完成組件和 PL 的配置后,該器件開(kāi)始執(zhí)行引導(dǎo)代碼中包含的應(yīng)用。

圖 2:在類似于常規(guī)微控制器的引導(dǎo)序列中,Xilinx 的 Zynq-7000 SoC 運(yùn)行 Boot ROM 中的代碼來(lái)加載和執(zhí)行引導(dǎo)加載程序,該加載程序負(fù)責(zé)處理后續(xù)階段,包括使用引導(dǎo)代碼中封裝的比特流來(lái)配置可編程邏輯結(jié)構(gòu)。(圖片來(lái)源:Xilinx)

即使有了簡(jiǎn)化的 PL 加載處理,開(kāi)發(fā)人員在過(guò)去仍需自行處理復(fù)雜的 FPGA 開(kāi)發(fā)過(guò)程,才能生成所需比特流。對(duì)于希望利用 FPGA 性能的開(kāi)發(fā)人員來(lái)說(shuō),傳統(tǒng)的 FGPA 開(kāi)發(fā)過(guò)程仍然是他們實(shí)現(xiàn)設(shè)計(jì)的一大障礙。Xilinx 通過(guò)其 PYNQ 環(huán)境有效地消除了這一障礙。

PYNQ 環(huán)境

在 PYNQ 中,PL 比特流封裝在預(yù)先構(gòu)建的庫(kù)中。這些庫(kù)稱為覆蓋層,在開(kāi)發(fā)過(guò)程和執(zhí)行環(huán)境中,其角色與軟件庫(kù)類似。在引導(dǎo)加載過(guò)程中,與所需覆蓋層相關(guān)聯(lián)的比特流將配置 PL 結(jié)構(gòu)。不過(guò),對(duì)于通過(guò)與每個(gè)覆蓋層關(guān)聯(lián)的 Python 應(yīng)用程序編程接口 (API) 來(lái)利用覆蓋層功能的開(kāi)發(fā)人員而言,該過(guò)程保持透明。在開(kāi)發(fā)過(guò)程中,工程師可以根據(jù)需要組合軟件庫(kù)和覆蓋層,通過(guò)其各自 API 來(lái)實(shí)現(xiàn)應(yīng)用。在執(zhí)行過(guò)程中,處理器系統(tǒng)像往常一樣執(zhí)行軟件庫(kù)代碼,而 PL 結(jié)構(gòu)負(fù)責(zé)實(shí)現(xiàn)覆蓋層中提供的功能。這樣做的結(jié)果是可以提升性能,從而進(jìn)一步促使開(kāi)發(fā)人員對(duì)日益嚴(yán)苛應(yīng)用進(jìn)行 FPGA 設(shè)計(jì)的興趣。

顧名思義,PYNQ 利用了與 Python 編程語(yǔ)言相關(guān)的更高開(kāi)發(fā)生產(chǎn)力。Python 之所以能夠成為頂級(jí)語(yǔ)言之一,不僅是因?yàn)槠湎鄬?duì)簡(jiǎn)單,還因?yàn)樗哂旋嫶笄也粩鄶U(kuò)增的生態(tài)系統(tǒng)。開(kāi)發(fā)人員可能會(huì)在 Python 開(kāi)源模塊的存儲(chǔ)庫(kù)中,找到支持服務(wù)或?qū)S盟惴ㄋ璧能浖?kù)。與此同時(shí),開(kāi)發(fā)人員可以使用 C 語(yǔ)言實(shí)現(xiàn)關(guān)鍵功能,因?yàn)?PYNQ 使用常見(jiàn) C 語(yǔ)言實(shí)現(xiàn) Python 解釋器。該實(shí)現(xiàn)允許輕松訪問(wèn)數(shù)千個(gè)現(xiàn)有 C 語(yǔ)言庫(kù),并簡(jiǎn)化開(kāi)發(fā)人員提供的 C 語(yǔ)言庫(kù)的使用。盡管經(jīng)驗(yàn)豐富的開(kāi)發(fā)人員可以使用專用硬件覆蓋層和 C 語(yǔ)言軟件庫(kù)來(lái)擴(kuò)展 PYNQ,但是 PYNQ 的真正優(yōu)勢(shì)在于,它可為任何能夠構(gòu)建 Python 程序的開(kāi)發(fā)人員提供高生產(chǎn)力開(kāi)發(fā)環(huán)境。

PYNQ 本身是一個(gè)開(kāi)源項(xiàng)目,基于另一個(gè)開(kāi)源項(xiàng)目(Jupyter 筆記本)而構(gòu)建。針對(duì)通過(guò)交互方式探索算法,以及使用 Python 或任何其他受支持的編程語(yǔ)言(目前超過(guò) 40 種)對(duì)復(fù)雜應(yīng)用進(jìn)行原型開(kāi)發(fā),Jupyter 筆記本可提供極其有效的環(huán)境。Jupyter 筆記本由 Project Jupyter 基于社區(qū)共識(shí)而開(kāi)發(fā),將可執(zhí)行代碼行與描述文本和圖形結(jié)合在一起。這一功能使各開(kāi)發(fā)人員能夠更有效地記錄進(jìn)展,而無(wú)需轉(zhuǎn)到其他開(kāi)發(fā)環(huán)境。例如,開(kāi)發(fā)人員可以使用筆記本,將查看數(shù)據(jù)所需的數(shù)行代碼與代碼生成的圖形結(jié)合起來(lái)(圖 3)。

圖 3:來(lái)自 Xilinx 樣例存儲(chǔ)庫(kù)的 Jupyter 筆記本將描述文本、可執(zhí)行代碼以及與應(yīng)用相關(guān)的輸出結(jié)合起來(lái)。(圖片來(lái)源:Xilinx)

Jupyter 筆記本之所以能夠同時(shí)包含代碼、輸出和描述文本,是因?yàn)樗且环N活動(dòng)文檔,并在 Jupyter 筆記本服務(wù)器提供的交互式開(kāi)發(fā)環(huán)境中進(jìn)行維護(hù)(圖 4)。在 Jupyter 會(huì)話中,服務(wù)器使用 HTTP 協(xié)議在常規(guī) Web 瀏覽器中呈現(xiàn)筆記本文件,并對(duì)所呈現(xiàn)文檔中的靜態(tài)和動(dòng)態(tài)內(nèi)容應(yīng)用 HTTP 和 Websocket 協(xié)議。在后端,服務(wù)器使用 ZeroMQ (?MQ) 開(kāi)源消息傳遞協(xié)議與代碼執(zhí)行內(nèi)核通信。

圖 4:在 Jupyter 會(huì)話中,筆記本服務(wù)器將筆記本文件的內(nèi)容呈現(xiàn)到 Web 瀏覽器,同時(shí)與執(zhí)行代碼的后端內(nèi)核進(jìn)行交互。

-

微控制器

+關(guān)注

關(guān)注

48文章

7651瀏覽量

152116 -

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606022 -

python

+關(guān)注

關(guān)注

56文章

4807瀏覽量

85040

原文標(biāo)題:使用Python和Jupyter筆記本快速構(gòu)建基于FPGA的設(shè)計(jì)并進(jìn)行編程

文章出處:【微信號(hào):FPGA-EETrend,微信公眾號(hào):FPGA開(kāi)發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

開(kāi)發(fā)者福利 一文帶你了解Digilent Arty S7 FPGA開(kāi)發(fā)板

fpga開(kāi)發(fā)板的新手,如何開(kāi)始使用引腳分配

Digilent公司推出新型FPGA硬件開(kāi)發(fā)平臺(tái):NEXYSTM3開(kāi)發(fā)板

Digilent公司basys2開(kāi)發(fā)板的全套開(kāi)發(fā)例程

Digilent公司發(fā)布新款FPGA開(kāi)發(fā)板

digilent Virtex-5 FPGA開(kāi)發(fā)板簡(jiǎn)介

digilent Spartan-7開(kāi)源創(chuàng)客開(kāi)發(fā)板介紹

digilent Artix-7 FPGA開(kāi)發(fā)板簡(jiǎn)介

開(kāi)始使用 RL78/G14 快速原型開(kāi)發(fā)板/Wi-Fi-Pmod-Expansion-Board

開(kāi)始使用 RL78/G14快速原型開(kāi)發(fā)板/Wi-Fi-Pmod-Expansion-Board

典型的FPGA方法:如何開(kāi)始使用Digilent的開(kāi)發(fā)板

典型的FPGA方法:如何開(kāi)始使用Digilent的開(kāi)發(fā)板

評(píng)論