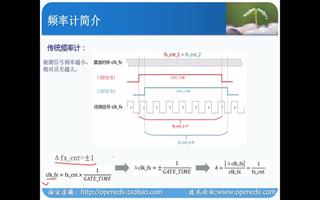

測(cè)量頻率的方法有很多,按照其工作原理分為無(wú)源測(cè)頻法、比較法、示波器法和計(jì)數(shù)法等。計(jì)數(shù)法在實(shí)質(zhì)上屬于比較法,其中最常用的方法是電子計(jì)數(shù)器法。電子計(jì)數(shù)器是一種最常見(jiàn)、最基本的數(shù)字化測(cè)量?jī)x器。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

示波器

+關(guān)注

關(guān)注

113文章

6282瀏覽量

185841 -

頻率計(jì)

+關(guān)注

關(guān)注

8文章

177瀏覽量

44483 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2261瀏覽量

94983

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

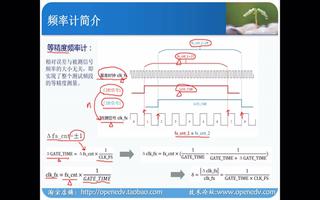

#硬聲創(chuàng)作季 #FPGA Zedboard教程-20 等精度頻率計(jì)的原理分析和實(shí)例實(shí)現(xiàn)-3

fpga頻率計(jì)實(shí)例

水管工

發(fā)布于 :2022年11月04日 02:56:34

#硬聲創(chuàng)作季 #FPGA Zedboard教程-20 等精度頻率計(jì)的原理分析和實(shí)例實(shí)現(xiàn)-4

fpga頻率計(jì)實(shí)例

水管工

發(fā)布于 :2022年11月04日 02:56:59

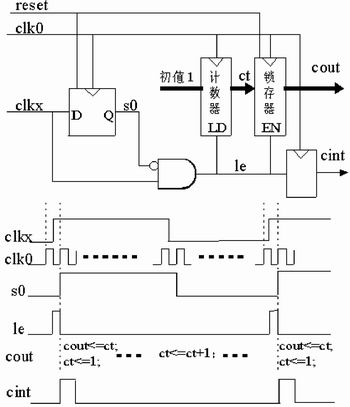

基于FPGA的等精度頻率計(jì)的設(shè)計(jì)與實(shí)現(xiàn)

基于FPGA的等精度頻率計(jì)的設(shè)計(jì)與實(shí)現(xiàn)摘 要:利用等精度測(cè)量原理,通過(guò)FPGA運(yùn)用VHDL編程設(shè)計(jì)一個(gè)數(shù)字式

發(fā)表于 08-19 09:46

頻率計(jì)精度問(wèn)題

我用51單片機(jī)的內(nèi)部定時(shí)/計(jì)數(shù)器做頻率計(jì)實(shí)驗(yàn),但是在仿真時(shí)出現(xiàn)較大的誤差,如從int0引入外部脈沖,如設(shè)置頻率為500Hz實(shí)際測(cè)量為542Hz,設(shè)置為1k,實(shí)際測(cè)量為1084hz。具體的軟件算法

發(fā)表于 05-01 16:24

【正點(diǎn)原子FPGA連載】第二十二章頻率計(jì)實(shí)驗(yàn)-領(lǐng)航者ZYNQ之FPGA開(kāi)發(fā)指南

原子公眾號(hào),獲取最新資料第二十二章頻率計(jì)實(shí)驗(yàn)數(shù)字頻率計(jì)是一種基本的測(cè)量?jī)x器,被廣泛應(yīng)用于航天、電子、測(cè)控等領(lǐng)域。基于傳統(tǒng)測(cè)頻原理的頻率計(jì)的測(cè)

發(fā)表于 09-27 17:54

【正點(diǎn)原子FPGA連載】第二十二章頻率計(jì)實(shí)驗(yàn)-領(lǐng)航者ZYNQ之FPGA開(kāi)發(fā)指南

原子公眾號(hào),獲取最新資料第二十二章頻率計(jì)實(shí)驗(yàn)數(shù)字頻率計(jì)是一種基本的測(cè)量?jī)x器,被廣泛應(yīng)用于航天、電子、測(cè)控等領(lǐng)域。基于傳統(tǒng)測(cè)頻原理的頻率計(jì)的測(cè)

發(fā)表于 09-28 18:10

基于FPGA的同步測(cè)周期高精度數(shù)字頻率計(jì)的設(shè)計(jì)

摘 要:本文介紹了一種同步測(cè)周期計(jì)數(shù)器的設(shè)計(jì),并基于該計(jì)數(shù)器設(shè)計(jì)了一個(gè)高精度的數(shù)字頻率計(jì)。文中給出了計(jì)數(shù)器的VHDL編碼,并對(duì)頻率計(jì)的FPGA實(shí)

發(fā)表于 03-24 13:31

?2034次閱讀

基于FPGA的等精度頻率計(jì)的設(shè)計(jì)與實(shí)現(xiàn)

本文介紹了一種利用FPGA實(shí)現(xiàn)DC~100 MHz的自動(dòng)切換量程數(shù)字等精度頻率計(jì)的實(shí)現(xiàn)方法,并給出實(shí)現(xiàn)代碼。整個(gè)系統(tǒng)在研制的CPLD/FPGA實(shí)驗(yàn)

發(fā)表于 12-03 11:17

?5843次閱讀

正點(diǎn)原子開(kāi)拓者FPGA:頻率計(jì)實(shí)驗(yàn)

頻率計(jì)又稱(chēng)為頻率計(jì)數(shù)器,是一種專(zhuān)門(mén)對(duì)被測(cè)信號(hào)頻率進(jìn)行測(cè)量的電子測(cè)量?jī)x器。頻率計(jì)主要由四個(gè)部分構(gòu)成:時(shí)基(T)電路、輸入電路、計(jì)數(shù)顯示電路以及控制電路。

【正點(diǎn)原子FPGA連載】第二十五章HDMI方塊移動(dòng)實(shí)驗(yàn) -摘自【正點(diǎn)原子】新起點(diǎn)之FPGA開(kāi)發(fā)指南_V2.1

【正點(diǎn)原子FPGA連載】第二十五章HDMI方塊移動(dòng)實(shí)驗(yàn) -摘自【正點(diǎn)原子】新起點(diǎn)之

發(fā)表于 11-24 14:36

?13次下載

【正點(diǎn)原子FPGA連載】第九章按鍵控制LED燈實(shí)驗(yàn) -摘自【正點(diǎn)原子】新起點(diǎn)之FPGA開(kāi)發(fā)指南_V2.1

【正點(diǎn)原子FPGA連載】第九章按鍵控制LED燈實(shí)驗(yàn) -摘自【正點(diǎn)原子】新起點(diǎn)之

發(fā)表于 12-04 13:06

?10次下載

【正點(diǎn)原子FPGA連載】第三十七章雙路高速AD實(shí)驗(yàn) -摘自【正點(diǎn)原子】新起點(diǎn)之FPGA開(kāi)發(fā)指南_V2.1

【正點(diǎn)原子FPGA連載】第三十七章雙路高速AD實(shí)驗(yàn) -摘自【正點(diǎn)原子】新起點(diǎn)之

發(fā)表于 12-04 15:06

?11次下載

【正點(diǎn)原子FPGA連載】第三十五章高速AD/DA實(shí)驗(yàn) -摘自【正點(diǎn)原子】新起點(diǎn)之FPGA開(kāi)發(fā)指南_V2.1

【正點(diǎn)原子FPGA連載】第三十五章高速AD/DA實(shí)驗(yàn) -摘自【正點(diǎn)原子】新起點(diǎn)之

發(fā)表于 12-04 15:06

?12次下載

【正點(diǎn)原子FPGA連載】第十五章 窗口門(mén)狗(WWDG)實(shí)驗(yàn) -摘自【正點(diǎn)原子】新起點(diǎn)之FPGA開(kāi)發(fā)指南_V2.1

【正點(diǎn)原子FPGA連載】第十五章 窗口門(mén)狗(WWDG)實(shí)驗(yàn) -摘自【正點(diǎn)原子】新起點(diǎn)之

發(fā)表于 12-05 11:21

?12次下載

正點(diǎn)原子FPGA:精度頻率計(jì)實(shí)驗(yàn)

正點(diǎn)原子FPGA:精度頻率計(jì)實(shí)驗(yàn)

評(píng)論