電源時序控制是微控制器、FPGA、DSP、ADC 和其他需要多個電壓軌供電的器件所必需的一項功能。這些應用通常需要在數(shù)字 I/O 軌上電前對內(nèi)核和模擬模塊上電,但有些設計可能需要采用其他序列。無論如何,正確的上電和關(guān)斷時序控制可以防止閂鎖引發(fā)的即時損壞和 ESD 造成的長期損害。此外,電源時序控制可以錯開上電過程中的浪涌電流,這種技術(shù)對于采用限流電源供電的應用十分有用。

本文討論使用分立器件進行電源時序控制的優(yōu)缺點,同時介紹利用 ADP5134 內(nèi)部精密使能引腳實現(xiàn)時序控制的一種簡單而有效的方法。ADP5134 內(nèi)置 2 個 1.2-A 降壓調(diào)節(jié)器與 2 個300-mA LDO。同時,本文還列出一系列 IC,可用于要求更高精度、更靈活時序控制的應用。

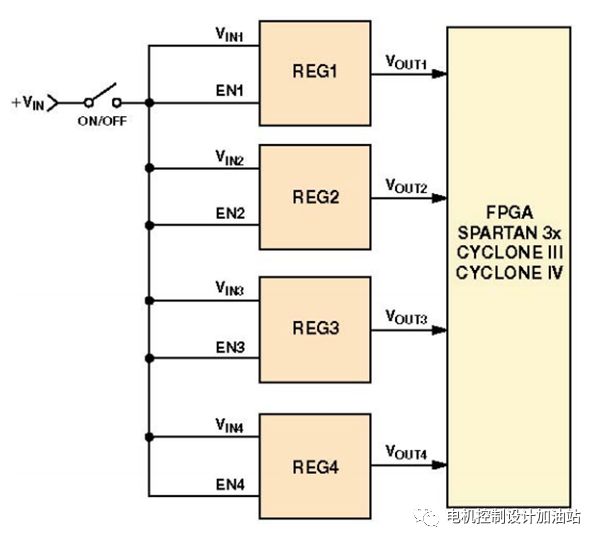

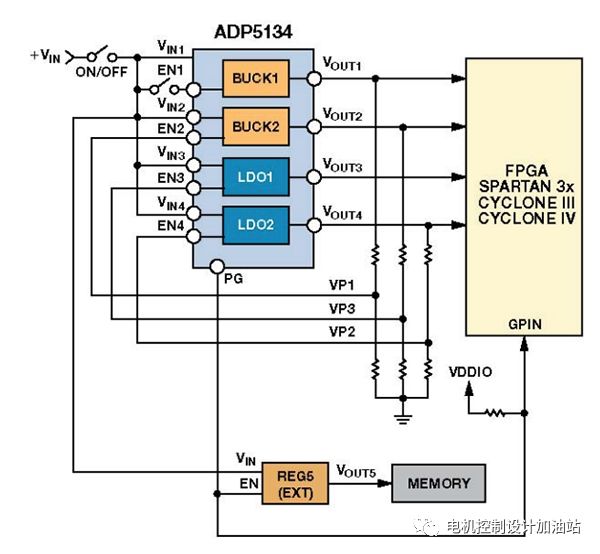

圖 1 所示為一種要求多個供電軌的應用。這些供電軌為內(nèi)核電源(VCCINT)、I/O 電源(VCCO)、輔助電源(VCCAUX)和系統(tǒng)存儲器電源。

圖 1. 處理器和 FPGA 的典型供電方法

舉例來說,Xilinx? Spartan-3A FPGA 具有一個內(nèi)置上電復位電路,可確保在所有電源均達到其閾值后才允許對器件進行配置。這樣有助于降低電源時序控制要求,但為了實現(xiàn)最小浪涌電流電平并遵循連接至 FPGA 的電路時序控制要求,供電軌應當按以下序列上電:VCC_INT a VCC_AUX a VCCO。請注意:有些應用要求采用特定序列,因此,務必閱讀數(shù)據(jù)手冊的電源要求部分。

使用無源延遲網(wǎng)絡簡化電源時序控制

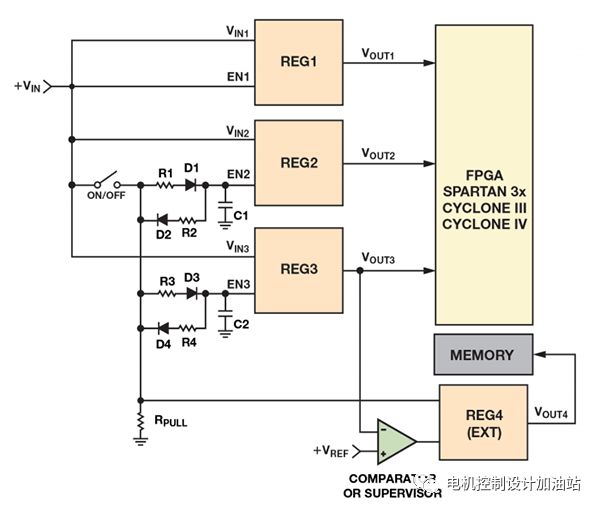

實現(xiàn)電源時序控制的一種簡單的方法就是利用電阻、電容、二極管等無源元件,延遲進入調(diào)節(jié)器使能引腳的信號,如圖 2 所示。當開關(guān)閉合時,D1 導電,而 D2 仍保持斷開。電容 C1 充電,而 EN2 處的電壓根據(jù) R1 和 C1 確定的速率上升。當開關(guān)斷開時,電容 C1 通過 R2、D2 和 RPULL向地放電。EN2 處的電壓以 R2、RPULL和 C2 確定的速率下降。更改 R1 和 R2 的值會改變充放電時間,從而設置調(diào)節(jié)器的開啟和關(guān)閉時間。

圖 2. 利用電阻、電容和二極管實現(xiàn)電源時序控制的簡單方法

該方法可用于不要求采用精密時序控制的應用,以及只需延遲信號即可并可能只要求采用外部 R 和 C 的部分應用。對于標準調(diào)節(jié)器,采用這種方法的缺點在于,使能引腳的邏輯閾值可能因為電壓和溫度而存在很大的差異。此外,電壓斜坡中的延遲取決于電阻和電容值及容差。典型的 X5R 電容在–55°C 至+85°C 溫度范圍內(nèi)的變化幅度約為±15%,由于直流偏置效應還會出現(xiàn)±10%的變化,從而使時序控制變得不精確,有時還會變得不可靠。

精密使能輕松實現(xiàn)時序控制

為了獲得穩(wěn)定的閾值電平以實現(xiàn)精密時序控制,大多數(shù)調(diào)節(jié)器都要求采用一個外部基準電壓源。ADP5134 通過集成精密基準電壓源、大幅節(jié)省成本和 PCB 面積的方式解決了這個問題。每個調(diào)節(jié)器都有一個獨立的使能引腳。當使能輸入的電壓升至VIH_EN (最小值為 0.9 V)以上時,器件退出關(guān)斷模式,且管理模塊開啟,但不會激活調(diào)節(jié)器。將使能輸入的電壓與一個精密內(nèi)部基準電壓(典型值為 0.97 V)相比較。一旦使能引腳的電壓升至高于精密使能閾值,則調(diào)節(jié)器被激活,輸出電壓開始升高。在輸入電壓和溫度轉(zhuǎn)折處,基準電壓的變化幅度只有±3%。這一小范圍變化可確保精密的時序控制,解決采用分立器件時遇到的各種問題。

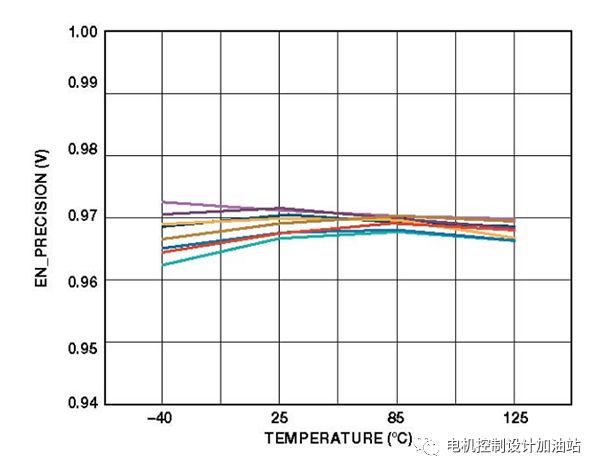

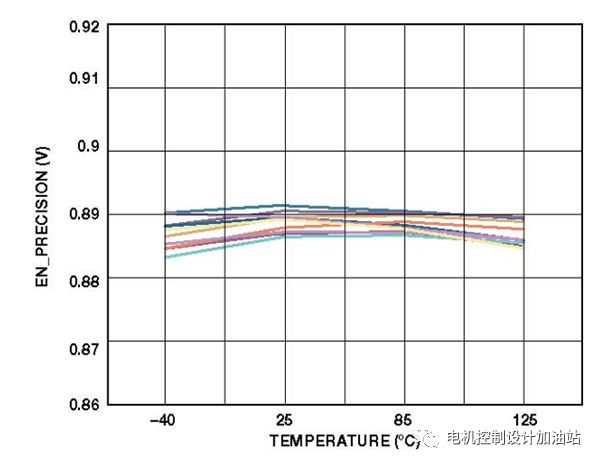

當使能輸入的電壓降至低于基準電壓低 80 mV(典型值)時,調(diào)節(jié)器停用。當所有使能輸入上的電壓都降至 VIL_EN(最大值為 0.35 V)以下時,器件進入關(guān)斷模式。在該模式下,功耗降至 1 μA 以下。圖 3 和圖 4 展示了用于 Buck1 的 ADP5134 精密使能閾值在溫度范圍內(nèi)的精度。

圖 3. 溫度范圍內(nèi)的精密使能導通閾值(10 個采樣)

圖 4. 溫度范圍內(nèi)的精密使能關(guān)閉閾值(10 個采樣)

使用電阻分壓器簡化電源時序控制

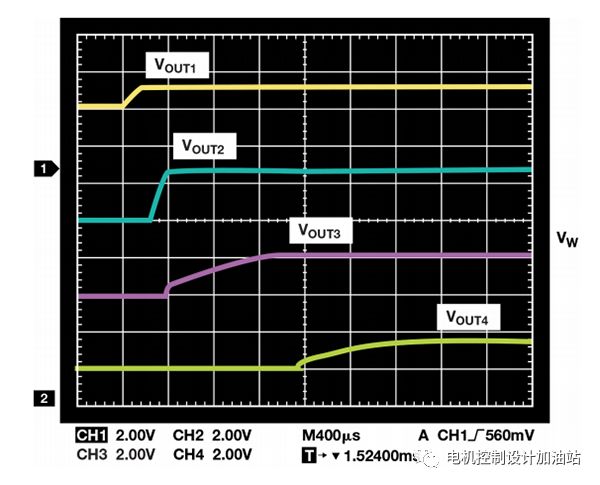

通過將衰減版本的調(diào)節(jié)器輸出端連接至待上電的下一個調(diào)節(jié)器使能引腳,可對多通道電源進行時序控制,如圖 5 所示,其中,調(diào)節(jié)器按以下順序開啟或關(guān)閉:Buck1 a Buck2 a LDO1a LDO2。圖 6 為 EN1 連接至 VIN1后的上電序列。圖 7 所示為EN1 與 VIN1斷開后的關(guān)斷序列。

圖 5. 采用 ADP5134 實現(xiàn)的簡單時序控制

圖 6. ADP5134 啟動序列

圖 7. ADP5134 關(guān)斷序列

序列器 IC 提高時序精度

在某些情況下,實現(xiàn)精密時序比降低 PCB 面積和成本更重要。對于這些應用,可以使用電壓監(jiān)控和序列器 IC,比如在電壓和溫度范圍內(nèi),精度可達±0.8%的 ADM1184 四通道電壓監(jiān)控器。或者,對于要求更加精確的上電和關(guān)斷序列控制的應用,可以使用帶可編程時序控制的 ADM1186 四通道電壓序列器和監(jiān)控器。

ADP5034 四通道調(diào)節(jié)器集成了兩個 3-MHz、1200-mA 降壓調(diào)節(jié)器和兩個 300 mA LDO。典型的時序控制功能可以通過以下方式實現(xiàn),采用 ADM1184 監(jiān)控一個調(diào)節(jié)器的輸出電壓,并在被監(jiān)測輸出電壓達到某個電平時,向下一個調(diào)節(jié)器的使能引腳提供一個邏輯高電平信號。這種方法(如圖 8 所示)可用于不具有精密使能功能的調(diào)節(jié)器。

結(jié)論

使用 ADP5134 精密使能輸入進行時序控制既簡單又輕松,每個通道只需要兩個外部電阻即可。而更加精密的時序控制則可以通過 ADM1184 或 ADM1186 電壓監(jiān)控器實現(xiàn)。

圖 8. 使用 ADM1184 四通道電壓監(jiān)控器對 ADP5034 四通道調(diào)節(jié)器實施時序控制

-

電源

+關(guān)注

關(guān)注

184文章

17841瀏覽量

251800 -

延遲

+關(guān)注

關(guān)注

1文章

70瀏覽量

13585

原文標題:輕松實現(xiàn)復雜電源時序控制

文章出處:【微信號:motorcontrol365,微信公眾號:電機控制設計加油站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

點到多點無源光網(wǎng)絡有哪些優(yōu)點

無源蜂鳴器怎么用電腦控制

電源時序器輸出電壓多少伏

電源時序器的原理及使用方法是什么

電源時序器常見故障維修

無源繼電器如何工作的

無源繼電器輸出什么意思?

高阻無源探頭的工作原理和用途及其使用技巧

輕松實現(xiàn)復雜的電源時序控制

使用無源延遲網(wǎng)絡簡化電源時序控制

使用無源延遲網(wǎng)絡簡化電源時序控制

評論