集成電路設計自動化軟件領導企業新思(Synopsys)近日宣布,面向三星7LPP(7nm Low Power Plus)和更先進工藝的良率學習平臺設計取得最大突破,也為三星后續5nm、4nm、3nm工藝的量產和良品率奠定了堅實基礎。

量產探索平臺(Yield Explorer)是一種復雜的芯片量產良品率學習平臺,可用來分析芯片設計、晶圓廠生產、產品測試三大方面的數據,以便幫助工程師找到缺點、改進良品率、提高產能。

現代芯片設計和生產是極為復雜的過程,往往涉及幾千個步驟,需要花費數月時間,而芯片的最終良品率取決于整體設計、性能和功耗需求等,因此要想提高芯片生產的成功率,需要對各種因素進行細致的分析。

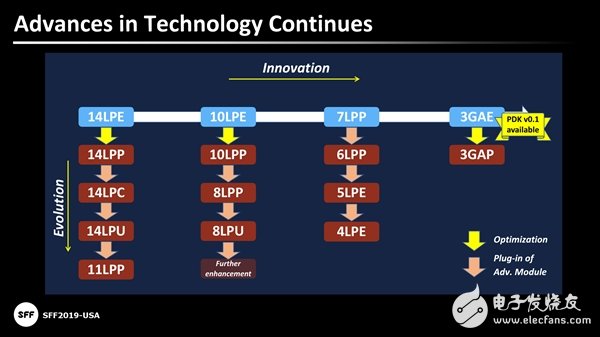

根據路線圖,三星工藝近期有14nm、10nm、7nm、3nm三個重要節點,其中14nm會演化出11nm,10nm會演化出8nm,7nm則會演化出6nm、5nm、4nm。

而每種工藝往往又會根據性能、功耗的不同而分為多個版本,比如14nm分成了14LPE、14LPP、14LPC、14LPU,3nm則分成3GAE、3GAP,預計會采用全新的材料。

目前,三星已經完成5nm工藝的設計工作,正在加速推進投入量產,4nm則將在今年下半年完成開發,新思的新平臺將在其中發揮巨大作用。

-

芯片

+關注

關注

456文章

51170瀏覽量

427255 -

三星電子

+關注

關注

34文章

15875瀏覽量

181331 -

新思

+關注

關注

0文章

21瀏覽量

29858

發布評論請先 登錄

相關推薦

三星3nm良率僅20%,仍不放棄Exynos 2500處理器,欲打造“十核怪獸”

三星電子1c nm內存開發良率里程碑推遲

三星1c nm DRAM開發良率里程碑延期

三星重啟1b nm DRAM設計,應對良率與性能挑戰

三星芯片代工新掌門:先進與成熟制程并重

三星蘇州先進封裝廠將擴產

半導體工藝之生產力和工藝良率

三星3nm芯片良率低迷,量產前景不明

三星展望2027年:1.4nm工藝與先進供電技術登場

傳三星電子12nm級DRAM內存良率不足五成

三星電子:加快2nm和3D半導體技術發展,共享技術信息與未來展望

受困于良率?三星否認HBM芯片生產采用MR-MUF工藝

新思宣布先進工藝良率學習平臺設計取得最大突破 為三星后續先進工藝奠定基礎

新思宣布先進工藝良率學習平臺設計取得最大突破 為三星后續先進工藝奠定基礎

評論