在固定電路板尺寸的情況下,如果設(shè)計中需要更多的功能,往往需要增加PCB的軌道密度,但這可能會導(dǎo)致軌道的相互干擾增強,軌道也是如此薄,使阻抗無法降低。 。在設(shè)計高速,高密度PCB時要注意串?dāng)_干擾,因為它對時序和信號完整性有很大影響。以下是一些注意事項:

1.控制跡線特征阻抗的連續(xù)性和匹配。

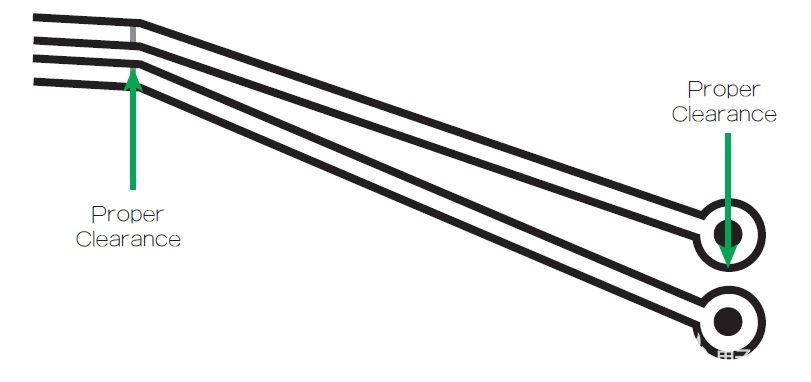

2。跟蹤空間。通常看到的間距是線寬的兩倍。仿真可用于了解走線間距對時序和信號完整性的影響,并找出可容許的最小空間。結(jié)果可能因芯片而異。選擇適當(dāng)?shù)慕K止方法。避免上下相鄰層的運行方向相同,或者甚至相互重疊,因為串?dāng)_大于同一層中相鄰線的串?dāng)_。

3.使用盲/埋通孔來增加軌道面積。然而,PCB板的制造成本將增加。在實際實現(xiàn)中實現(xiàn)完全并行性和相同長度確實很困難,但仍然嘗試這樣做。

4.可以保留差分終端和共模終端,以減輕對時序和信號完整性的影響。

-

PCB設(shè)計

+關(guān)注

關(guān)注

394文章

4698瀏覽量

86340 -

高速PCB

+關(guān)注

關(guān)注

4文章

94瀏覽量

25091 -

華強pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43177

發(fā)布評論請先 登錄

相關(guān)推薦

高速PCB設(shè)計指南的高密度(HD)電路設(shè)計

PCB設(shè)計--處理布線密度

高速高密度PCB設(shè)計的關(guān)鍵技術(shù)問題是什么?

高速高密度PCB 設(shè)計中電容器的選擇

高速高密度PCB設(shè)計的新挑戰(zhàn)概述

高速高密度PCB的RE問題

高速高密度PCB的SI問題

高速高密度PCB設(shè)計面臨著什么挑戰(zhàn)

PCB設(shè)計中管理高密度通孔的需求設(shè)計

如何看待高密度PCB設(shè)計的DFM規(guī)則

高速(>100MHz)高密度PCB設(shè)計技巧分享

高密度PCB設(shè)計中的技巧

高速高密度PCB設(shè)計的4個技巧

高速高密度PCB設(shè)計的4個技巧

評論