計數是一種最簡單基本的運算,計數器就是實現這種運算的邏輯電路,計數器在數字系統中主要是對脈沖的個數進行計數,以實現測量、計數和控制的功能,同時兼有分頻功能,計數器是由基本的計數單元和一些控制門所組成,計數單元則由一系列具有存儲信息功能的各類觸發器構成,這些觸發器有RS觸發器、T觸發器、D觸發器及JK觸發器等。計數器在數字系統中應用廣泛,如在電子計算機的控制器中對指令地址進行計數,以便順序取出下一條指令,在運算器中作乘法、除法運算時記下加法、減法次數,又如在數字儀器中對脈沖的計數等等。本文為大家介紹74ls161構成12進制計數器設計。

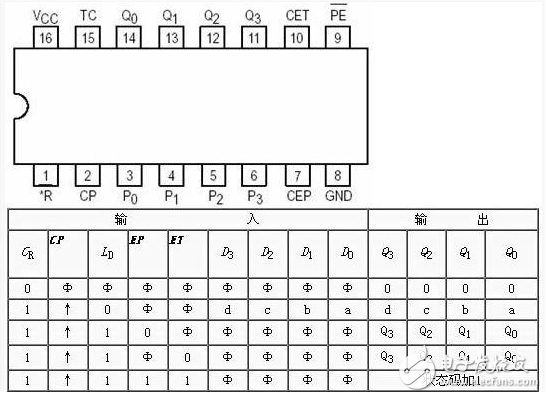

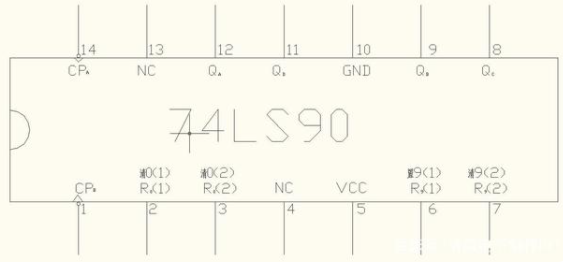

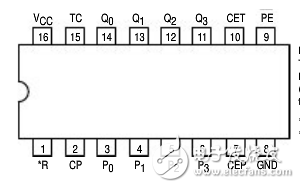

74ls161引腳圖與真值表

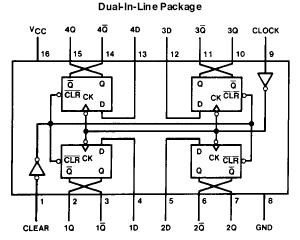

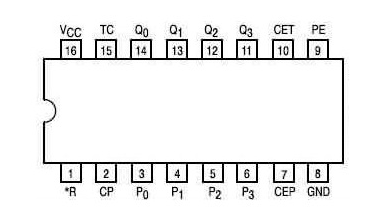

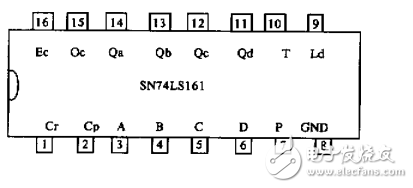

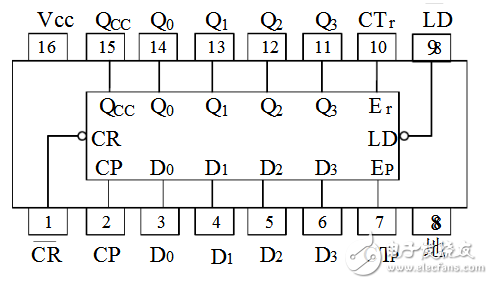

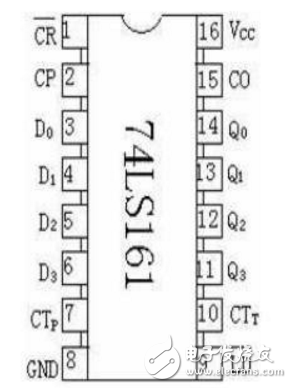

管腳圖介紹

時鐘CP和四個數據輸入端P0~P3

清零/MR

使能CEP,CET

置數PE

數據輸出端Q0~Q3

以及進位輸出TC.(TC=Q0·Q1·Q2·Q3·CET)

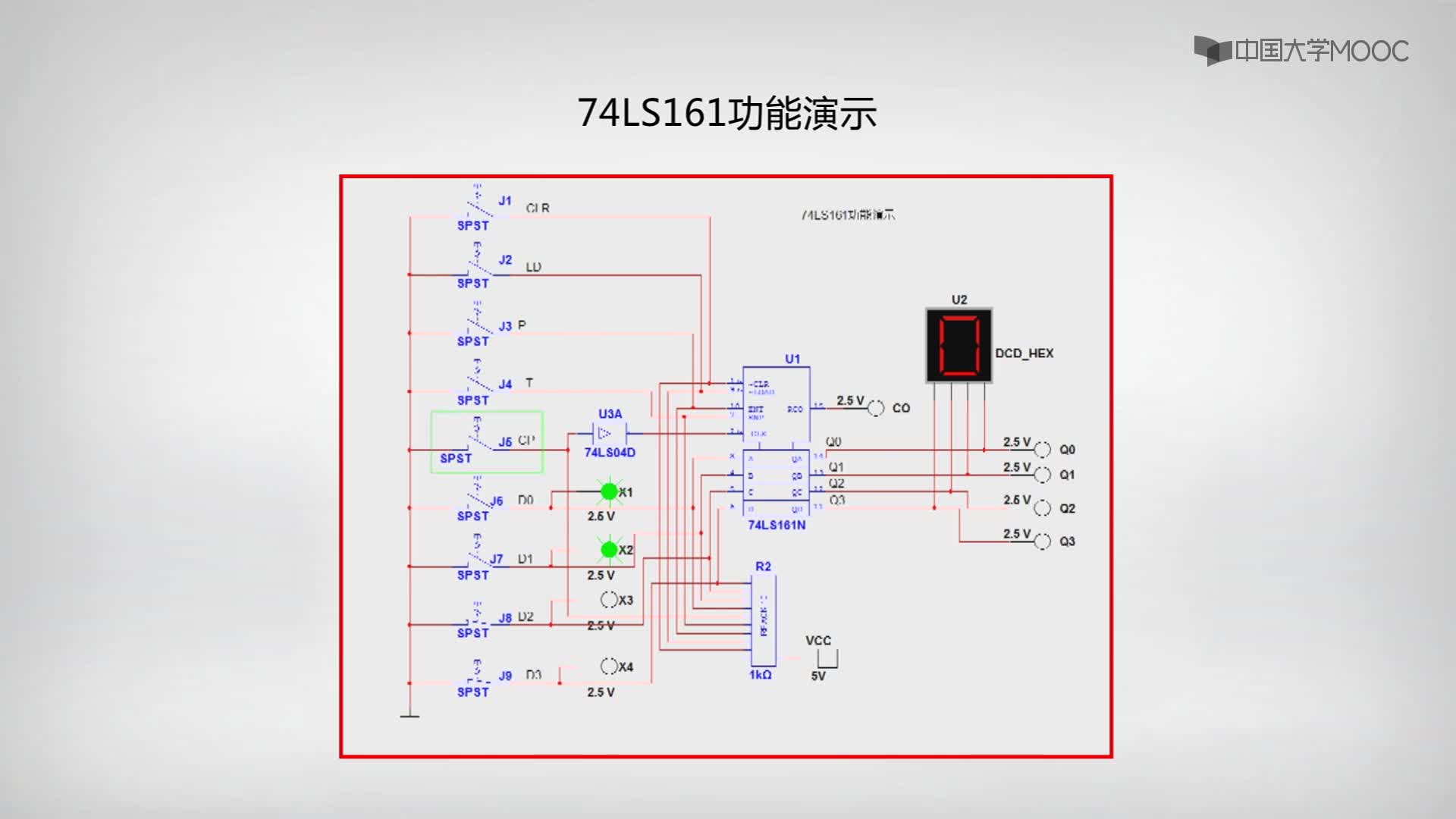

74ls161功能分析

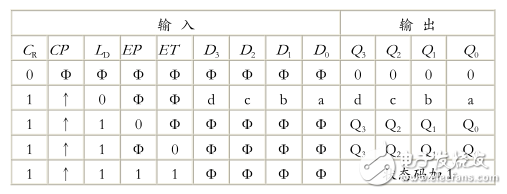

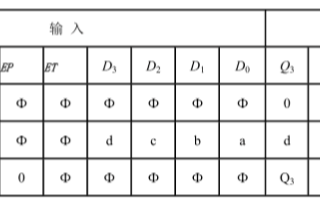

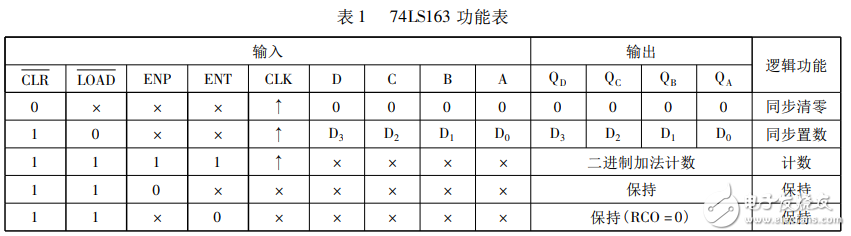

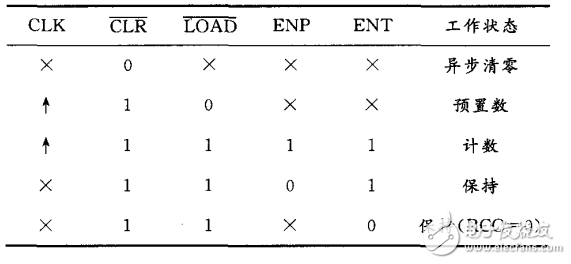

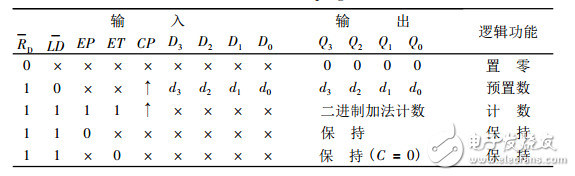

74ls161功能表

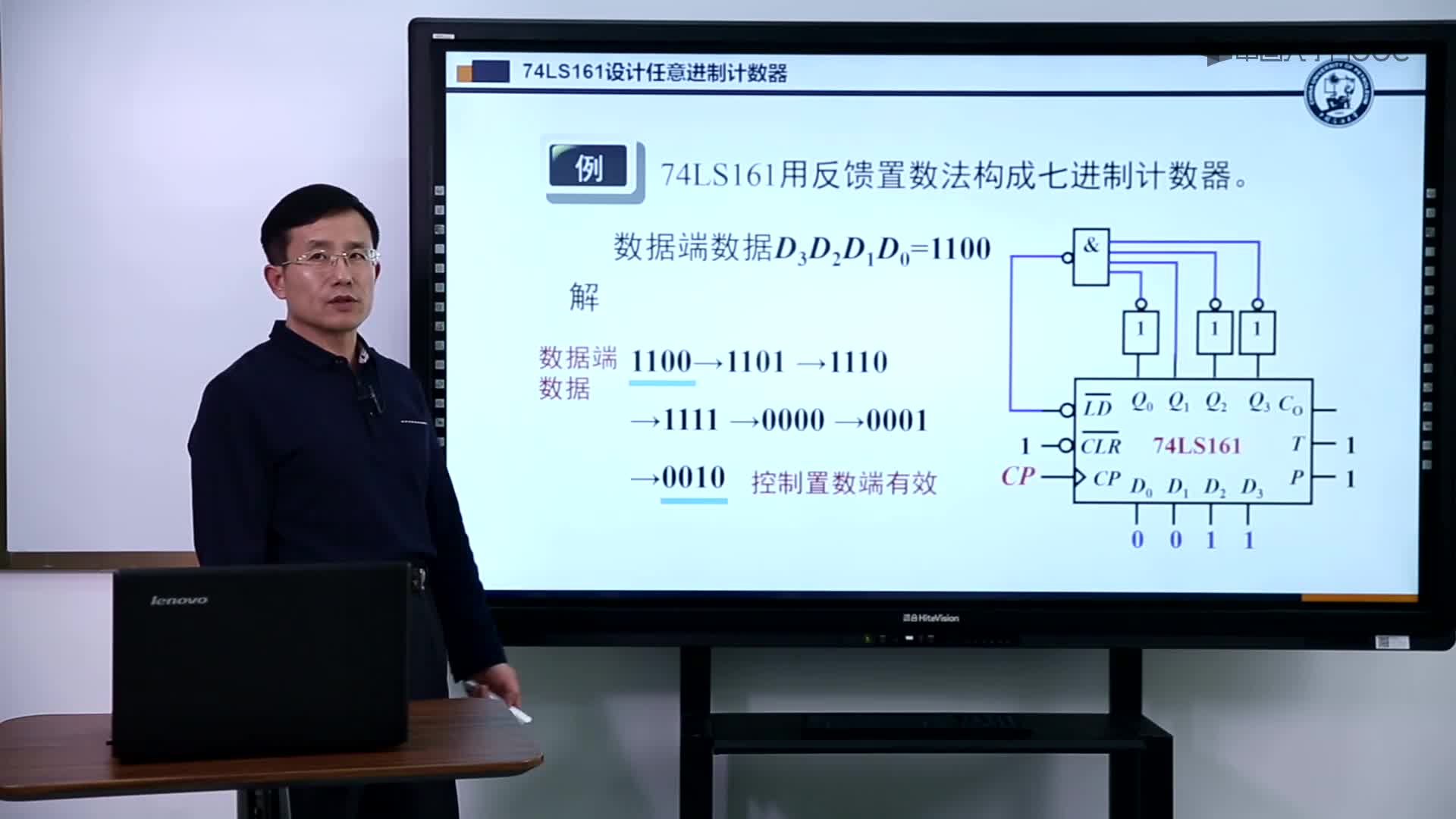

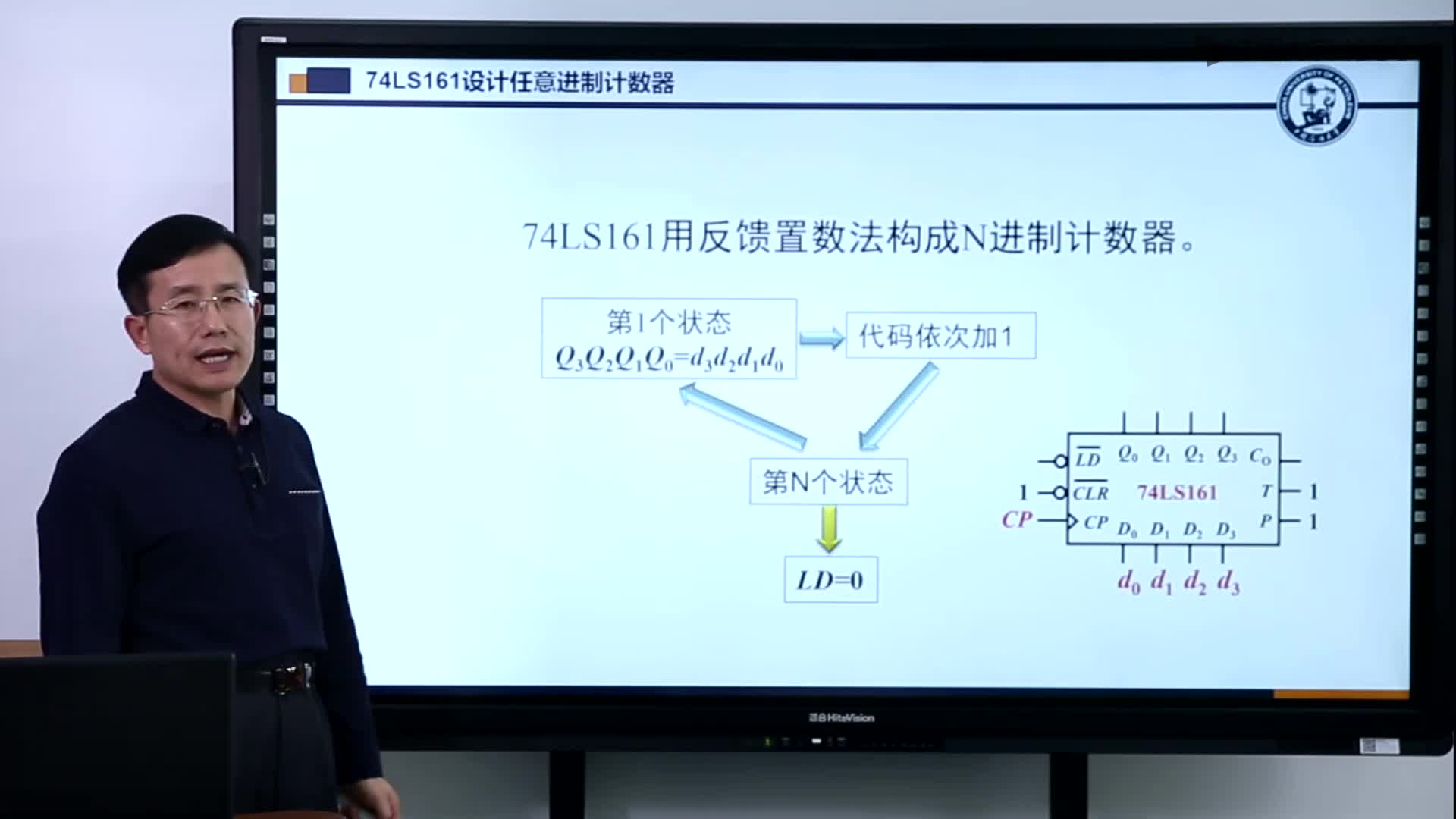

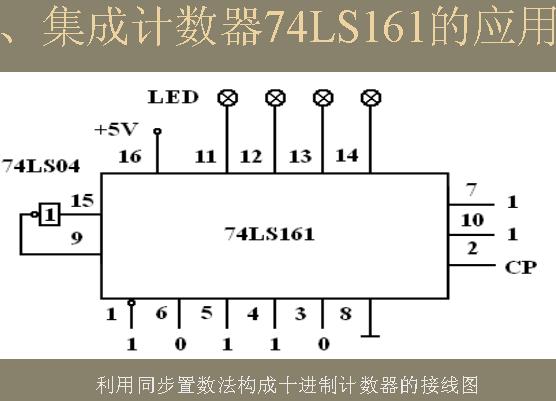

從74LS161功能表功能表中可以知道,當清零端CR=“0”,計數器輸出Q3、Q2、Q1、Q0立即為全“0”,這個時候為異步復位功能。當CR=“1”且ID=“0”時,在CP信號上升沿作用后,74LS161輸出端Q3、Q2、Q1、Q0的狀態分別與并行數據輸入端D3,D2,D1,D0的狀態一樣,為同步置數功能。而只有當CR=LD=EP=ET=“1”、CP脈沖上升沿作用后,計數器加1。74ls161還有一個進位輸出端CO,其邏輯關系是CO=Q0.Q1.Q2.Q3.CET。合理應用計數器的清零功能和置數功能,一片74LS161可以組成16進制以下的任意進制分頻器。

161的清除端是異步的。當清除端CLEAR為低電平時,不管時鐘端CLOCK狀態如何,即可完成清除功能。

161的預置是同步的。當置入控制器LOAD為低電平時,在CLOCK上升沿作用下,輸出端QA-QD與數據輸入端A-D相一致。對于54/74161,當CLOCK由低至高跳變或跳變前,如果計數控制端ENP、ENT為高電平,則LOAD應避免由低至高電平的跳變,而54/74LS161無此種限制。

161的計數是同步的靠CLOCK同時加在四個觸發器上而實現的。當ENP、ENT均為高電平時,在CLOCK上升沿作用下QA-QD同時變化,從而消除了異步計數器中出現的計數尖峰。對于54/74161,只有當CLOCk為高電平時,ENP、ENT才允許由高至低電平的跳變,而54/74LS161的ENP、ENT跳變與CLOCK 無關。

161有超前進位功能。當計數溢出時,進位輸出端(RCO) 輸出一個高電平脈沖,其寬度為QA的高電平部分。在不外加門電路的情況下,可級聯成N位同步計數器。對于54/74LS161,在CLOCk 出現前,即使ENP、ENT、CLEAR 發生變化,電路的功能也不受影響。

編輯推薦:74LS161真值表

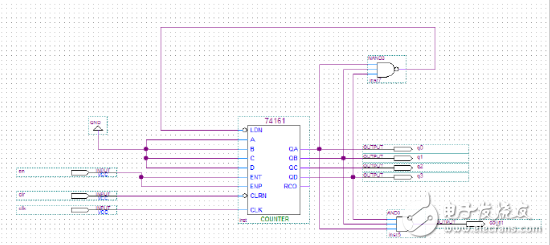

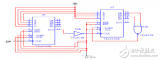

74ls161構成12進制計數器設計方案

74LS160是十進制計數器,要實現十二進制計數器必須用兩片實現級聯,把各位芯片預置1,當數碼管顯示9時,個位芯片開始進位即B端為0C端為1,經過與非門輸出高電平,十位芯片開始工作,十位芯片由0變為1,此時十位芯片A端為1個位芯片B端為0C端為0,經過與或門輸出0,十位芯片處于維持狀態,當個位芯片顯示2時,個位芯片B端為1十器位芯片A端為1,經過與非門輸出0,重新開始預置數,即完成了十二進制計數。

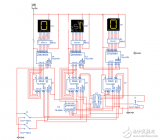

74ls161構成12進制計數器原理圖

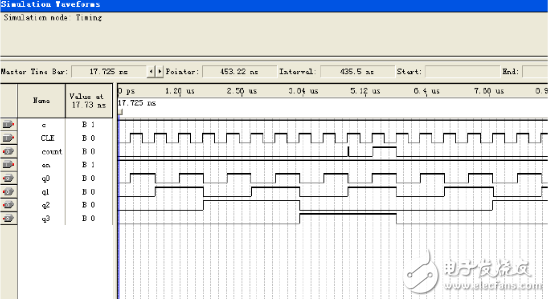

仿真波形圖

電子發燒友App

電子發燒友App

評論