低采樣速率ADC仍然采用逐次逼近(SAR)、積分型結(jié)構(gòu)以及最近推出的過采樣ΣΔADC,而高采樣速率(幾百M(fèi)SPS以上)大多用閃速ADC及其各種變型電路。然而,最近幾年各種各樣的流水線ADC已經(jīng)在速度

2023-09-26 10:24:32 82

82

流水線是為了提高效率,能并發(fā)同時(shí)進(jìn)行多個(gè)任務(wù)。

2023-09-05 15:39:56 541

541

stage:和聲明式的含義一致,定義流水線的階段。Stage 塊在腳本化流水線語法中是可選的,然而在腳本化流水線中實(shí)現(xiàn) stage 塊,可以清楚地在 Jenkins UI 界面中顯示每個(gè) stage 的任務(wù)子集。

2023-07-20 16:43:16 275

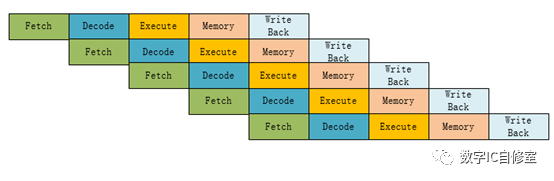

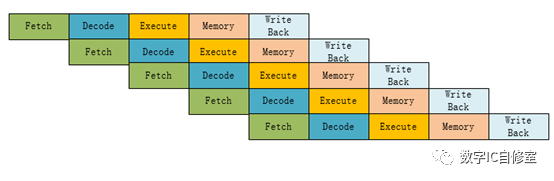

275 pipeline流水線設(shè)計(jì)是一種典型的面積換性能的設(shè)計(jì)。一方面通過對(duì)長功能路徑的合理劃分,在同一時(shí)間內(nèi)同時(shí)并行多個(gè)該功能請(qǐng)求,大大提高了某個(gè)功能的吞吐率

2023-06-27 15:26:11 384

384

請(qǐng)教一下大家 流水線型 AD 的優(yōu)缺點(diǎn),還有應(yīng)用范圍。小弟只用過SAR型的,在選型的時(shí)候看到了 流水線型的這種AD,不知道和SAR型的相比有什么特點(diǎn),有什么不足。~先謝謝大家啦

2010-06-23 10:25:51

jenkins 有 2 種流水線分為聲明式流水線與腳本化流水線,腳本化流水線是 jenkins 舊版本使用的流水線腳本,新版本 Jenkins 推薦使用聲明式流水線。文檔只介紹聲明流水線。

2023-05-17 16:57:31 333

333 流水線設(shè)計(jì)通常可以在一定程度上提升系統(tǒng)的時(shí)鐘頻率,因此常常作為時(shí)序性能優(yōu)化的一種常用技巧。如果某個(gè)原本單個(gè)時(shí)鐘周期完成的邏輯功能塊可以進(jìn)一步細(xì)分為若干個(gè)更小的步驟進(jìn)行處理,而且整個(gè)數(shù)據(jù)處理過程是單向

2023-05-08 10:55:14 364

364

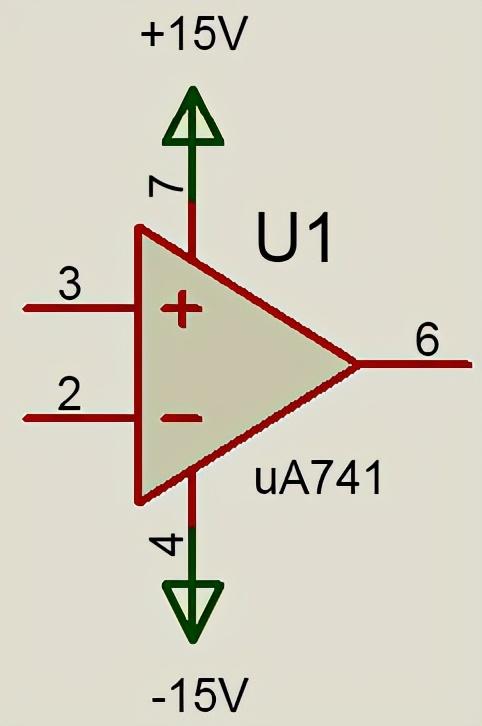

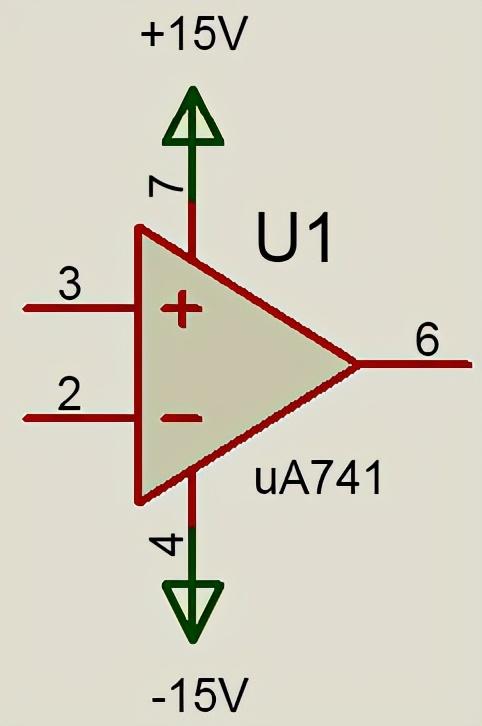

【任務(wù)】運(yùn)放是模擬電路的靈魂核心器件,為使運(yùn)放工作可靠且壽命達(dá)到設(shè)計(jì)預(yù)期,應(yīng)該對(duì)運(yùn)放采取必要的保護(hù)措施。運(yùn)放作為一種高輸入阻抗,高增益的器件,其損壞的原因主要有:電源極性接反,浪涌電壓,過壓,過載。試對(duì)uA741運(yùn)放進(jìn)行:極性保護(hù)、浪涌電壓保護(hù)、過壓保護(hù)、過載保護(hù)電路設(shè)計(jì)。

2023-03-31 15:59:31 2686

2686

流水線型ADC是采樣速率從幾Msps到100Msps+的首選架構(gòu)。設(shè)計(jì)復(fù)雜性僅隨位數(shù)線性(非指數(shù))增加,因此同時(shí)為轉(zhuǎn)換器提供高速、高分辨率和低功耗。流水線ADC在廣泛的應(yīng)用中非常有用,尤其是在數(shù)

2023-02-25 09:28:18 2100

2100

在生產(chǎn)過程中,自動(dòng)化包裝流水線設(shè)備會(huì)出現(xiàn)一些故障,自動(dòng)化設(shè)備故障修復(fù)排除的方法:

2023-02-19 10:03:41 439

439 stage:和聲明式的含義一致,定義流水線的階段。Stage 塊在腳本化流水線語法中是可選的,然而在腳本化流水線中實(shí)現(xiàn) stage 塊,可以清楚地在 Jenkins UI 界面中顯示每個(gè) stage 的任務(wù)子集。

2023-01-13 15:34:18 562

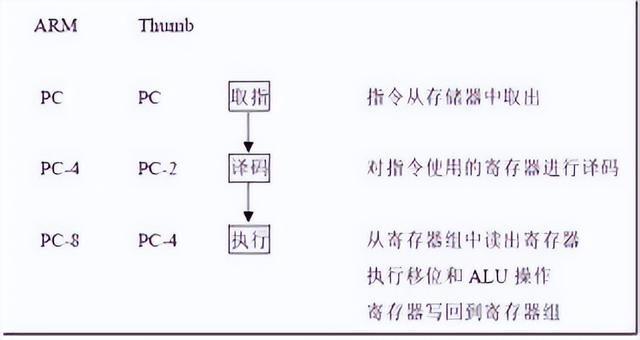

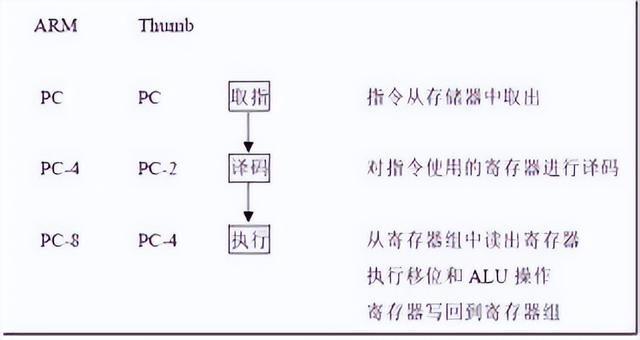

562 為什么有些CPU的主頻更低,但運(yùn)算效率卻更高呢? 比如:51單片機(jī)30M主頻,STM32單片機(jī)20M主頻,執(zhí)行相同一段代碼可能主頻更低的STM32所花的時(shí)間更短。 這里就牽涉到CPU流水線的問題,本文圍繞CPU流水線描述相關(guān)內(nèi)容。

2022-10-24 14:34:48 2329

2329 1989 年推出的 i486 處理器引入了五級(jí)流水線。這時(shí),在 CPU 中不再僅運(yùn)行一條指令,每一級(jí)流水線在同一時(shí)刻都運(yùn)行著不同的指令。這個(gè)設(shè)計(jì)使得 i486 比同頻率的 386 處理器性能提升了不止一倍。

2022-09-22 10:04:23 891

891 這是一種由運(yùn)放組成的恒流源電路。

2022-09-13 10:57:56 4971

4971 本文解釋了流水線及其對(duì) FPGA 的影響,即延遲、吞吐量、工作頻率的變化和資源利用率。

2022-05-07 16:51:10 4112

4112

Mara-pipelines 是一個(gè)輕量級(jí)的數(shù)據(jù)轉(zhuǎn)換框架,具有透明和低復(fù)雜性的特點(diǎn)。其他特點(diǎn)如下: 基于非常簡單的Python代碼就能完成流水線開發(fā)。 使用 PostgreSQL 作為數(shù)據(jù)處理引擎

2021-11-16 18:20:00 2389

2389 流水線一、定義流水線是指在程序執(zhí)行時(shí)多條指令重疊進(jìn)行操作的一種準(zhǔn)并行處理實(shí)現(xiàn)技術(shù)。各種部件同時(shí)處理是針對(duì)不同指令而言的,他們可同時(shí)為多條指令的不同部分進(jìn)行工作。? 把一個(gè)重復(fù)的過程分解為若干個(gè)子過程

2021-10-20 20:51:14 6

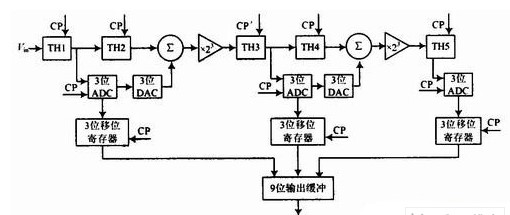

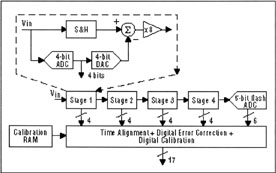

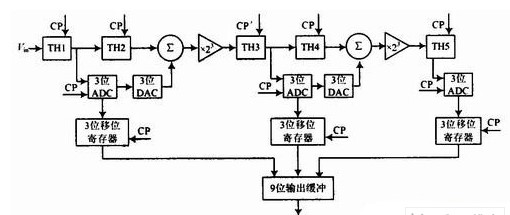

6 工藝設(shè)計(jì)了一款12位200MSPS的時(shí)間交織流水線型模數(shù)轉(zhuǎn)換器。采用時(shí)間交織、流水線、運(yùn)放共享等技術(shù),既提高了速度...

2021-09-17 11:13:44 16

16 昀通科技流水線式UVLED固化爐在工作中可以與生產(chǎn)線對(duì)接,配合流水線生產(chǎn)達(dá)到快速固化的效果。需要固化的器材在經(jīng)過UV隧道式固化爐時(shí),使其受到流水線內(nèi)UV固化光源的照射,讓器材上的膠水或油墨所含的光引發(fā)劑產(chǎn)生反應(yīng),在幾秒的時(shí)間內(nèi)完成固化。

2021-09-13 14:16:29 1120

1120 LED生產(chǎn)流水線輸送形式分為平面直線傳輸流水線、各種角度平面轉(zhuǎn)彎傳輸流水線、斜面上傳流水線、斜面下傳流水線這四種輸送方式,企業(yè)也是可以根據(jù)LED燈具生產(chǎn)狀況選擇合適自己的LED生產(chǎn)流水線輸送方式。選擇LED生產(chǎn)流水線時(shí)應(yīng)了解流水線各部分組成及功用。

2021-08-06 11:53:51 697

697 目前組裝流水線的使用范圍是非常廣泛的,特別是在電子電器行業(yè)產(chǎn)品的組裝,組裝流水線使用的評(píng)價(jià)也是高的。目前組裝流水線適用范圍:電子廠,電腦廠,食品廠,建材廠等等行業(yè)。隨著它的發(fā)展,不少的企業(yè)人員都會(huì)問

2021-08-05 18:51:25 679

679 在工程建造中,滾筒流水線演著重要的角色。在一些工程建造過程中,經(jīng)常看到滾筒流水線的身影。在工業(yè)不斷發(fā)展下的今天,滾筒流水線日益增長,走向多元化。滾筒流水線能夠長距離的輸送,而且支持重量大的貨物。

2021-07-08 09:32:56 1225

1225 按照流水線的輸送方式大體可以分為:皮帶流水裝配線、板鏈線、倍速鏈、插件線、網(wǎng)帶線、懸掛線及滾筒流水線這七類流水線。

2021-07-05 11:12:18 5492

5492

所謂流水線處理,如同生產(chǎn)裝配線一樣,將操作執(zhí)行工作量分成若干個(gè)時(shí)間上均衡的操作段,從流水線的起點(diǎn)連續(xù)地輸入,流水線的各操作段以重疊方式執(zhí)行。這使得操作執(zhí)行速度只與流水線輸入的速度有關(guān),而與處理所需

2021-05-27 16:57:52 2067

2067 送給 Reducer任務(wù),由此導(dǎo)致的大量傳輸延遲成為 Mapreduce框架性能的重要瓶頸。為此,文中提出了一種面向 Mapreduce的中間數(shù)據(jù)傳輸流水線優(yōu)化機(jī)制,將有效計(jì)算與中間數(shù)據(jù)傳輸解耦,以流水線的方式重疊執(zhí)行各個(gè)階段,有效隱藏?cái)?shù)據(jù)傳輸開銷。文中還給岀了中間數(shù)據(jù)傳輸流

2021-04-13 14:19:47 4

4 流水線設(shè)計(jì)是用于提高所設(shè)計(jì)系統(tǒng)運(yùn)行速度的一種有效的方法。為了保障數(shù)據(jù)的快速傳輸,必須使系統(tǒng)運(yùn)行在盡可能高的頻率上, 但如果某些復(fù)雜邏輯功能的完成需要較長的延時(shí),就會(huì)使系統(tǒng)很難運(yùn)行在高的頻率上, 在這

2020-09-16 17:49:46 3

3 流水線的工作方式就象工業(yè)生產(chǎn)上的裝配流水線。在CPU中由5—6個(gè)不同功能的電路單元組成一條指令處理流水線,然后將一條X86指令分成5—6步后再由這些電路單元分別執(zhí)行,這樣就能實(shí)現(xiàn)在一個(gè)CPU時(shí)鐘周期完成一條指令,因此提高CPU的運(yùn)算速度。

2019-11-29 07:06:00 2044

2044 流水線的平面設(shè)計(jì)應(yīng)當(dāng)保證零件的運(yùn)輸路線最短,生產(chǎn)工人操作方便,輔助服務(wù)部門工作便利,最有效地利用生產(chǎn)面積,并考慮流水線安裝之間的相互銜接。為滿足這些要求,在流水線平面布置時(shí)應(yīng)考慮流水線的形式、流水線安裝工作地的排列方法等問題。

2019-11-28 07:07:00 1842

1842 流水線在工業(yè)生產(chǎn)中扮演著重要的角色,優(yōu)化流水線直接關(guān)系著產(chǎn)品的質(zhì)量和生產(chǎn)的效率,因此成為企業(yè)不得不關(guān)注的話題。

2019-11-28 07:05:00 1919

1919 流水線又稱為裝配線,一種工業(yè)上的生產(chǎn)方式,指每一個(gè)生產(chǎn)單位只專注處理某一個(gè)片段的工作。以提高工作效率及產(chǎn)量;按照流水線的輸送方式大體可以分為:皮帶流水裝配線、板鏈線、倍速鏈、插件線、網(wǎng)帶線、懸掛線及滾筒流水線這七類流水線。

2019-11-28 07:04:00 3040

3040 流水線又稱為裝配線,一種工業(yè)上的生產(chǎn)方式,指每一個(gè)生產(chǎn)單位只專注處理某一個(gè)片段的工作。以提高工作效率及產(chǎn)量

2019-11-22 07:03:00 3239

3239 流水線主要是一種硬件設(shè)計(jì)的算法,如第一條中表述的流水線設(shè)計(jì)就是將組合邏輯系統(tǒng)地分割,并在各個(gè)部分(分級(jí))之間插入寄存器,并暫存中間數(shù)據(jù)的方法。

2019-11-18 07:05:00 1710

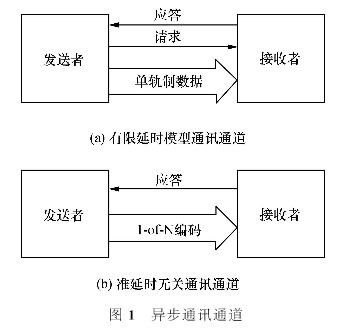

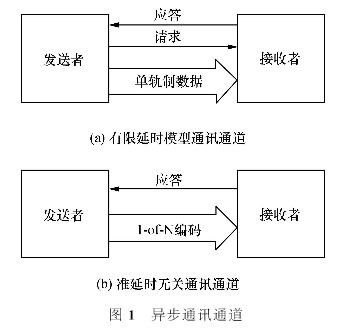

1710 異步電路因其具有低功耗、高性能和低電磁干擾的特性,正受到越來越多的關(guān)注。異步流水線是異步電路實(shí)現(xiàn)的主要形式,從而得到廣泛研究,實(shí)用的異步流水線結(jié)構(gòu)也被不斷提出,例如在文中提出的超高速異步流水線控制

2019-08-30 08:04:00 2174

2174

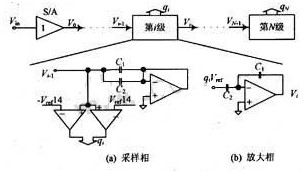

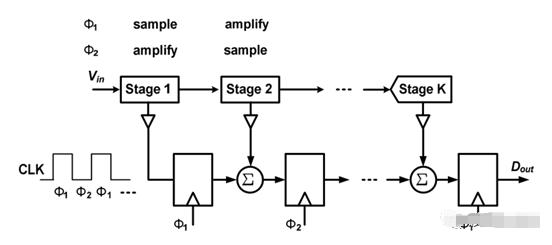

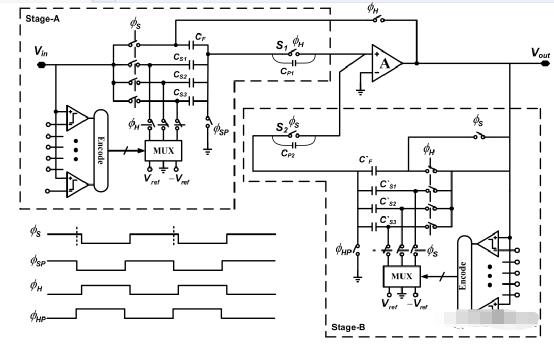

在基本A/D轉(zhuǎn)換結(jié)構(gòu)中,有些具備高速性能,有些具備高精度性能,沒有能夠同時(shí)達(dá)到高速高精度的要求。流水線ADC的出現(xiàn)在一定程度上解決了這個(gè)難題。流水線結(jié)構(gòu)可以在采樣速度和轉(zhuǎn)換精度之間取得較好的平衡。圖1是三級(jí)流水線ADC的結(jié)構(gòu)。

2019-06-08 09:39:00 2241

2241

自動(dòng)化流水線是一個(gè)統(tǒng)稱,包括組裝流水線、皮帶流水線、鏈板線、插件線等等,主要通過自動(dòng)化系統(tǒng)來操作運(yùn)行,不需要人工操作。

2019-05-22 06:06:00 6047

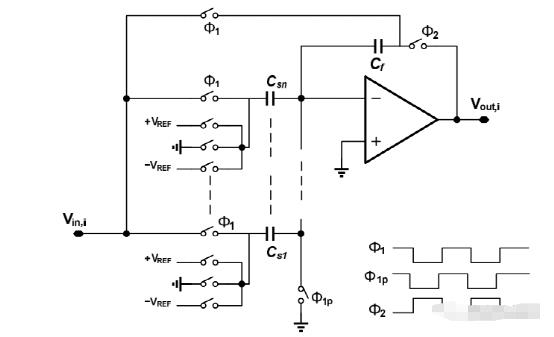

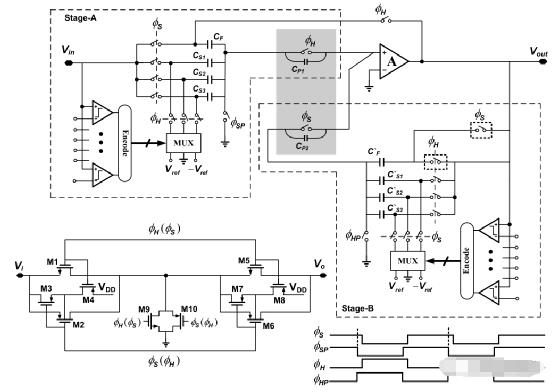

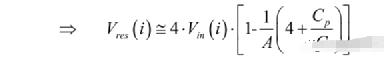

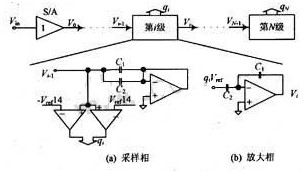

6047 雖然實(shí)際的流水線ADC應(yīng)為全差分結(jié)構(gòu),但是由于電路的對(duì)稱性,本文只對(duì)單端進(jìn)行原理分析(有源誤差平均技術(shù)除外)。如圖1所示,整個(gè)電路由1個(gè)采樣保持電路和N位相同的子級(jí)電路構(gòu)成。其每一個(gè)子級(jí)的工作原理相同:

2019-05-17 08:11:00 2964

2964

如果有數(shù)字電路常識(shí)的人都知道,利用一塊組合邏輯電路去做8位的加法,其速度肯定比做2位的加法慢。因此這里可以采用4級(jí)流水線設(shè)計(jì),每一級(jí)只做兩位的加法操作,當(dāng)流水線一啟動(dòng)后,除第一個(gè)加法運(yùn)算之外,后面每經(jīng)過一個(gè)2位加法器的延時(shí),就會(huì)得到一個(gè)結(jié)果。

2019-02-04 17:20:00 7226

7226 第一部分什么是流水線 第二部分什么時(shí)候用流水線設(shè)計(jì) 第三部分使用流水線的優(yōu)缺點(diǎn) 第四部分流水線加法器舉例 一. 什么是流水線 流水線設(shè)計(jì)就是將組合邏輯系統(tǒng)地分割,并在各個(gè)部分(分級(jí))之間插入寄存器

2018-09-25 17:12:02 4151

4151 1914年福特在高地公園引入流水線的時(shí)候,一種全新的技術(shù)方式出現(xiàn)了。盡管此前流水線也屢屢冒頭,但福特卻是將其真正轉(zhuǎn)化為一門工廠的必備技能。隨后一百多年,任工業(yè)技術(shù)如何發(fā)展,流水線巋然不動(dòng),以其強(qiáng)大的生命力,證明了它才是“鐵打營盤百年流水線”。

2018-08-27 09:20:00 1501

1501 我們正在第三級(jí)執(zhí)行第五條指令的執(zhí)行操作,對(duì)于整個(gè)數(shù)據(jù)通路來講,其它幾級(jí)都是空閑狀態(tài),那我們?yōu)榱颂岣逤PU的工作效率,就讓他提前后邊指令的其他幾級(jí)操作。這樣一來,我們的CPU就像工廠內(nèi)的流水線一樣,每

2018-07-16 09:20:07 5262

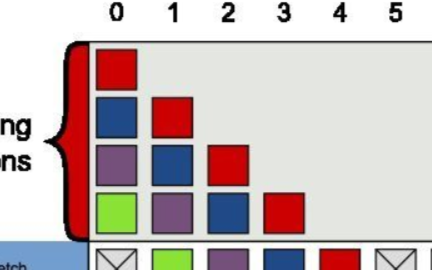

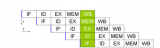

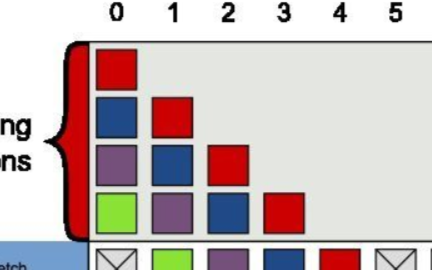

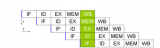

5262 顏色表示了不同階段的可配置性或可編程性:綠色表示該流水線階段是完全可編程控制的,黃色表示該流水線階段可以配置但不是可編程的,藍(lán)色表示該流水線階段是由GPU固定實(shí)現(xiàn)的,開發(fā)者沒有任何控制權(quán)。實(shí)線表示該shader必須由開發(fā)者編程實(shí)現(xiàn),虛線表示該Shader是可選的.

2018-05-04 09:16:00 3505

3505

本文將討論處理器的一個(gè)重要的基礎(chǔ)知識(shí):流水線。熟悉計(jì)算機(jī)體系結(jié)構(gòu)的讀者一定知道,言及處理器微架構(gòu),幾乎必談其流水線。處理器的流水線結(jié)構(gòu)是處理器微架構(gòu)最基本的一個(gè)要素,猶如汽車底盤對(duì)于汽車一般具有基石性的作用,它承載并決定了處理器其他微架構(gòu)的細(xì)節(jié)。

2018-04-08 08:16:00 21384

21384

設(shè)計(jì)了一種新穎的3232位高速流水線乘法器結(jié)構(gòu).該結(jié)構(gòu)所采用的新型Radix-16 Booth算法吸取了冗余Booth編碼與改進(jìn)Booth編碼的優(yōu)點(diǎn),能簡單、快速地產(chǎn)生復(fù)雜倍數(shù).設(shè)計(jì)完成的乘法器只

2018-03-15 13:34:00 6

6 1989年推出的i486處理器引入了五級(jí)流水線。這時(shí),在CPU中不再僅運(yùn)行一條指令,每一級(jí)流水線在同一時(shí)刻都運(yùn)行著不同的指令。這個(gè)設(shè)計(jì)使得i486比同頻率的386處理器性能提升了不止一倍。五級(jí)流水線

2018-01-26 01:18:48 2762

2762

了一種新的解決方法。 1 流水線結(jié)構(gòu) 流水線處理器一般把一條指令的執(zhí)行分成幾個(gè)步驟,或稱為級(jí)(stages)。每一級(jí)在一個(gè)時(shí)鐘周期內(nèi)完成,也就是說在每個(gè)時(shí)鐘周期,處理器啟動(dòng)并執(zhí)行一條指令。如果處理器的流水線有m級(jí),則同時(shí)可重疊執(zhí)

2017-10-23 10:35:35 0

0 流水線狀態(tài)機(jī)20進(jìn)制,101序列檢測(cè),8位加法器流水線的程序

2017-05-24 14:40:47 0

0 一種系統(tǒng)化流水線控制方法_章其富

2017-03-19 11:45:57 0

0 一種基于流水線DA算法的數(shù)字下變頻器_周云

2017-01-07 22:14:03 2

2 一種針對(duì)可重構(gòu)處理器流水線簡化編程的設(shè)計(jì)范式_周君宇

2017-01-07 21:39:44 0

0 基于五級(jí)流水線的HEVCDBF模塊硬件架構(gòu)設(shè)計(jì)_沈高峰

2017-01-07 21:28:58 0

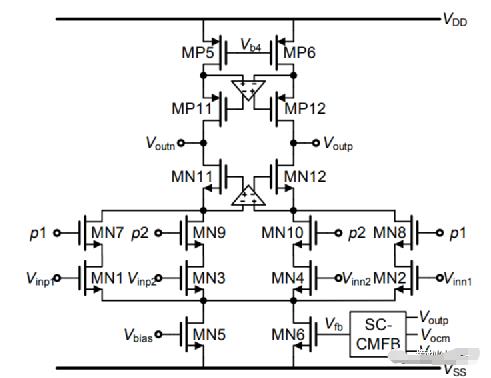

0 一種改進(jìn)運(yùn)放共享結(jié)構(gòu)的11位流水線ADC設(shè)計(jì)

2017-01-07 20:49:27 3

3 一種基于40nmCMOS工藝12位60MHz流水線模數(shù)轉(zhuǎn)換器

2017-01-07 20:32:20 3

3 三菱plc裝配流水線課程設(shè)計(jì)

2016-12-17 15:26:59 23

23 裝配流水線控制系統(tǒng)設(shè)計(jì)

2016-12-17 15:26:59 13

13 FPGA流水線個(gè)人總結(jié),感興趣的小伙伴們可以瞧一瞧。

2016-11-22 14:35:13 4

4 電鍍流水線的PLC控制電鍍流水線的PLC控制電鍍流水線的PLC控制

2016-02-17 17:13:04 34

34 行為級(jí)仿真是提高流水線(Pipeline)ADC設(shè)計(jì)效率的重要手段。建立精確的行為級(jí)模型是進(jìn)行行為級(jí)仿真的關(guān)鍵。本文采用基于電路宏模型技術(shù)的運(yùn)算放大器模型,構(gòu)建了流水線ADC的行為

2012-04-05 15:37:55 20

20 設(shè)計(jì)了一種支持IEEE754浮點(diǎn)標(biāo)準(zhǔn)的32位高速流水線結(jié)構(gòu)浮點(diǎn)乘法器。該乘法器采用新型的基4布思算法,改進(jìn)的4:2壓縮結(jié)構(gòu)和部分積求和電路,完成Carry Save形式的部分積壓縮,再由Carry Lo

2012-02-29 11:20:45 3111

3111 cpu流水線技術(shù)是一種將指令分解為多步,并讓不同指令的各步操作重疊,從而實(shí)現(xiàn)幾條指令并行處理,以加速程序運(yùn)行過程的技術(shù)。

2011-12-14 15:29:24 4346

4346 研究了一種基于 流水線結(jié)構(gòu) 的多級(jí)數(shù)字混沌保密通信方案,以驅(qū)動(dòng)參量法作為同步實(shí)現(xiàn)模型,并在編碼機(jī)制上進(jìn)行了改進(jìn)。以流水線方式對(duì)整個(gè)處理過程進(jìn)行分割,為進(jìn)程間設(shè)定合理

2011-07-25 16:16:51 32

32 為了在提高數(shù)據(jù)采集卡的速度的同時(shí)降低成本,設(shè)計(jì)了一種應(yīng)用流水線存儲(chǔ)技術(shù)的數(shù)據(jù)采集系統(tǒng)。該系統(tǒng)應(yīng)用軟件與硬件相結(jié)合的方式來控制實(shí)現(xiàn),通過MAX1308 模數(shù)轉(zhuǎn)換器完成ADC 的轉(zhuǎn)化

2011-05-12 16:29:53 36

36 介紹了補(bǔ)碼陣列乘法器的Pezaris 算法。為提高運(yùn)算速度,利用流水線技術(shù)進(jìn)行改進(jìn),設(shè)計(jì)出流水線結(jié)構(gòu)陣列乘法器,使用VHDL語言建模,在Quartus II集成開發(fā)環(huán)境下進(jìn)行仿真和功能驗(yàn)證

2010-08-02 16:38:00 12

12 流水線技術(shù)在高速數(shù)字電路設(shè)計(jì)中的應(yīng)用

2010-07-17 16:37:21 6

6 流水線中的相關(guān)培訓(xùn)教程[4]

下面討論如何利用編譯器技術(shù)來減少這種必須的暫停,然后論述如何在流水線中實(shí)現(xiàn)數(shù)據(jù)相關(guān)檢測(cè)和定向。

2010-04-13 16:09:15 4184

4184 流水線中的相關(guān)培訓(xùn)教程[3]

(1) 寫后讀相關(guān)(RAW:Read After Write) (命名規(guī)則) :j 的執(zhí)行要用到 i 的計(jì)算結(jié)果,當(dāng)它們?cè)?b style="color: red">流水線中重疊執(zhí)行時(shí),j 可

2010-04-13 16:02:57 754

754 流水線中的相關(guān)培訓(xùn)教程[1]

學(xué)習(xí)目標(biāo)

理解流水線中相關(guān)的分類及定義;

2010-04-13 15:56:08 822

822 FPGA重要設(shè)計(jì)思想及工程應(yīng)用之流水線設(shè)

流水線設(shè)計(jì)是高速電路設(shè)計(jì)中的一 個(gè)常用設(shè)計(jì)手段。如果某個(gè)設(shè)計(jì)的處理流程分為若干步驟,而且整個(gè)數(shù)據(jù)處理 流程分

2010-02-09 11:02:20 52

52 什么是流水線技術(shù)

流水線技術(shù)

2010-02-04 10:21:39 3503

3503 使用軟件仿真硬件流水線是很耗時(shí)又復(fù)雜的工作,仿真過程中由于流水線的沖突而導(dǎo)致運(yùn)行速度緩慢。本文通過對(duì)嵌入式處理器的流水線, 指令集, 設(shè)備控制器等內(nèi)部結(jié)構(gòu)的分析和

2009-12-31 11:30:21 9

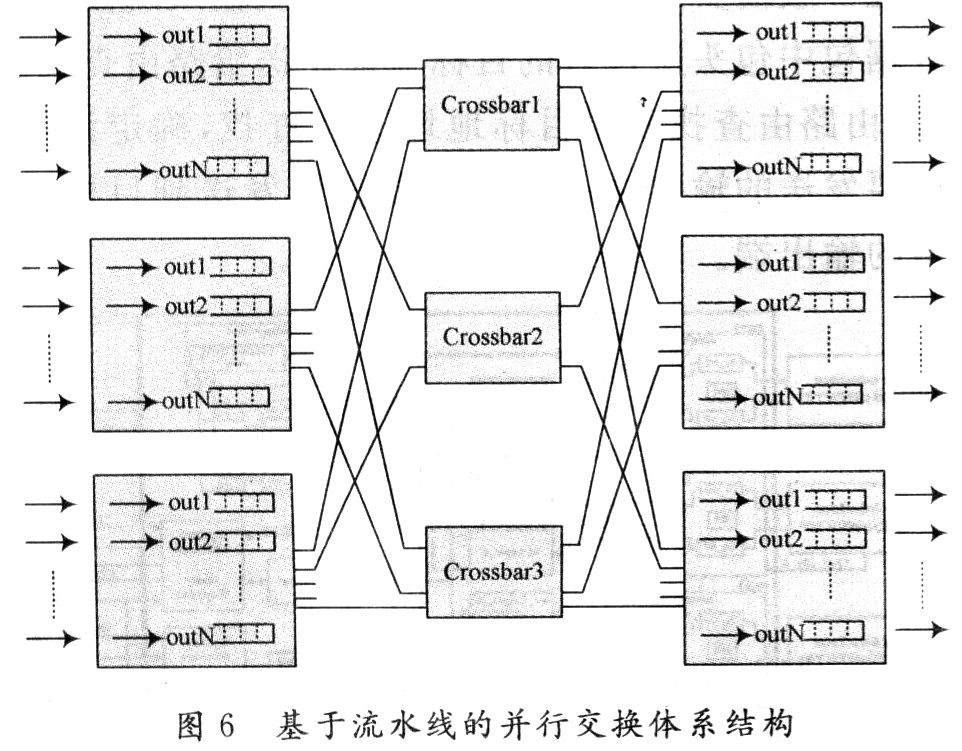

9 一種基于流水線的SpaceWire路由器研究

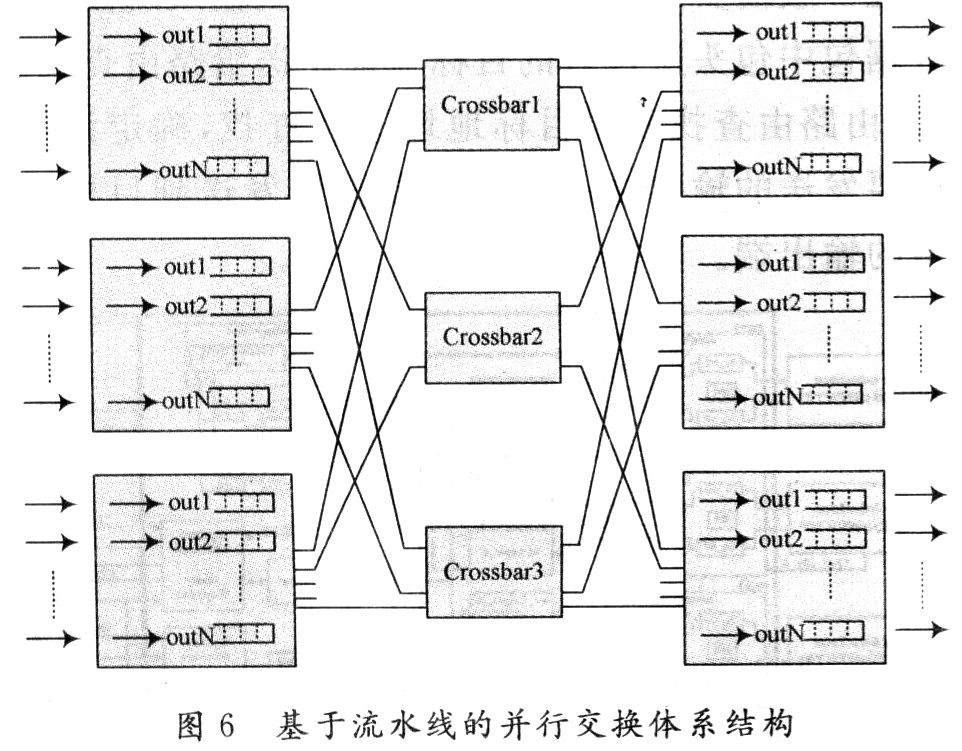

近年來,隨著SpaceWire總線技術(shù)在航天航空領(lǐng)域的不斷應(yīng)用,SpaceWire路由器在理論和技術(shù)應(yīng)用方面也得到了飛速發(fā)展。國外,歐洲航天局 (

2009-11-07 10:03:32 1096

1096

流水線ADC

低采樣速率ADC仍然采用逐次逼近(SAR)、積分型結(jié)構(gòu)以及最近推出的過采樣ΣΔADC,而高采樣速率(幾百M(fèi)SPS以上)大多用閃速ADC及其各種變型電路。然而

2009-02-08 11:02:50 6282

6282

提出了一種開關(guān)電容流水線結(jié)構(gòu)A/D轉(zhuǎn)換器(ADC)的速度分析方法。流水線結(jié)構(gòu)ADC的速度取決于其級(jí)電路中開關(guān)電容反饋放大器的建立速度。根據(jù)流水線結(jié)構(gòu)的特點(diǎn),推導(dǎo)出輸入等效階

2008-12-03 13:02:29 30

30

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論