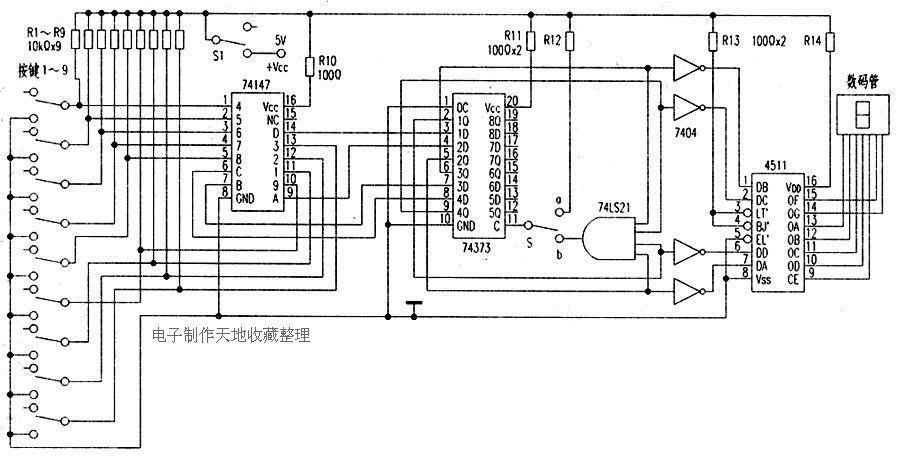

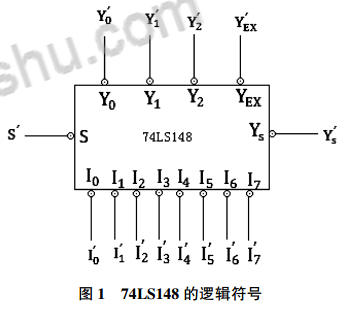

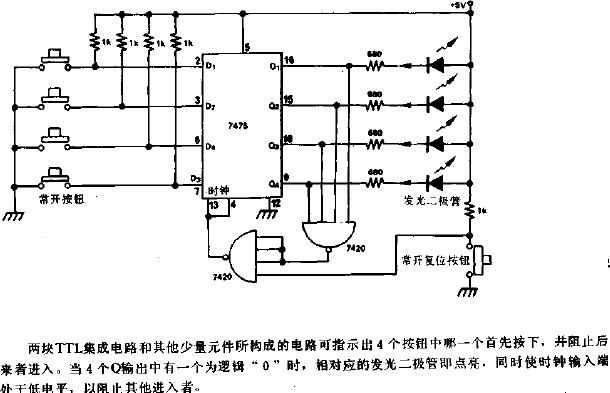

74ls148應用電路圖(一)

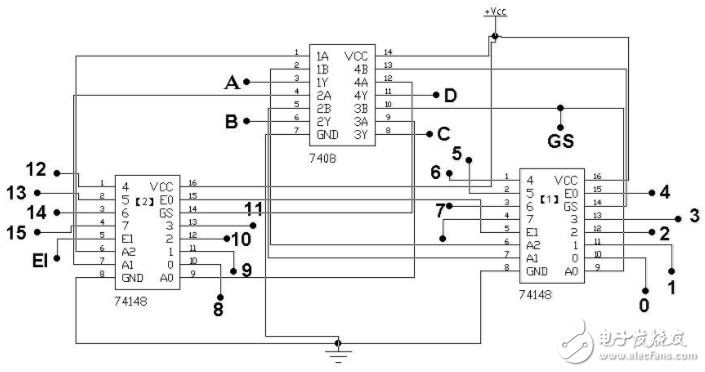

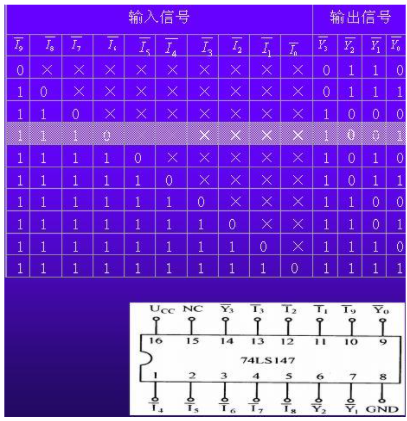

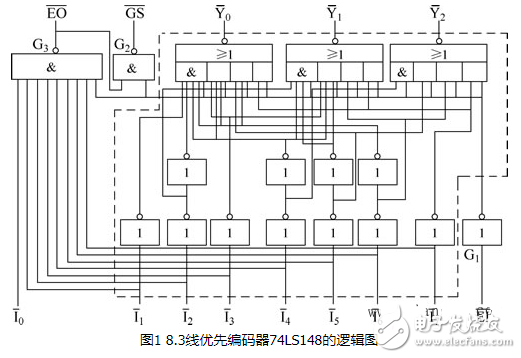

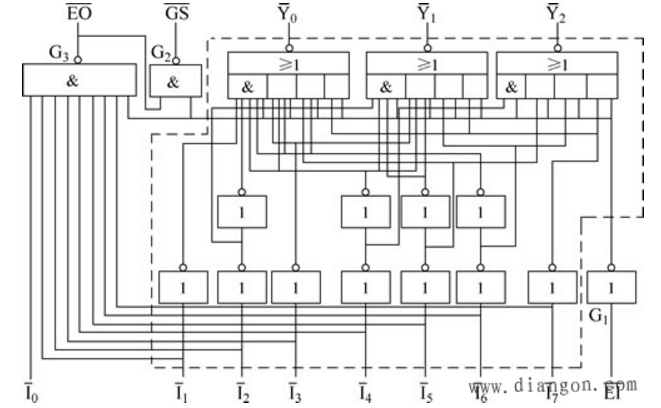

用74LS148和邏輯門電路實現16:4線優先編碼器。

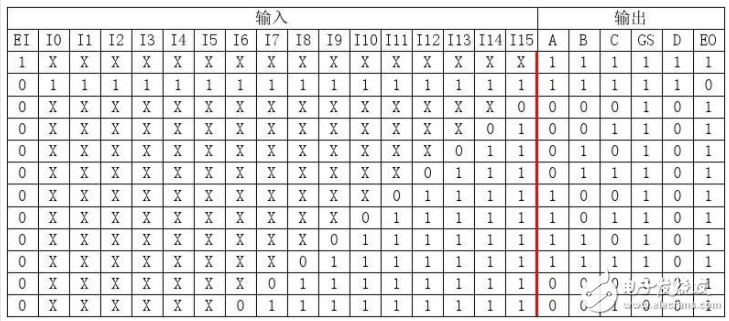

邏輯功能:按優先順序從級別最高的輸入信號編碼,當多個輸入同時有效時,只對其中優先級別最高的輸入信號編碼,而對級別較低的輸入信號不予理睬。

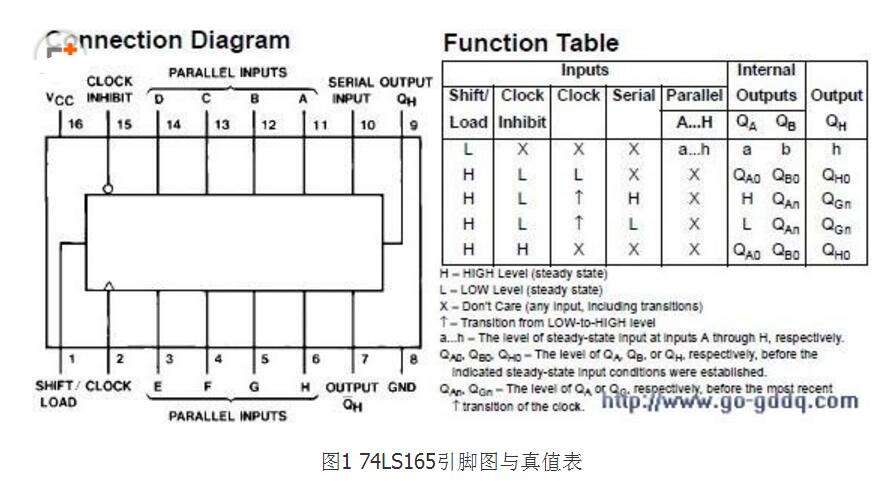

根據邏輯功能寫出真值表

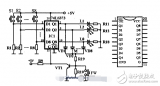

電路圖

連接電路,測試邏輯電路輸出數據,并記錄結果 根據實際操作情況,實測值與理論值一致。

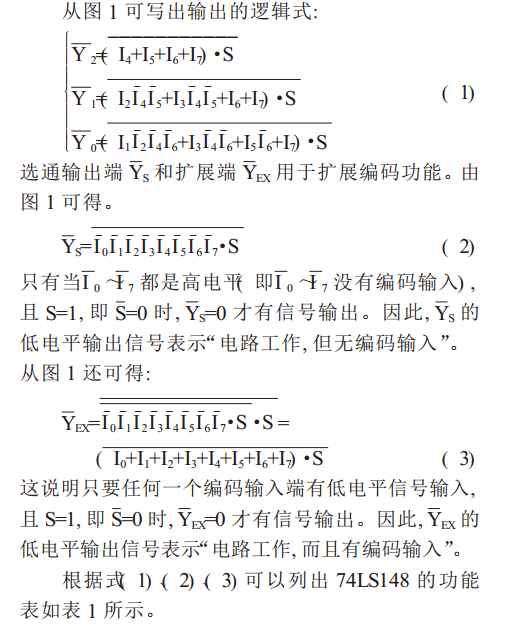

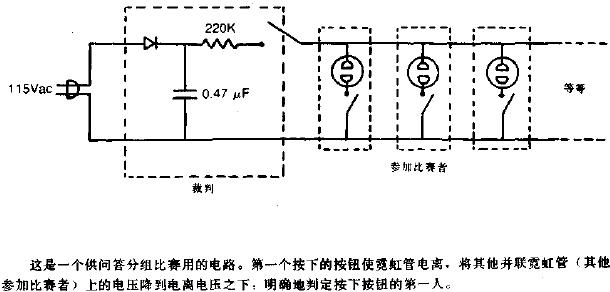

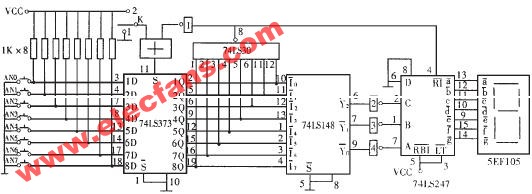

74ls148應用電路圖(二)

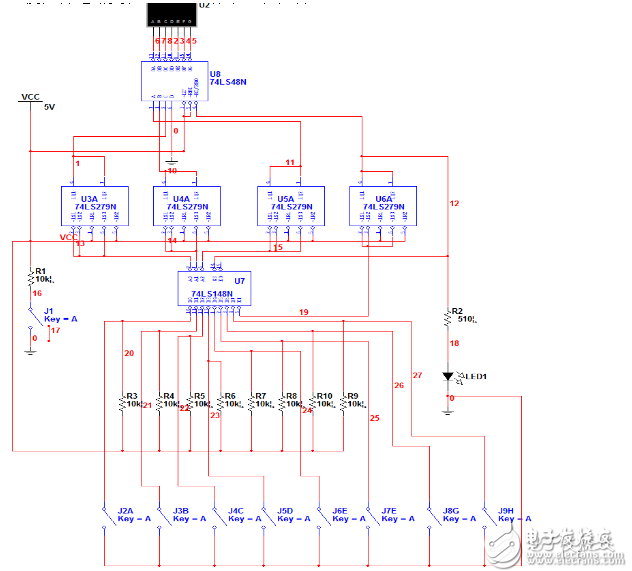

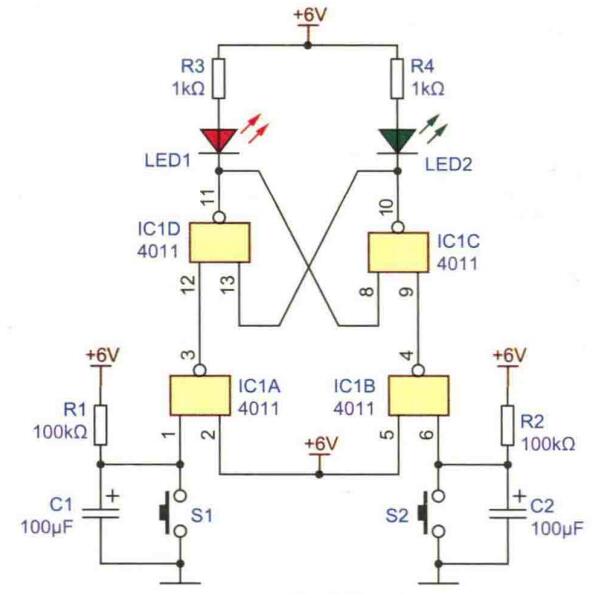

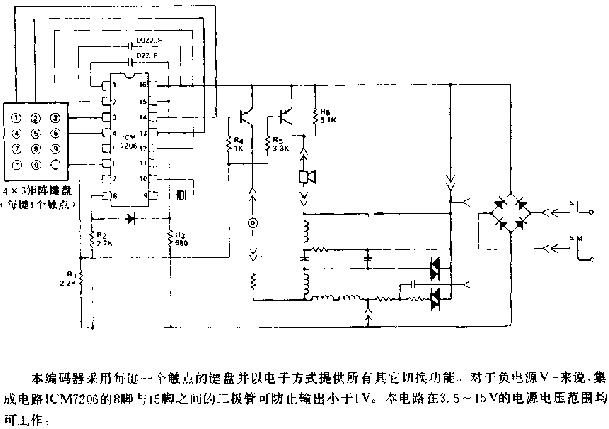

搶答電路的設計

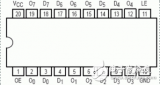

搶答電路的功能有兩個:一是能分辨出選手按鍵的的先后,并鎖存優先搶答者的編號,供譯碼顯示電路用;二是要使其他選手的按鍵操作無效。選用優先編碼74LS148和RS鎖存器74LS279可以完成上述功能。其電路組成如圖3-1所示。

其工作原理是:當主持人控制開關處于“清零”位置時,RS觸發器的R端為低電平,輸出端(4Q~1Q)全部為低電平。于是74LS48的BI=0,顯示器滅燈;74LS148的選通輸入端ST=0,74LS148處于工作狀態,此時鎖存電路不工作。當主持人將開關撥到“開始”位置時,優先編碼電路和鎖存電路同時處于工作狀態,既搶答器處于等待工作狀態,等待輸入端I7、I6、I5、I4、I3、I2、I1、I0輸入信號,當有選手將鍵按下時(如按下S5),74LS148的輸出Y2Y1Y0=010,YEX=0

經RS鎖存器后,CTR=1,BI=1,此時74LS279處于工作狀態,4Q3Q2Q=101,經74LS48譯碼后,顯示器顯示出“5”。此外,CTR=1,使74LS148的ST端為高電平,74LS148處于禁止工作狀態,封鎖了其它按鍵的輸入。當按下的鍵松開后,74LS148的YEX高電平,但由于CTR維持高電平不變,所以74LS148仍處于禁止工作狀態,其它按鍵的輸入信號仍不會被接受。這就保證了搶答者的優先性以及搶答電路的準確性。當優先搶答者回答完問題后,主持人操作控制開關S,使搶答電路復位,以便進行下一輪搶答。

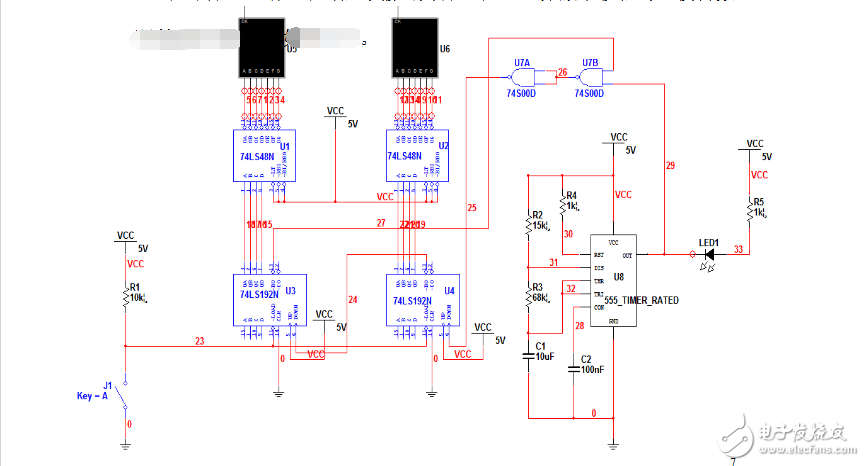

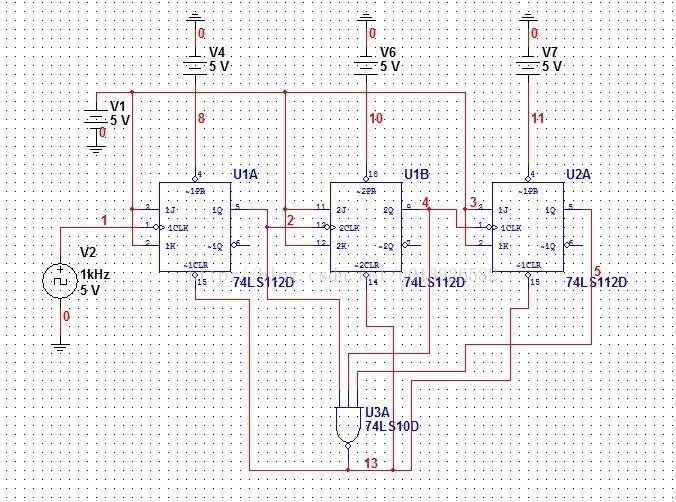

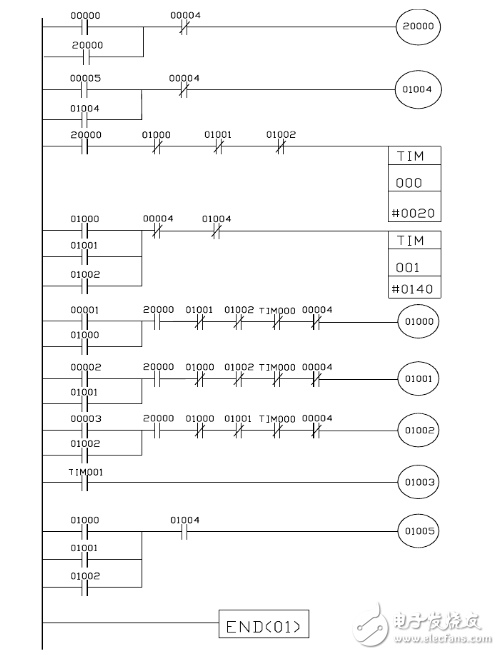

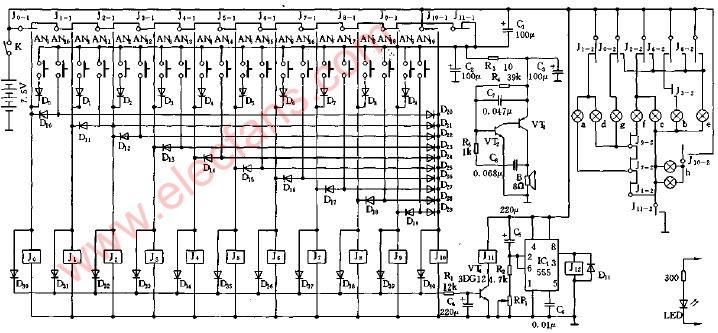

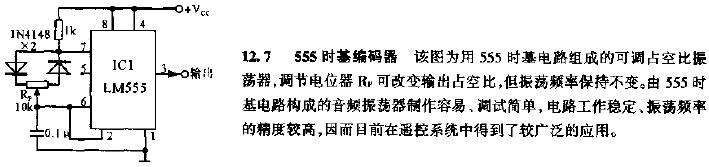

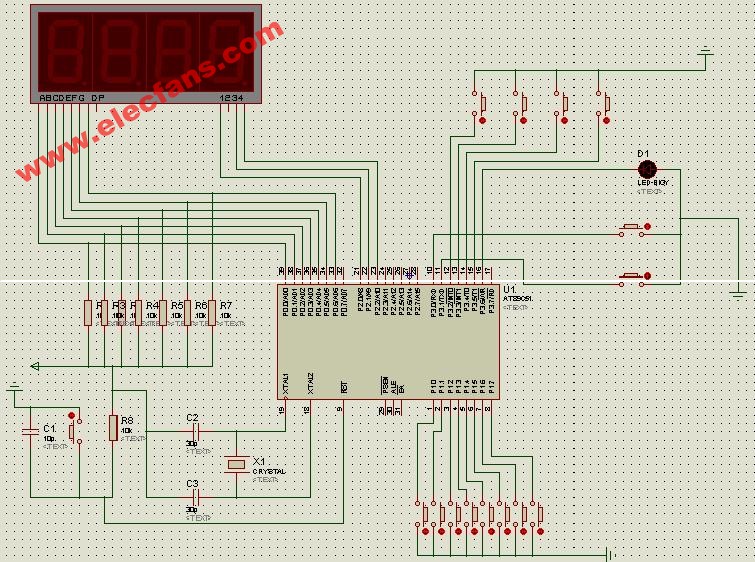

定時電路的設計

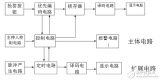

74LS48的7,6,2,3引腳接受來自74LS192的輸出信號并把它譯碼 顯示在數碼管上。74LS192的9,10,11,15引腳完成時間設定功能,本設計要求定時30秒,所以把左邊的芯片的1,15引腳接高電位,期于的全接低位,使的初始時間設定為30秒。555芯片完成產生秒脈沖的功能。工作過程為:搶答開始前,74LS192的置數端為低電位,處于初始狀態,數碼管顯示為30,5引腳接高電位。搶答開始后,秒脈沖沖推動右邊的芯片開始倒記時,同時右邊芯片產生的信號做為左邊芯片的CP信號推動左邊的芯片倒記時,完成十進制的倒記時功能。當有人搶答后1Q的輸出為1,經過非門后變為0,通過與門屏蔽了秒信號,停止記時,完成顯示搶答時間的功能。當記到了30秒時,左邊的芯片產生的定時到信號輸出為低電位,也屏蔽了秒信號,使得數碼管顯示為00。如圖3-2

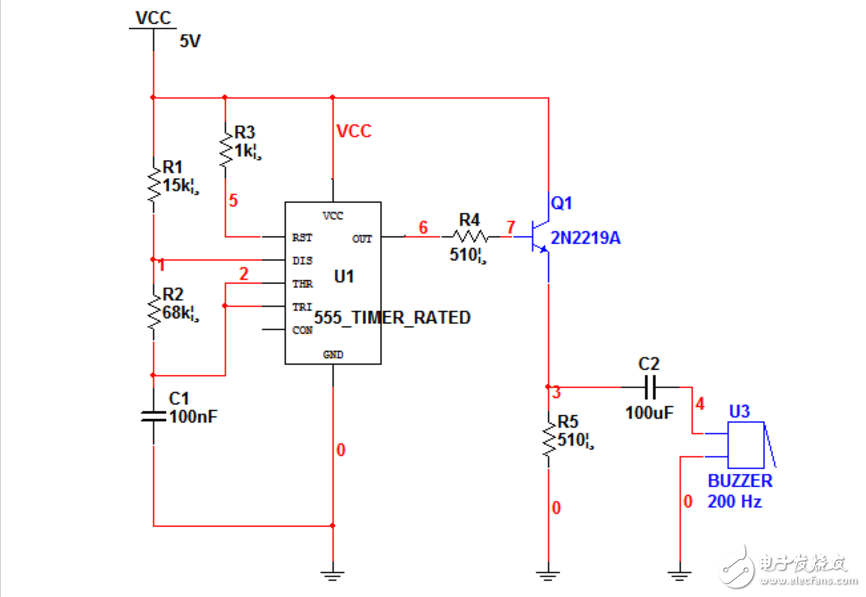

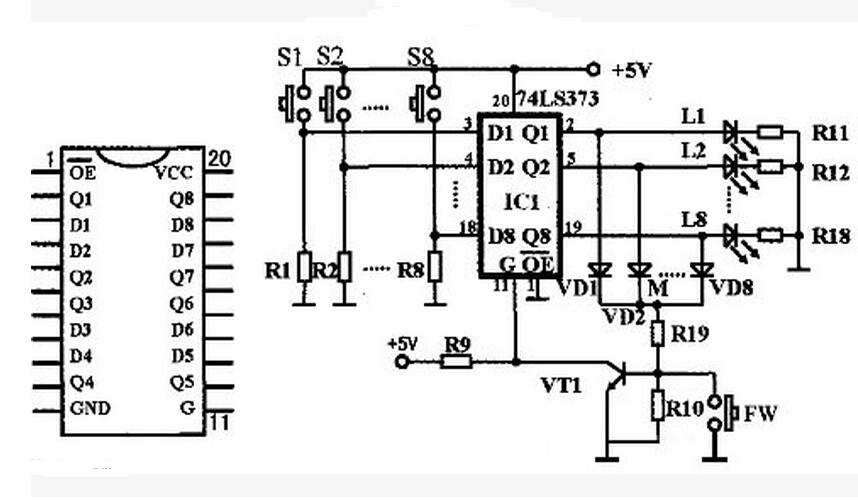

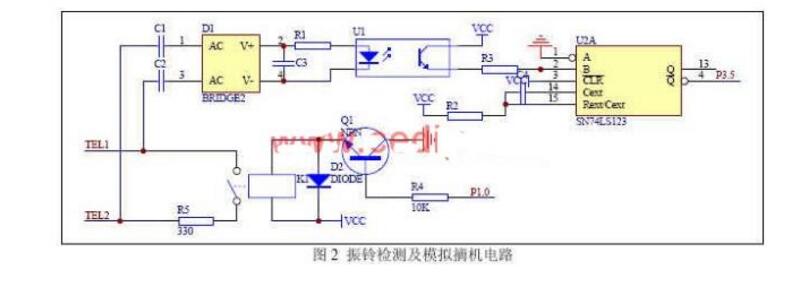

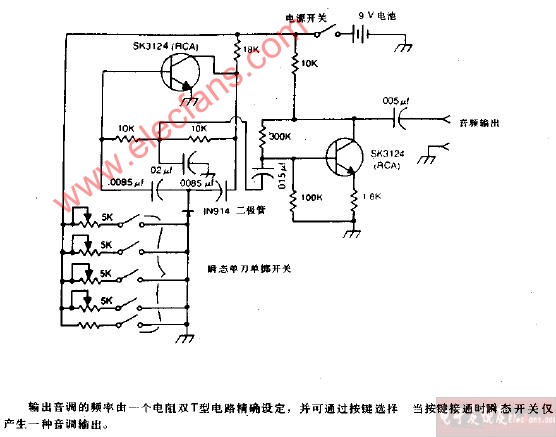

報警電路的設計

其中555構成多諧振蕩器,振蕩頻率為: f0=1/(R1+2R2)*C*ln2=1.43/(R1+2R2)*C

其輸出信號經三極管推動揚聲器。PR為控制信號,當PR為高電平時,多諧振蕩器工作,反之,電路停振不再工作。 3.4時序電路的設計時序控制電路是搶答器設計的關鍵,它要完成以下三項功能: ① 主持人將控制開關撥到“開始”位置時,揚聲器發聲,搶答電路和定時電路進入正常搶答工作狀態,

②當參賽選手按動搶答鍵時,揚聲器發聲,搶答電路和定時電路停止工作。

③當設定的搶答時間到,無人搶答時,揚聲器發聲,同時搶答電路和定時電路停止工作。

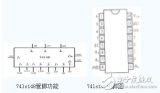

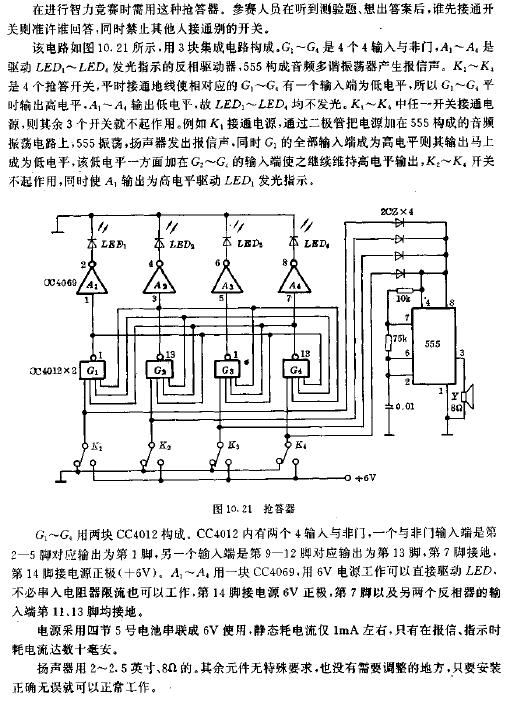

根據上面的功能要求以及圖3.1和圖3.2,設計的時序控制電路如圖3.4所示:

圖中,門G1的作用是控制時鐘信號CP的放行與禁止,門G2的作用是控制74LS148的輸入使能端ST。圖3-4(a)的工作原理是:主持人控制開關從“清零”位置撥到“開始”位置時,來自于圖3-1中的74LS279的輸出CTR=0,經G3反相,A=1,則從555輸出端來的時鐘信號CP能夠加到74LS192的CPD時鐘輸入端,定時電路進行遞減計時,在定時時間未到時,來自于圖3-2的74LS192的借位輸出端BO2=1,門G2的輸出ST=0,使74LS148處于正常工作狀態,從而實現功能①的要求;當選手在定時時間內按動搶答鍵時,CTR=1,經G3反相,A=0,封鎖CP信號,定時器處于保持狀態,門G2的輸出ST=1,74LS148處于禁止工作狀態,從而實現功能②的要求;當定時時間到時,來自于圖3-2的74LS192的借位輸出端BO2=0,門G2的輸出ST=1,74LS148處于禁止工作狀態,禁止選手進行搶答,門G1同時處于關門狀態,封鎖CP信號,使定時電路為00狀態,從而實現功能③的要求,74LS121用于控制報警電路及發聲的時間。

電子發燒友App

電子發燒友App

評論