賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。本文為您解惑......

2013-07-23 09:25:53 19707

19707

引言:本文我們介紹一下全局時鐘資源。全局時鐘是一個專用的互連網絡,專門設計用于到達FPGA中各種資源的所有時鐘輸入。

2022-07-14 09:15:35 1537

1537 “全局時鐘和第二全局時鐘資源”是FPGA同步設計的一個重要概念。合理利用該資源可以改善設計的綜合和實現效果;如果使用不當,不但會影響設計的工作頻率和穩定性等,甚至會導致設計的綜合、實現過程出錯

2023-07-24 11:07:04 655

655

FPGA 如何估算程序所需的資源?是不是要把輸出接到FPGA的PIN上后build,才算是程序所需的資源?因為我有個比較復雜的程序,沒有output到FPGA上,LUT使用為8000+一旦output到FPGA上,LUT使用為8W+.是不是此時的LUT使用量才是程序真正所需的?

2017-01-19 09:09:19

)是兩種不同的硬件實現方式。

FPGA是一種可編程邏輯器件,其內部資源可以根據需要進行配置和重新配置。這些資源包括但不限于:

邏輯單元(Logic Cells):這些是FPGA的核心計算資源,可以實現各種

2024-02-22 09:52:22

各位大神,小弟最近在做一個項目,由于之前選用的FPGA資源不夠,現在需要將程序的資源占用率降下來。經過我的冥思苦想,也找不到好的方法,不知道各位大神平時工作中降低資源利用率的方法有哪些?求助啊!!!!

2015-04-04 00:32:57

嗨,我想知道通過使用c ++代碼是否存在使用FPGA資源的骯臟,快速且非常粗糙的想法?我的任務是在FPGA上實現一個非常復雜的c ++算法。 c ++代碼非常復雜,需要幾周或幾個月才能理解,但同時

2019-03-26 06:42:03

求FPGA內部資源{:soso_e100:}相關資料,發lishenghhuc@126.com,謝謝

2012-09-27 16:55:44

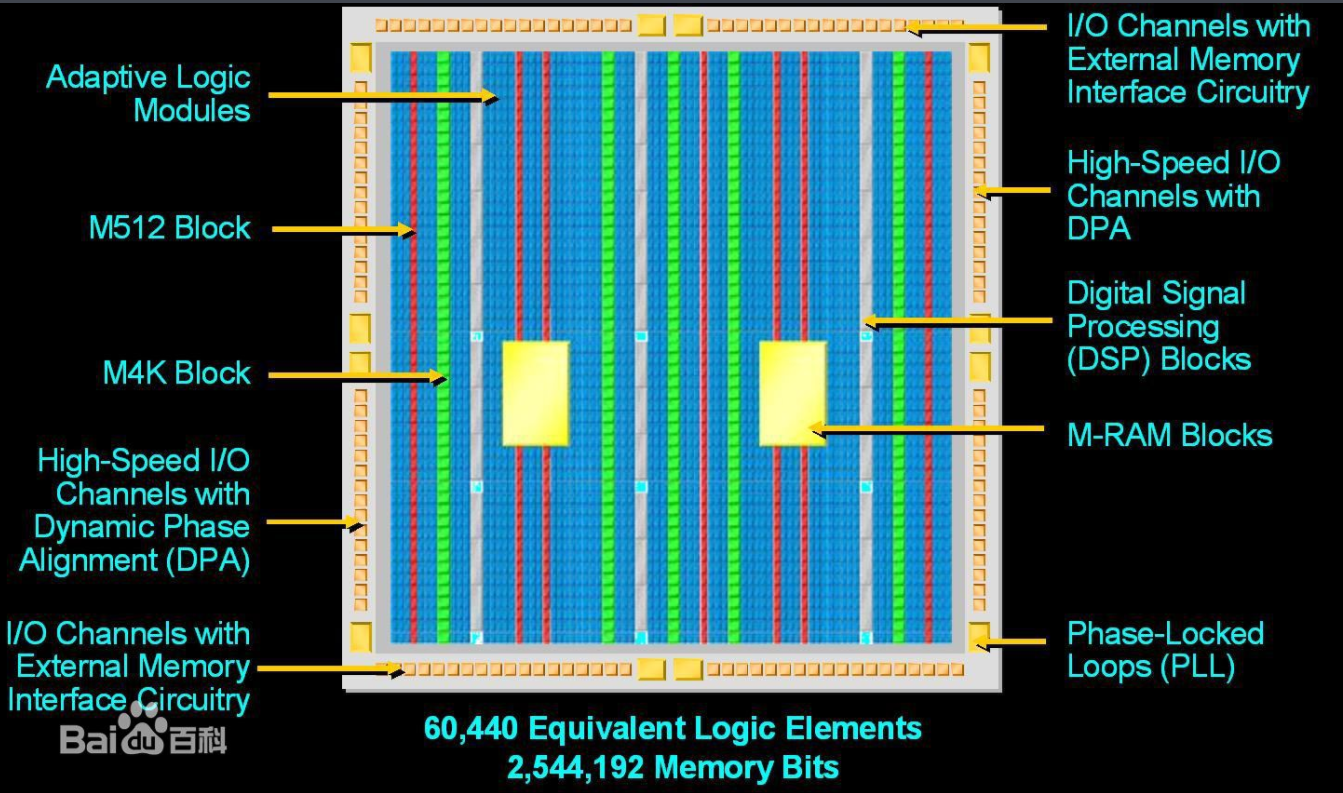

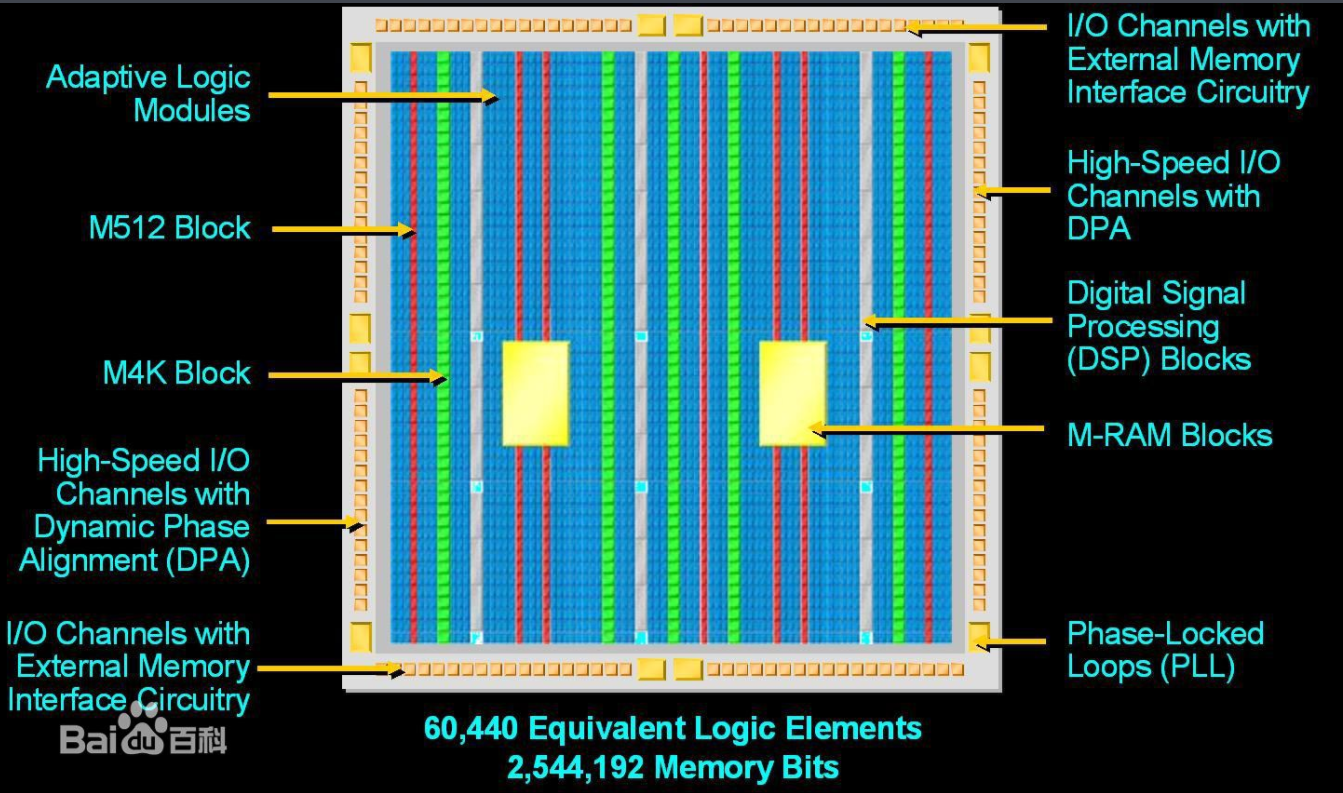

FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內嵌專用硬核等。

2019-05-24 06:15:05

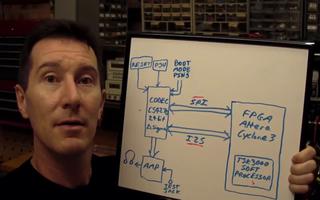

固件開發指的就是 FPGA 開發,也就是使用硬件描述語言(VHDL 或者 VerilogHDL)編寫 FPGA 內部程序。FPGA 的作用就是和 PDIUSBD12 進行通信,從 PDIUSBD12

2018-11-13 17:15:21

對FPGA學習好的資源有哪些?從入門到精通,大家可以分享一起學習呀

2024-01-28 17:00:27

的讀寫時序。 2 模塊劃分本實例工程模塊層次如圖所示。●Pll_controller.v模塊產生FPGA內部所需時鐘信號。●fifo_test.v模塊例化FPGA片內FIFO,并產生FPGA片內

2019-04-08 09:34:42

請問FPGA的資源使用如何評估?

2024-02-22 09:55:53

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2019-09-24 11:54:53

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2016-07-16 15:32:39

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2016-08-23 10:33:54

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2016-09-18 11:15:11

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2016-10-08 14:43:50

FPGA設計之模塊劃分常用架構

2019-08-14 09:42:36

模塊劃分,顧名思義是指模塊的劃分。但是,明德揚提出的模塊劃分,是廣義的“模塊劃分”。后續所提及的“模塊劃分”,不單單指模塊的劃分,還包括模塊劃分好后,模塊的端口及模塊之間數據流向的確定。

2017-05-15 16:04:29

基于SRAM的FPGA結構是怎樣構成的?FPGA連線資源的優勢有哪些?

2021-05-06 07:04:23

一個電源指示燈(紅色),一個FPGA編程完成指示燈(綠色)和一個用戶指示燈(綠色)2.2 底板硬件資源 ? PS單元l 1路千兆以太網l 1路USB Host(預留USB Device)1路TF卡接口

2018-03-23 10:11:03

NetFPGA 能夠很好地支持模塊化設計,復雜的硬件設計可以通過各個子模 塊的組合來完成.更重要的是,NetFPGA 是一個基于 Linux 的開放性平臺,所 有對它感興趣的人都可以利用平臺

2019-10-24 09:00:49

STM32的硬件系統是由哪些部分組成的?STM32的時鐘系統是由哪些部分組成的?

2021-11-23 07:17:16

,用的是HDL,偏重的是軟件;而在設計實現階段,使用的是FPGA器件的物理資源,包含了混合的I/O單元、存儲單元、寄存器、布線和特定功能的電路,這些都是偏重于硬件。在FPGA開發的各個階段中,往往要求

2019-04-10 14:58:20

最近對ibeacon非常感興趣求ibeacon的軟件和硬件開發資源的軟硬件開發資源:軟件IOS和安卓的開發資源硬件主要是原理圖之類的

2014-07-29 17:52:47

Phxhawk硬件芯片有哪些?pixhawk的硬件構架是怎樣組成的?

2021-10-15 08:50:40

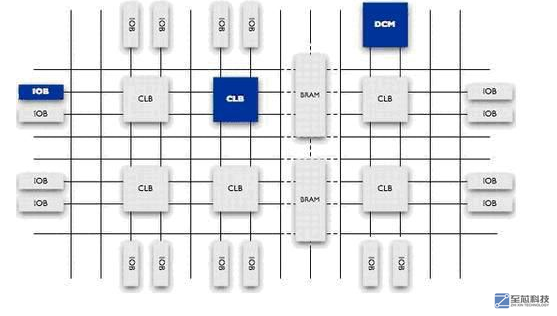

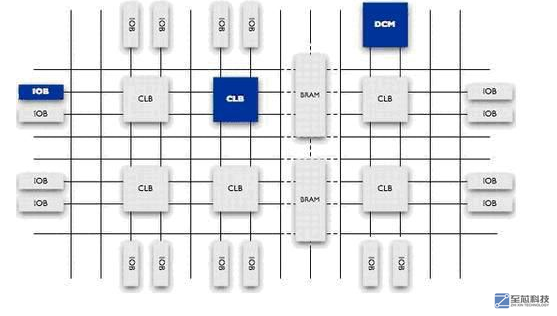

前言FPGA芯片主 要由6部分完成,分別為:可編程輸入輸出單元(IOB)基本可編程邏輯單元(configurable logic block,CLB) 完整的時鐘管理嵌入塊式RAM豐富的布線資源內嵌

2021-07-26 06:54:01

⑴ 結合Xilinx、Altera 等公司的FPGA 芯片,簡要羅列一下FPGA 內部的資源或專用模塊,并簡要說明這些資源的一些作用或用途。(至少列出5 項,越多越好)⑵ 如果,對內部特定資源,曾有

2012-03-08 11:03:49

本視頻是MiniStar FPGA開發板的配套視頻課程,本章節課程主要介紹Gowin的FPGA硬件基礎,包括FPGA的IO、IO Bank,可配置功能單元和時鐘及其他特殊資源,幫助用戶在芯片選型

2021-05-06 15:37:42

`帶你深入全面了解FPGA硬件資源PLL`

2021-03-30 14:43:12

什么是FPGA?FPGA的特點是什么?由哪些部分組成?

2021-11-03 06:17:12

把握DCM、PLL、PMCD和MMCM知識是穩健可靠的時鐘設計策略的基礎。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。

2019-09-18 08:26:21

(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。 本文主要介紹的是FPGA的片上資源使用情況,分別是從組合邏輯及時序邏輯來詳細的分析

2019-06-17 09:03:28

嵌入式最小硬件系統是由哪些部分組成的?嵌入式系統使用的存儲器是如何進行劃分的?可分為哪幾類?

2021-10-22 07:18:56

。實驗表明該系統能夠較好的支持過程級的動態軟硬件劃分,實現了節省資源、簡化設計,提高性能等目的。【關鍵詞】:可重構片上系統;;動態軟硬件劃分;;硬件透明編程模型【DOI】:CNKI:SUN

2010-05-28 13:40:38

,偏外存儲,還有硬件加速資源的共享等。

多內核之間的資源共享

多內核之間的應用劃分也意味著所有共享資源的劃分,例如片外存儲器和片上緩存等。隨著單顆裸片上內核數量的增加,片外存儲器帶寬和片上二彖緩存

2019-05-16 10:45:11

請問各位學友,站內有沒有FPGA視頻學習資源,,以及下載quartus具體指南,,,謝謝

2015-08-03 16:11:02

求大神告知目前資源最豐富的CPLD/FPGA的詳情!萬分感謝!!!

2013-03-24 17:01:22

能否組成2019年全國電賽資源共享

2019-07-21 19:37:20

RISC-V的含義是什么?計算機體系結構是由哪些部分組成的?可劃分哪幾個層次?

2021-06-18 08:38:28

概述EasyGo FPGA Solver是EasyGo開發的專門部署在FPGA 硬件上的解算器軟件。根據不同的應用需求,會有不同的FPGA Solver 選擇

2022-05-19 09:21:43

介紹了頻域抽取基二快速傅里葉運算的基本原理;討論了基于FPGA達4 096點的大點數超高速FFT硬件系統設計與實現方法,當多組大點數進行FFT運算時,利用FPGA內部大容量存儲資源,采

2009-04-26 18:33:08 26

26 根據電力監控系統的要求,提出一種基于FPGA技術的多路交流信號采集與處理系統的設計方法。分析整個系統的結構,并討論FPGA內部硬件資源的劃分和軟件的設計方案,以及各個功能

2009-05-16 14:47:58 27

27 提出用FPGA 來實現指紋識別算法, 代替了PC 機、通用MCU 或者DSP。算法由硬件來實現, 提高了運算速度。同時具體說明了指紋識別系統的基本原理、系統總體結構、FPGA 模塊劃分, 以及指

2009-07-22 15:17:27 0

0 軟硬件劃分技術是軟硬件協同設計中的一個關鍵技術。提出將時間Petri 網應用到軟硬件劃分當中,為系統的性能評估提供了形式化的方法和工具。另一方面,將系統功能集中到Petri

2009-08-15 14:34:35 11

11 基于EDA 的嵌入式系統軟硬件劃分方法Hardware/Software Partitioning Method Based on Estimation of Distribution

摘要:針對嵌入式系統軟硬件協同設計中的軟硬件劃分問題,提

2009-12-05 16:34:56 26

26 摘要:提出一種基于FPGA技術的多路模擬量、數字量采集與處理系統的設計方案,分析整個系統的結構,并討論FPGA內部硬件資源的劃分和軟件的設計方案等。本設計

2009-06-20 15:05:11 1543

1543 基于FPGA的嵌入式Linux軟硬件設計

引言

FPGA是通過邏輯組合電路來實現各種功能的器件。由于FPGA內部集成了大量的邏輯資源和可配置的I/O引腳,加上獨特的

2010-03-10 10:20:04 793

793

提出了二維模糊CMAC網絡的一種基于FPGA的硬件實現方法。首先,分析了模糊CMAC網絡的結構與算法,并以Matlab仿真為依據,得到模糊CMAC網絡的FPGA實現所需的參數;在此基礎上,對模糊CMAC網絡進行硬件模塊劃分,基于VHDL實現了各硬件模塊的功能描述,并對模塊

2011-03-15 17:19:56 29

29 提出了先進行前一級4點蝶形運算,再進行本級與旋轉因子復乘運算的結構,合理地利用了硬件資源。對系統劃分的各個模塊使用Verilog HDL進行編碼設計。對整個系統整合后的代碼進行功能

2012-02-09 16:42:09 86

86 本文簡要的分析FPGA芯片中豐富的布線資源 。FPGA芯片內部有著豐富的布線資源,根據工藝、長度、寬度和分布位置的不同而劃分為4類不同的類別。

2012-12-17 17:28:41 3491

3491 電子專業單片機相關知識學習教材資料——FPGA片內資源設計指導

2016-08-23 15:55:35 0

0 如何正確使用FPGA的時鐘資源

2017-01-18 20:39:13 22

22 現代硬件設計規模逐漸增大,單個程序功能越來越復雜,當把多個功能復雜的程序集成到一個FPGA 上實現時,由于各個程序的數據通路及所占用的資源可能沖突,使得FPGA 控制模塊的結構臃腫,影響了整個系統

2017-10-12 17:57:08 15

15 布線資源連通FPGA內部的所有單元,而連線的長度和工藝決定著信號在連線上的驅動能力和傳輸速度。FPGA芯片內部有著豐富的布線資源,根據工藝、長度、寬度和分布位置的不同而劃分為4類不同的類別。第一類

2017-12-05 11:48:44 8

8 這一次給大家分享的內容主要涉及Xilinx FPGA內的CLBs,SelectIO和Clocking資源,適合對FPGA設計有時序要求,卻還沒有足夠了解的朋友。

2018-03-21 14:48:00 4672

4672

模塊劃分,顧名思義是指模塊的劃分。但是,明德揚至簡設計法提出的模塊劃分,是廣義的“模塊劃分”。后續所提及的“模塊劃分”,不單單指模塊的劃分,還包括模塊劃分好后,模塊的端口及模塊之間數據流向的確定。

2018-04-20 02:44:00 4884

4884

(ASIC型)模塊。如圖所示,FPGA芯片主要由7部分組成,分別為:可編程輸入輸出單元(IOB)、基本可編程邏輯單元(CLB)、完整的時鐘管理(DCM)、嵌入式塊RAM、豐富的布線資源、內嵌的底層功能單元和內嵌專用硬件模塊。 1.可編程輸入輸出單元(IOB) 可編程

2018-05-25 14:11:47 8558

8558

近年來,FPGA技術發展迅速,片內集成了PLL、硬件乘法器、存儲器,具有了實現優秀算法的充足資源。許多航空電子嵌入式圖像處理系統是由固定的視頻源和顯示設備組成,系統中圖像縮放的倍率是固定的。文中針對此展開重點研究,基于FPGA硬件,實現固定倍率的圖像縮放。

2018-08-18 09:36:50 4184

4184 了解如何描述Spartan-6 FPGA中可用的基本片和I / O資源。

2019-01-04 10:32:00 3056

3056 本視頻介紹了7系列FPGA中可用的專用硬件資源。

所描述的功能包括專用的串行千兆位收發器,PCI Express內核和XADC資源。

2018-11-28 06:27:00 4345

4345 Xilinx FPGA有三種可以用來做片上存儲(RAM,ROM等等)的資源,第一個就是Flip Flop;第二種就是SLICEM里面LUT;第三種就是Block RAMs資源。

2018-12-16 11:31:21 12304

12304

在使用FPGA過程中,通常需要對資源做出評估,下面簡單談談如何評估FPGA的資源。

2019-02-15 15:09:05 3580

3580 FPGA由邏輯單元、RAM、乘法器等硬件資源組成,通過將這些硬件資源合理組織,可實現乘法器、寄存器、地址發生器等硬件電路。

2019-12-27 07:05:00 1613

1613

FPGA由邏輯單元、RAM、乘法器等硬件資源組成,通過將這些硬件資源合理組織,可實現乘法器、寄存器、地址發生器等硬件電路。

2019-11-26 07:00:00 839

839 FPGA由邏輯單元、RAM、乘法器等硬件資源組成,通過將這些硬件資源合理組織,可實現乘法器、寄存器、地址發生器等硬件電路。

2019-11-25 07:11:00 755

755 管腳是FPGA重要的資源之一,FPGA的管腳分別包括,電源管腳,普通I/O,配置管腳,時鐘專用輸入管腳GCLK等。

2019-06-28 14:34:07 3702

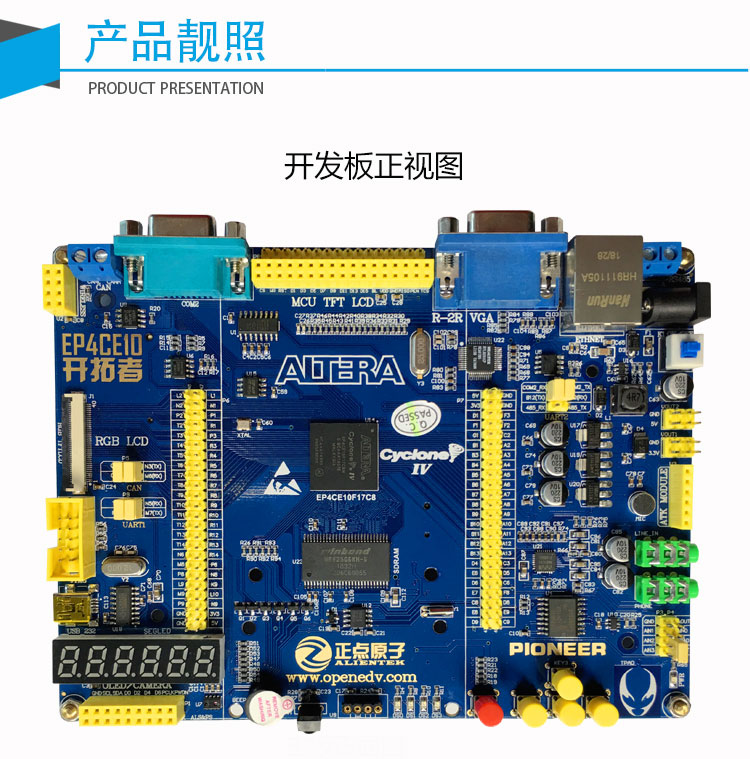

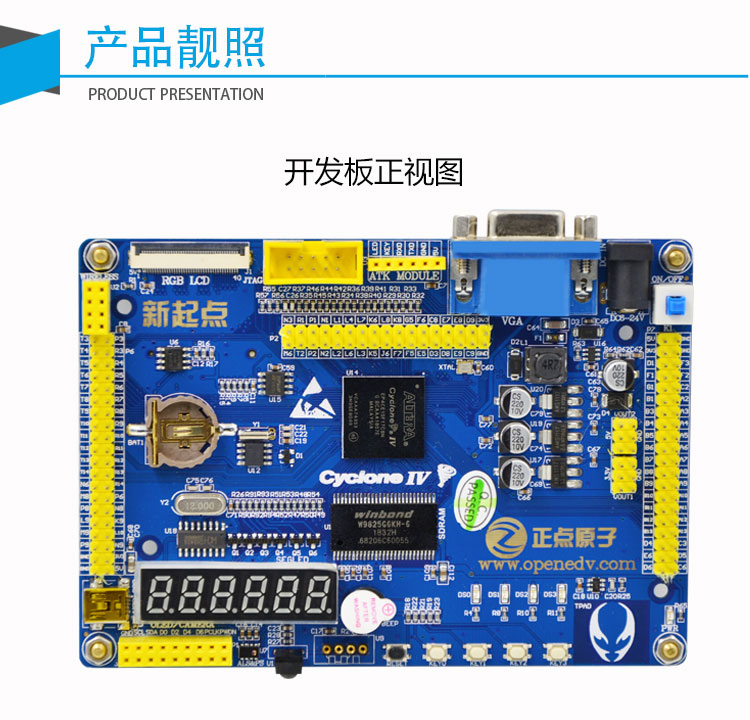

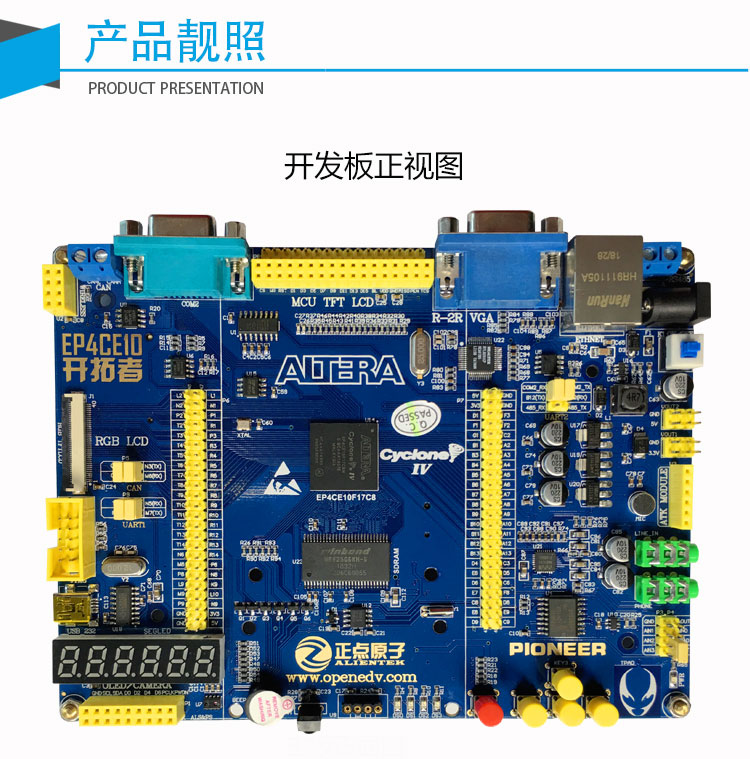

3702 星翼電子:開拓者FPGA開發板資源硬件描述

2019-10-16 09:52:00 3288

3288

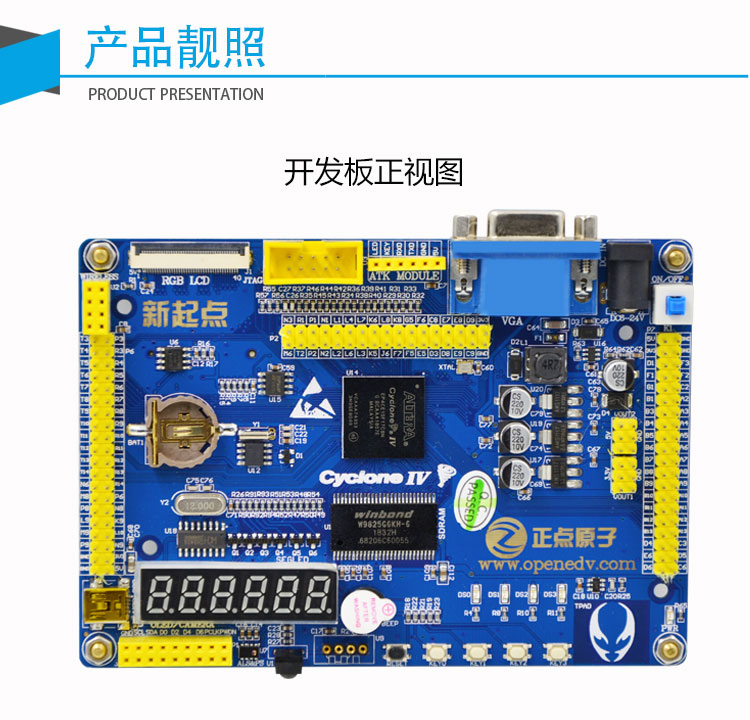

星翼電子:新起點FPGA開發板硬件資源描述

2019-10-16 11:51:10 3472

3472

雖然很多 FPGA 工程師都是寫代碼,但是作為硬件編程工程師,如果不熟悉 FPGA 的底層資源和架構,是很難寫出高質量的代碼——至少很難寫出復雜邏輯的高質量代碼,也很難站在系統的層面去考慮芯片的選型等問題。那熟悉 FPGA 架構,首先最主要的一點,我們先來了解 FPGA 的 IO。

2020-07-16 17:53:02 9031

9031

在使用 FPGA 過程中,通常需要對資源做出評估,下面簡單談談如何評估 FPGA 的資源。 FF 和 LUT 的數目:這個在寫出具體代碼之前,初學者通常沒法估算,但資深 FPGA 工程師會估算

2020-12-28 07:59:00 8

8 區域(Region):每個FPGA器件被分為多個區域,不同的型號的器件區域數量不同。

FPGA時鐘資源主要有三大類:時鐘管理模、時鐘IO、時鐘布線資源。

時鐘管理模塊:不同廠家及型號的FPGA

2020-12-09 14:49:03 20

20 FPGA時鐘資源主要有三大類 時鐘管理模、時鐘 IO 、時鐘布線資源。

2020-12-09 18:14:00 13

13 本文檔的主要內容詳細介紹的是FPGA硬件基礎之理解FPGA時鐘資源的工程文件免費下載。

2020-12-10 14:20:11 6

6 本文檔的主要內容詳細介紹的是FPGA硬件基礎之FPGA時鐘資源的工程文件免費下載。

2020-12-10 15:00:29 15

15 了關于FPGA架構和基本組成《FPGA學習–架構和基本組成單元(一)》 ,下面參考Xilinx Vivado官方文檔學習硬件設計的基本概念。

2020-12-25 17:34:36 22

22 DDR3。 2.FPGA架構設計問題 我們知道,FPGA片上分布著各種資源,如時鐘,serdes,RAM,LUT,IO等。在進行FPGA規劃時候,應當需要知道項目設計需求,以及需求各模塊之間的數據交織情況,這樣可以避免

2021-01-07 10:15:31 4645

4645

也被設計成支持非常高頻率的信號。了解全局時鐘的信號路徑可以擴展對各種全局時鐘資源的理解。全局時鐘資源和網絡由以下路徑和組件組成: 時鐘樹和網絡:GCLK 時鐘區域 全局時鐘緩沖器 1. 時鐘樹和網絡:GCLK 7系列FPGA時鐘樹設計用于低偏差和低功

2021-03-22 10:09:58 11527

11527

本文通過一個設計實例,介紹了基于電子系統級設計,的軟硬件劃分在嫡解碼器中的應用在視頻解碼的軟硬件協同設計中,虛擬平臺在協同驗證時指出每比特消耗的時鐘過多,需要對設計進行修改通過合理的軟硬件劃分

2021-03-29 11:25:37 7

7 中的重構區域劃分和任務調度決定了整個系統的性能,因此如何對DPR系統的邏輯資源劃分和調度問題進行建模,并設計高效的求解算法是保證系統性能的關鍵。在建立劃分和調度模型的基礎上,設計了基于模擬退火( SimulatedΔ nnealing,SA)的DPR系統劃分-調度聯合優化算法,用于優化重構區域的劃分方案和任務調

2021-05-13 10:39:19 5

5 隨著FPGA的不斷發展,FPGA本身自帶的PCIE硬核的數量越來越多,本文以ZU11EG為例介紹,如何進行對應的硬件引腳分配。 設計目標:ZU11EG FFVC1760封裝,掛載4組NVME,接口

2021-06-27 11:20:53 5951

5951

【正點原子FPGA連載】第三章 硬件資源詳解 -摘自【正點原子】新起點之FPGA開發指南_V2.1

2021-11-21 14:06:03 19

19 (06)FPGA資源評估1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA資源評估5)結語1.2 FPGA簡介FPGA(Field Programmable Gate

2021-12-29 19:40:45 6

6 在設計初期,為解決兩臺設備間的協同問題,我們通過 OpenHarmony 提供的分布式設備虛擬化能力將兩臺設備的硬件資源進行融合,實現了“一對一”的硬件資源訪問。這便是硬件資源池化模型的雛形。

2022-05-11 10:24:33 1223

1223 關于 FPGA 的 IO資源分析共分為三個系列進行具體闡述,分別為: IO資源:分析FPGA IO資源的電氣特性; IO邏輯資源:分析FPGA的輸入輸出數據寄存器、DDR工作方式、可編程輸入延時

2022-12-13 13:20:06 1099

1099 中國無線電頻率劃分圖:頻譜資源的劃分能幫助理解各頻率的占用情況。

2023-06-12 09:51:26 2631

2631

FPGA的BRAM和LUT等資源都是有限的,在FPGA開發過程中,可能經常遇到BRAM或者LUT資源不夠用的情況。

2023-08-30 16:12:04 949

949

FPGA(Field Programmable Gate Array)是一種可編程邏輯器件,它是由大量的可編程邏輯單元(查找表、觸發器等)和可編程互連資源組成的。FPGA的靈活性和可重構性使其在數字系統設計中得到了廣泛應用。

2023-09-28 17:22:48 718

718 隨著 FPGA 的不斷發展,FPGA本身自帶的PCIE硬核的數量越來越多,本文以ZU11EG為例介紹,如何進行對應的 硬件 引腳分配。 設計目標:ZU11EG FFVC1760封裝,掛載4組NVME

2023-12-14 15:45:01 194

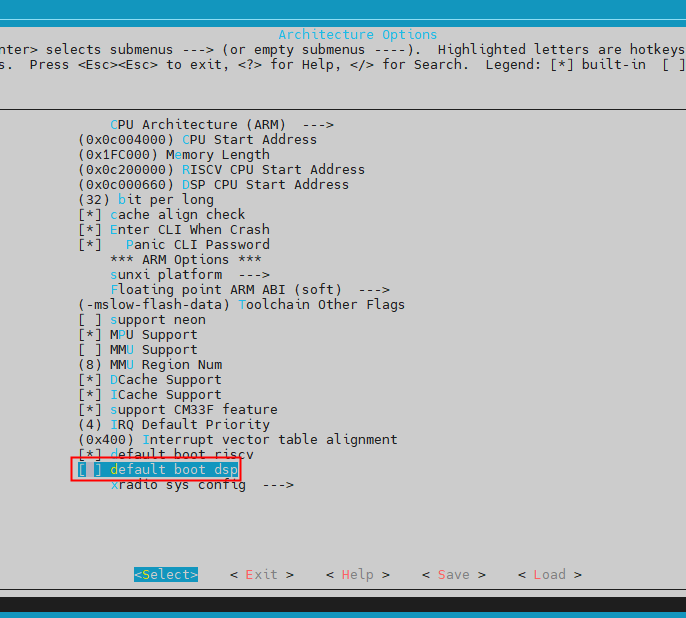

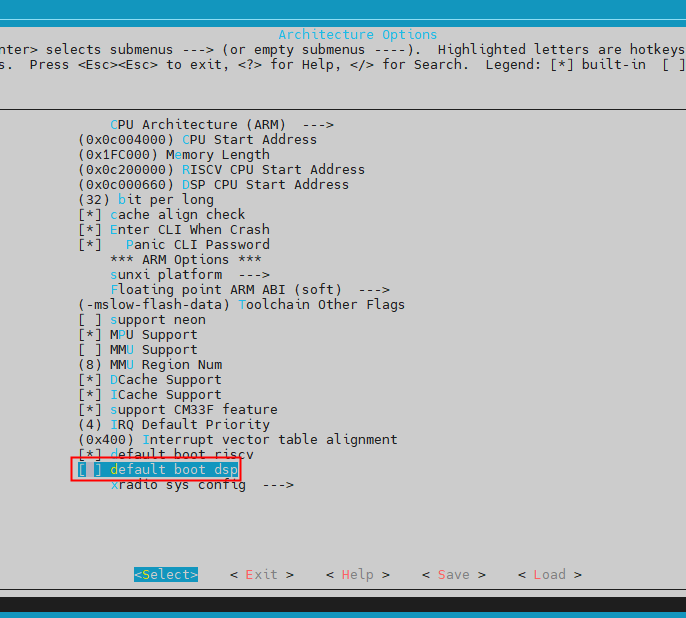

194 下面簡單介紹一下 R128 方案的資源劃分與啟動流程。 資源劃分 CPU 資源劃分 這只是默認配置方案,CPU 資源劃分可以按照需求任意修改 CPU 功能說明 M33 控制核。運行 WI-FI/BT

2023-12-22 17:46:07 240

240

FPGA(現場可編程門陣列)屬于硬件設備,而不是軟件。它是一種可編程的硬件設備,由大量的邏輯單元、存儲單元和互連資源組成,能夠實現復雜的數字電路和系統設計。

2024-03-14 17:08:59 124

124

電子發燒友App

電子發燒友App

評論