隨著EDA技術的高速發展, 以大規模和超大規模器件FPGA/CPLD為載體、以VHDL(硬件描述語言)為工具的電子系統設計越來越廣泛。有限狀態機(簡稱狀態機)作為數字系統控制單元的重

2010-09-07 18:07:56 1998

1998

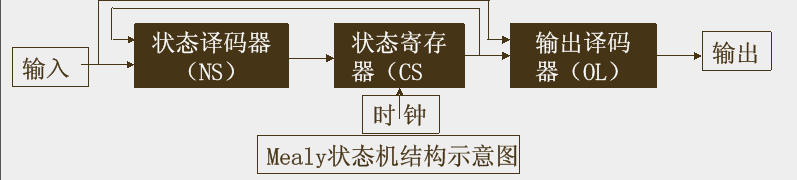

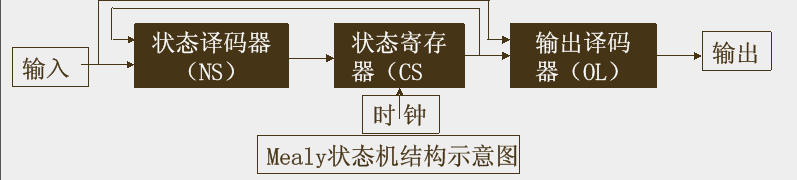

安全高效的狀態機設計對于任何使用FPGA的工程師而言都是一項重要技能。選擇Moore狀態機、Mealy狀態機還是混合機取決于整個系統的需求。無論選擇哪種類型的狀態機,充分掌握實現方案所需的工具和技巧,將確保您實現最佳解決方案。本文主要介紹如何在FPGA中實現狀態機

2013-03-29 15:02:57 12361

12361

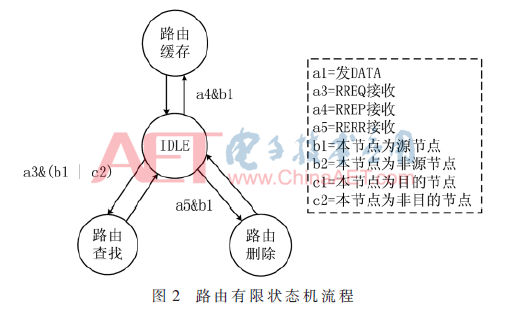

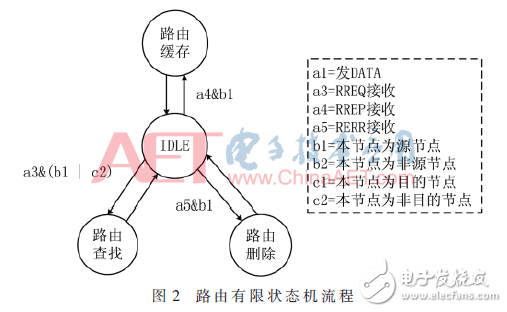

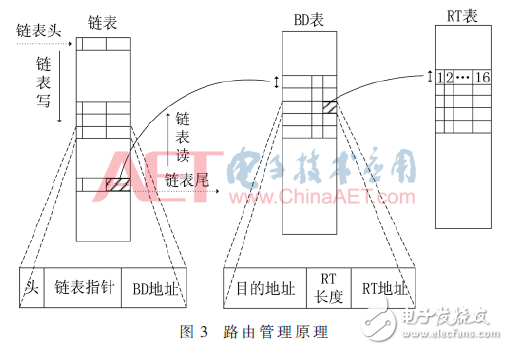

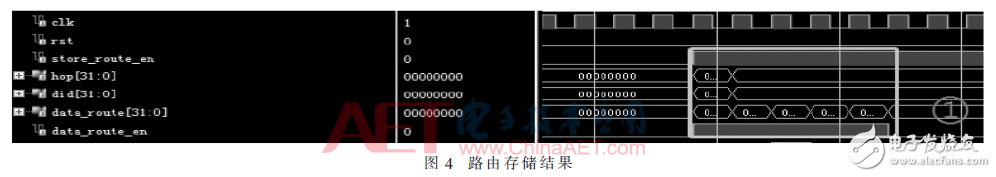

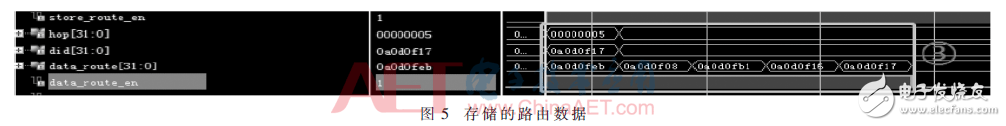

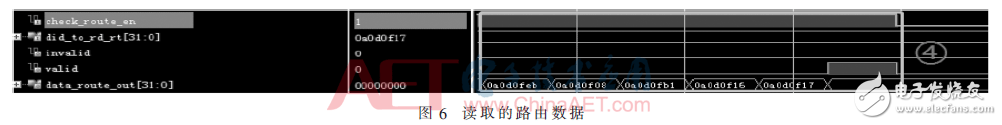

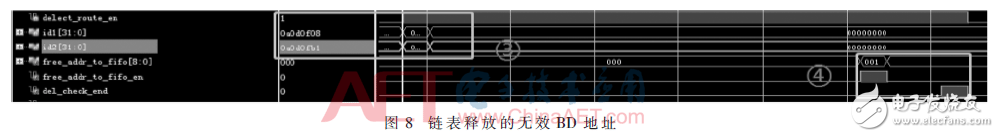

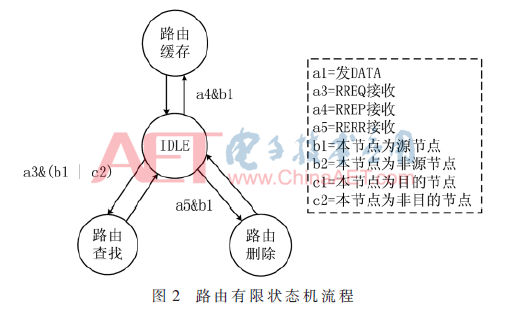

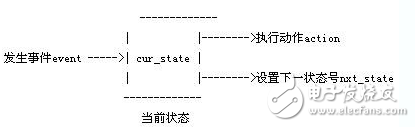

本文為在FPGA中支持DSR協議的路由表項管理功能,設計一種基于有限狀態機[8]的實現方法。

2020-12-22 16:27:25 1921

1921

關于狀態機,基礎的知識點可以自行理解。本文主要講解的是一個有限狀態機FSM通用的寫法,目的在于更好理解,移植,節省代碼閱讀與調試時間,體現出編程之美。

2023-09-13 09:28:42 282

282

狀態機建模是使用狀態圖和方程式的手段,創建基于混合信號的有限狀態機模型的一種建模工具。

2023-12-05 09:51:02 429

429

的是有限狀態機(Finite-State Machine,FSM),簡稱為狀態機,表示在有限個狀態以及這些狀態之間的轉移和動作等行為的數學模型。 二、分類 在verilog中常使用的狀態機可以分為兩類,分別是Moore(摩爾)狀態機和Mealy(米利)狀態機。兩種狀態機的主要區別在于

2024-02-12 19:07:39 1818

1818

關于有限狀態機的總結資料,比較全面,特別分享下。

2016-04-16 13:22:10

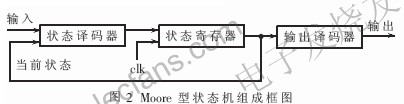

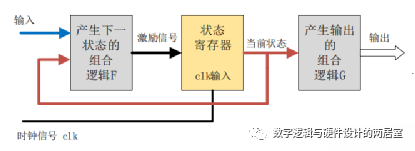

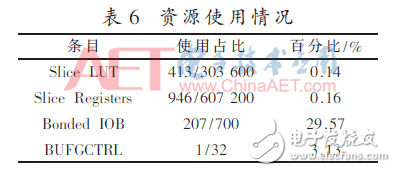

數字系統有兩大類有限狀態機(Finite State Machine,FSM):Moore狀態機和Mealy狀態機。Moore狀態機 其最大特點是輸出只由當前狀態確定,與輸入無關。Moore狀態機

2012-03-09 10:04:18

FPGA有限狀態機

2013-09-08 08:45:17

FPGA狀態機的文書資料

2014-09-14 19:01:20

在實際的應用中,根據有限狀態機是否使用輸入信號,設計人員經常將其分為Moore型有限狀態機和Mealy型有限狀態機兩種類型。

2020-04-06 09:00:21

軟件開發第四講 - 按鍵檢測(狀態機)一、工具鏈接1、Keil c51 UV4https://yunpan.360.cn/surl_yrIfYYmeRFk2、STC-ISP下載軟件https

2022-02-18 06:51:28

等待一段時間后,光標的位置就會右移,表示對最后輸入字符的確認。因此,按鍵輸入接口設計和實現的核心,更多的體現在軟件接口處理程序的設計中。下面將以此為例,介紹有限狀態機的分析設計原理,以及基于狀態機思想

2008-07-10 18:00:24

本文檔旨在提供有關 ST 的 ISM330DHCX嵌入式有限狀態機的使用和配置的信息。ISM330DHCX 可配置為由用戶定義的運動模式激活中斷信號生成。為此,最多可以為運動檢測獨立編程 16 組嵌入式有限狀態機。

2023-09-08 08:00:23

本文檔旨在提供有關 ST 的 LSM6DSOX 嵌入式有限狀態機的使用和配置的信息。LSM6DSOX 可配置為由用戶定義的運動模式激活中斷信號生成。為此,最多可以為運動檢測獨立編程 16 組嵌入式有限狀態機

2023-09-06 06:36:09

本文檔旨在提供有關 ST 的 LSM6DSOX 嵌入式有限狀態機的使用和配置的信息。LSM6DSOX 可配置為由用戶定義的運動模式激活中斷信號生成。為此,最多可以為運動檢測獨立編程 16 組嵌入式有限狀態機。

2023-09-13 07:33:03

MOORE型有限狀態機的幾種設計方法是什么VHDL設計MOORE型有限狀態機時速度問題是什么

2021-05-07 06:01:38

本帖最后由 御宇1995 于 2015-6-6 15:06 編輯

實驗課要用FPGA(Altera的cycloneIV)實現交通燈,有用狀態機和非狀態機兩種方法,以下是代碼狀態機實現(一個數

2015-06-06 15:03:52

狀態機編程的歷史很可能久于傳統的操作系統, 傳統的一個大while 循環模式普遍用到了狀態機模式編程, 狀態機一般是基于fsm 的有限狀態機,或者更先進點的是hsm 分層的狀態機。具體的fsm 以及

2013-02-27 14:35:10

當狀態機進入一個狀態后,是把里面里面的代碼執行一遍,還是一直執行,一直到狀態發生改變

2014-04-03 18:38:21

狀態機設計實例實驗目的:1.學習狀態機的相關概念2.理解一段式、兩段式以及三段式狀態機的區別以及優缺點實驗平臺:無實驗原理:狀態機全稱是有限狀態機(finite-state machine,縮寫

2016-12-26 00:17:38

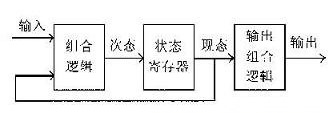

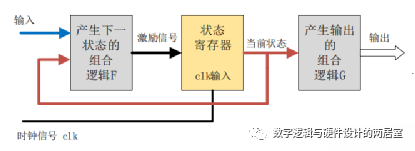

組合電路輸出,也可以時序電路輸出)。一般而言,推薦的FSM 描述方法是后兩種。這是因為:FSM和其他設計一樣,最好使用同步時序方式設計,以提高設計的穩定性,消除毛刺。狀態機實現后,一般來說,狀態轉移部分

2015-05-25 20:33:02

的UART的實現方法,具體描述了發送、接收等模塊的設計,恰當使用了有限狀態機,實現了FPGA片上UART的設計,給出了仿真結果。關鍵詞:通用異步收發器;串口通信;現場可編程邏輯器件;有限狀態機

2019-06-21 07:17:24

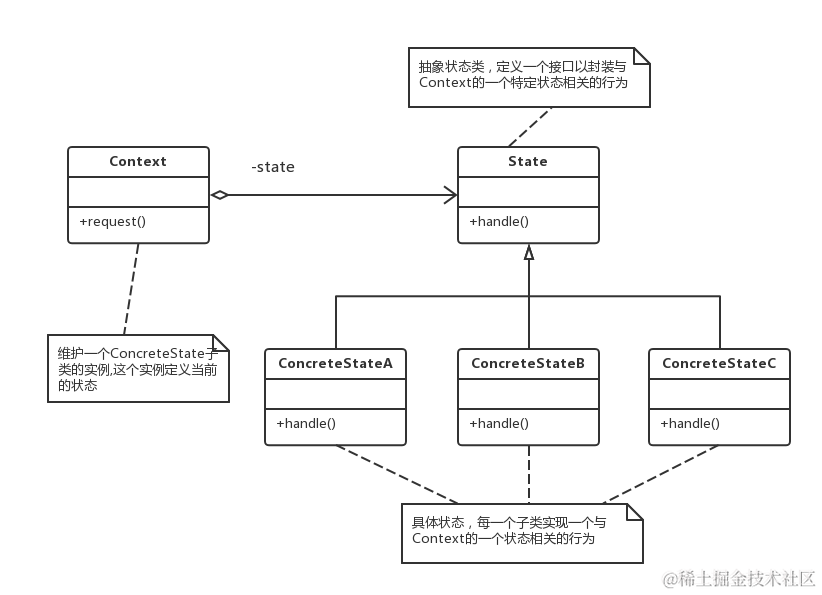

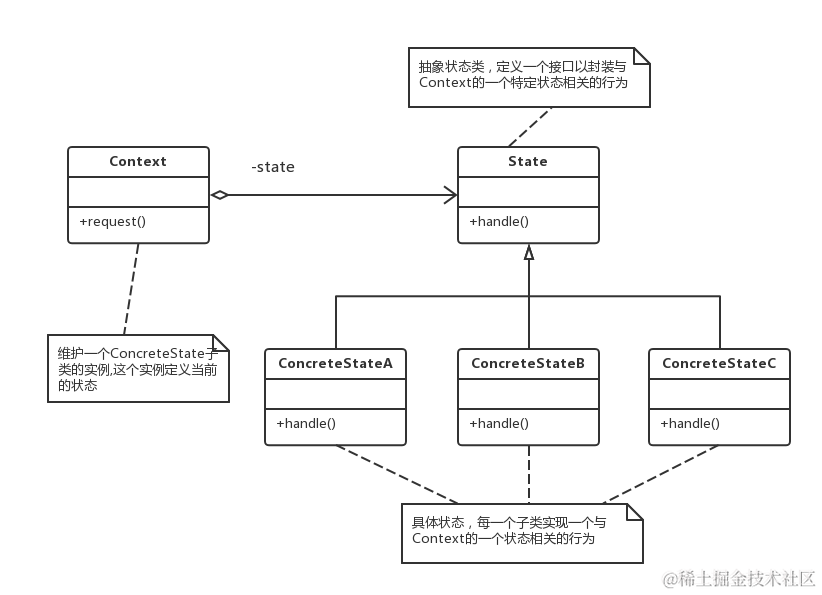

什么是有限狀態機FSM簡述 有限狀態機(以下用FSM指代)是一種算法思想,簡單而言,有限狀態機由一組狀態、一個初始狀態、輸入和根據輸入及現有狀態轉換為下一個狀態的轉換函數組成。在Gof的23種

2008-06-04 10:35:23

在嵌入式,機器人領域,由于多的復雜邏輯狀態,我們編寫程序的時候不得不考慮很多種情況,容易造成功能間的沖突。有限狀態機(finite-state machine),簡稱狀態機,是一種表示有限個狀態以及狀態間轉移等行為的數學模型。狀態機簡單來說

2021-12-20 06:51:26

文章目錄1、什么是狀態機?2、狀態機編程的優點(1)提高CPU使用效率(2) 邏輯完備性(3)程序結構清晰3、狀態機的三種實現方法switch—case 法表格驅動法函數指針法小節摘要:不知道大家

2021-12-22 06:51:58

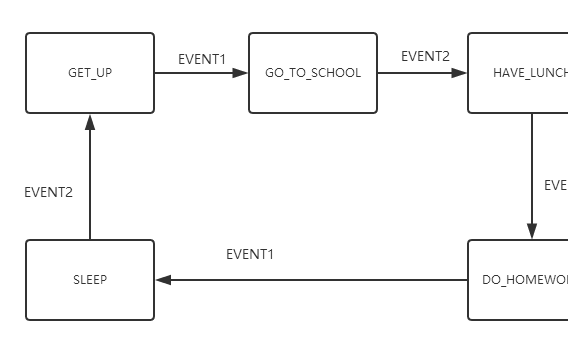

STM32實現按鍵有限狀態機(超詳細,易移植)一、狀態機簡而言之,狀態機是使不同狀態之間的改變以及狀態時產生的相應動作的一種機制。1.1狀態機的四要素現態:狀態機當前狀態。觸發條件:改變當前狀態

2022-02-16 06:58:52

什么是有限狀態機FSM呢?如何去實現有限狀態機FSM的程序設計呢?

2022-01-21 07:04:39

如何建立有限狀態機的模型?如何利用狀態機進行軟件設計?如何使用狀態機的效能分析?

2021-04-28 06:21:24

應用,往往需要讓硬件來實現一些具有一定順序的工作,這就是要用到狀態機的思想。(以上摘自特權同學的《深入淺出玩轉FPGA》一書) 有限狀態機FSM(Finite State Machine)是數字電路

2014-09-25 09:35:29

有限狀態機是什么?怎樣使用狀態機思想進行編程呢?有哪些建議?

2022-02-25 06:19:58

利用 VHDL 設計的許多實用邏輯系統中,有許多是可以利用有限狀態機的設計方案來描述和實現的。無論與基于 VHDL的其它設計方案相比,還是與可完成相似功能的 CPU 相比,狀

2008-06-04 10:33:10 75

75 提出了一種改進的遺傳算法,針對有限狀態機中輸出矢量與狀態轉移相關的特性,將配置有限狀態機的染色體分解為狀態轉移基因和輸出矢量基因進行分階段的進化實驗。實驗結

2009-05-10 11:55:33 18

18 通過一個基于操作規程的虛擬訓練系統研究了系統仿真流程,分析了有限狀態機(FSM)的原理,結合虛擬仿真訓練的特點,設計出了操作過程模型,并通過Windows 消息機制編程實

2009-12-07 14:23:01 14

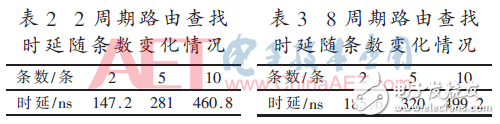

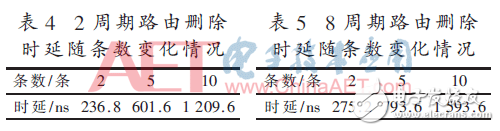

14 TCAM(Ternary Content-Addressable Memory) 能夠很好的完成最長前綴匹配,實現快速路由查找和分組轉發,但是其對路由表項的有序性要求使得表項管理比較復雜。在討論已有TCAM 表項管理算法

2009-12-22 14:10:59 23

23 實驗目的

1、 熟悉用硬件描述語言(VHDL)設計一般狀態機所包含的幾個基本部分;2、 掌握用硬件描述語言(VHDL)設計Moore型和Mealy型有限狀態機的方法;3、 了解狀態

2010-09-03 09:48:17 0

0 基于有限狀態機在LIN總線開發中的應用

引言

隨著汽車智能化程度的提高和迅速升級

2010-04-20 13:47:43 737

737

本文用Verilog HDL語言,結合有限狀態機的設計方法實現了UART的功能,將其核心功能集成到FPGA上,使整體設計緊湊、小巧,實現的UART功能穩定、可靠;同時,利用有限狀態機的方法具有結

2011-08-25 13:15:53 4439

4439

設計了有限狀態機模型,實現了對不同設備命令的統一轉換。基于統一命令轉換,實現了Telnet對遠程設備的統一命令配置,通過SNMP協議可視化配置設備更加方便。

2011-12-14 14:35:47 22

22 有限狀態機及其設計技術是數字系統設計中的重要組成部分,是實現高效率、高可靠性邏輯控制的重要途徑。本文論述了兩種針對狀態機的綜合策略實現

2012-01-05 10:34:21 2055

2055

為了能夠更簡潔嚴謹地描述MTM總線的主模塊有限狀態機的狀態轉換,同時減少FPGA芯片功耗,提高系統穩定性,文中在分析MTM總線結構和主模塊有限狀態機模型的基礎上,基于VHDL語言采

2012-05-29 15:39:09 20

20 Transmitter 通用異步收發器) 。 重點討論了使用 FSM(有限狀態機) 技術進行接收器和發送器兩大核心模塊的設計實現 以及接收器能夠正常工作的關鍵技術 ———倍頻采樣技術。

2016-03-22 15:52:23 4

4 本文詳 細論述了高速狀態機的錯步問題以及控制層中狀態機的狀態劃分問題,結合具體的應用實例,給出了基于狀態機的實現方法。

2016-03-22 15:48:30 3

3 本文主要介紹了IP模塊的有限狀態機的實現。

2016-03-22 15:42:47 0

0 本文通過舉例 利用VHDL 語言描述了不同模式的有限狀態機 分析了有限狀態機在 PLD 中綜合的特點 。

2016-03-22 15:41:36 3

3 如何使嵌入式軟件代碼更加可靠 增強程序的可維護性 一直以來都是嵌入式程序員追 求的目標。論述了有限狀態機的原理和其實現方法;采用狀態機方法編寫了一個按鍵掃描程序介紹了狀態機編程在嵌入式系統中的實際應用和優點。

2016-03-22 15:40:22 1

1 本文提出一種優秀 、高效的 Verilog HDL 描述方式來進行有限狀態機設計 介紹了 有限狀態機的建模原則 并通過一個可綜合的實例 驗證了 該方法設計的有限狀態機在面積和功耗上的優勢。

2016-03-22 15:19:41 1

1 EDA的有限狀態機,廣義而言是指只要涉及觸發器的電路,無論電路大小都可以歸結為狀態機。有限狀態機設計在學習EDA時是很重要的一章。

2016-06-08 16:46:10 3

3 有限狀態機在數控系統軟件中的應用研究,感興趣的小伙伴們可以看看。

2016-07-26 10:43:06 20

20 有限狀態機在嵌入式軟件中的應用,感興趣的小伙伴們可以看看。

2016-07-26 10:43:06 27

27 基于有限狀態機的五橋臂逆變器改進調制策略_梅楊

2017-01-08 13:58:48 0

0 有限狀態機(FSM)是一種常見的電路,由時序電路和組合電路組成。設計有限狀態機的第一步是確定采用Moore狀態機還是采用Mealy狀態機。

2017-02-11 13:51:40 3881

3881

基于有限狀態機的Linux多點觸摸屏驅動設計_劉斌

2017-03-15 08:00:00 0

0 ”,當系統時鐘頻率、操作密度大幅提高時,極易引起時序邏輯錯誤。為此,研究了一種基于存儲器映射的有限狀態機邏輯實現方法,對FPGA資源進行選擇性使

2017-11-17 02:30:07 3184

3184

和通用性上都不理想。針對RICE算法中自適應熵編碼的特點,設計了一種基于有限狀態機和查找表的并行RICE解碼結構,可在FPGA上完成8比特寬度的并行解碼,解碼速度最高可達176 MB/s;同時,該解碼結構適用于編碼參數足變化的情況,具有很強的通用性。

2017-11-20 14:21:55 8

8 本文主要介紹了是如何利用74LS161實現復雜狀態機的。時序邏輯電路的數學模型是有限狀態機。有限狀態機它把復雜的控制邏輯分解成有限個穩定狀態,在每個狀態上判斷事件,變連續處理為離散數字處理,符合計算機的工作特點。本文主要討論使用MSI同步計數器74LS161進行復雜狀態機的設計。

2018-01-18 09:00:02 8299

8299

隨著微電子技術的迅速發展,人們對數字系統的需求也在提高。不僅要有完善的功能,而且對速度也提出了很高的要求。對于大部分數字系統,都可以劃分為控制單元和數據單元兩個組成部分。通常,控制單元的主體是一個有限狀態機,它接收外部信號以及數據單元產生的狀態信息,產生控制信號序列。

2019-06-10 08:03:00 4833

4833

有限狀態機(finite state machine)簡稱FSM,表示有限個狀態及在這些狀態之間的轉移和動作等行為的數學模型,在計算機領域有著廣泛的應用。FSM是一種邏輯單元內部的一種高效編程方法,在服務器編程中,服務器可以根據不同狀態或者消息類型進行相應的處理邏輯,使得程序邏輯清晰易懂。

2019-05-15 16:53:39 1813

1813

狀態機有三種描述方式:一段式狀態機、兩段式狀態機、三段式狀態機。下面就用一個小例子來看看三種方式是如何實現的。

2019-08-29 06:09:00 2514

2514

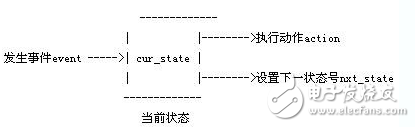

有限狀態機是一種具有離散輸入輸出系統的模型,在任何時刻都處于一個特定的狀態。對于事件驅動的程序設計,它是非常有用的設計模型。在某一個狀態下有事件發生時,根據當前狀態和輸入事件的不同,選擇如何處

2020-05-03 17:49:00 2402

2402 摩爾型的有限狀態機的輸出只與當前狀態有關,而與輸入信號的當前值無關,且僅豐時鐘信號邊沿到來時才發生變化。

2020-08-08 10:57:00 7841

7841

之前寫過一篇狀態機的實用文章,很多朋友說有幾個地方有點難度不易理解,今天給大家換種簡單寫法,使用函數指針的方法實現狀態機。 狀態機簡介 有限狀態機FSM是有限個狀態及在這些狀態之間的轉移和動作等行為

2020-10-19 09:36:53 2141

2141

有限狀態機是絕大部分控制電路的核心結構, 是表示有限個狀態以及在這些狀態之間轉移和動作等行為的數學模型。有限狀態機是指輸出取決于過去輸入部分和當前輸入部分的時序邏輯電路。一般來說, 除了輸入部分和

2020-11-04 17:17:04 12

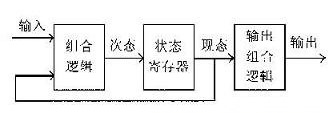

12 是FPGA設計中一種非常重要、非常根基的設計思想,堪稱FPGA的靈魂,貫穿FPGA設計的始終。 02. 狀態機簡介 什么是狀態機:狀態機通過不同的狀態遷移來完成特定的邏輯操作(時序操作)狀態機是許多數字系統的核心部件, 是一類重要的時序邏輯電路。通常包括三個部分: 下一個

2020-11-05 17:58:47 6145

6145

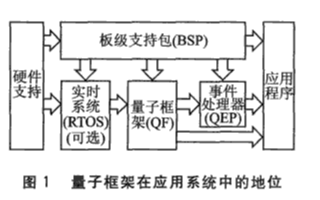

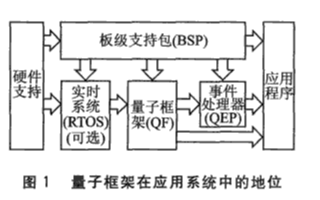

工作的能力,其信息傳輸的確定性離不開其內部的時鐘同步機制的支持。時鐘同步機制可根據該節點啟動的不同工作階段,定義成不同的工作狀態,如初始化、等待接收同步幀等。考慮到傳統的FSM方法建立模型存在代碼難以復用、維護困難等問題,本文基于量子框架的角度,采用有限狀態機的方法對FlexRay時鐘同步機制進行研究。

2021-03-31 10:22:27 2908

2908

Synplify的優勢之一是有限狀態機編譯器。 這是一個強大的功能,不僅具有自動檢測狀態機中的狀態的能力源代碼,并使用順序編碼,灰色編碼或一鍵編碼實現它們。但也要進行可達性分析,以確定所有可能的狀態達到并優化掉所有無法達到的狀態和轉換邏輯。因此,產生狀態機的高度優化的最終實現。

2021-04-07 09:20:51 12

12 有限狀態機的設計是HDL Designer Series?工具的關鍵應用。 盡可能地對于設計人員編寫導致狀態機性能不佳的VHDL,可以使用HDL Designer用于生成VHDL的Series?工具

2021-04-08 10:05:23 3

3 經典雙進程狀態機的FPGA實現(含testbeach)(肇慶理士電源技術有限公司圖片)-該文檔為經典雙進程狀態機的FPGA實現(含testbeach)總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………? ??

2021-08-31 13:26:52 3

3 ? 一、介紹 EFSM(event finite state machine,事件驅動型有限狀態機),是一個基于事件驅動的有限狀態機,主要應用于嵌入式設備的軟件系統中。 EFSM的設計原則是:簡單

2021-11-16 15:29:10 2036

2036 制作航模遙控器需要用到多按鍵檢測,使用有限狀態機實現檢測短按、長按,修正了原文中的一些錯誤

2021-11-26 11:21:04 36

36 STM32實現按鍵有限狀態機(超詳細,易移植)一、狀態機簡而言之,狀態機是使不同狀態之間的改變以及狀態時產生的相應動作的一種機制。1.1狀態機的四要素現態:狀態機當前狀態。觸發條件:改變當前狀態

2021-12-17 18:37:10 25

25 關注、星標公眾號,直達精彩內容文章來源:頭條-嵌入式在左C語言在右鏈接:https://www.toutiao.com/i6843028812112855564/有限狀態機概念有限狀態機...

2022-01-13 13:32:23 14

14 有限狀態機又稱有限狀態自動機,簡稱狀態機,是表示有限個狀態以及在這些狀態之間的轉移和動作等行為的數學計算模型,用英文縮寫也被簡...

2022-02-07 11:23:28 4

4 FSM有限狀態機,序列產生,序列檢測,是FPGA和數字IC相關崗位必須要掌握的知識點,在筆試和面試中都非常常見。

2022-03-14 17:42:09 12848

12848 本文描述了有限狀態機的基礎知識,并展示了在 Verilog 硬件描述語言中實現它們的實用方法。

2022-04-26 16:20:01 2850

2850

電子發燒友網站提供《帶有有限狀態機的機械臂對象收集器.zip》資料免費下載

2022-12-27 10:08:22 0

0 EFSM(event finite state machine,事件驅動型有限狀態機),是一個基于事件驅動的有限狀態機,主要應用于嵌入式設備的軟件系統中。

2023-02-11 10:17:15 709

709 在Verilog HDL中可以用許多種方法來描述有限狀態機,最常用的方法是用always語句和case語句。

2023-03-23 14:06:11 374

374 有限狀態機是由寄存器組和組合邏輯構成的硬件時序電路,其狀態(即由寄存器組的1和0的組合狀態所構成的有限個狀態)只可能在同一時鐘跳變沿的情況下才能從一個狀態轉向另一個狀態,究竟轉向哪一狀態還是留在原狀態不但取決于各個輸入值,還取決于當前所在狀態。這里是指Mealy型有限狀態機。

2023-04-07 09:52:46 909

909 有限狀態機(Finite-State Machine,FSM),簡稱狀態機,是表示有限個狀態以及在這些狀態之間的轉移和動作等行為的數學模型。

2023-06-01 15:23:39 1260

1260

狀態機往往是FPGA 開發的主力。選擇合適的架構和實現方法將確保您獲得一款最佳解決方案。 FPGA 常常用于執行基于序列和控制的行動, 比如實現一個簡單的通信協議。對于設計人員來說,滿足這些行動

2023-07-18 16:05:01 499

499

電子發燒友網站提供《LSM6DSOX嵌入式有限狀態機的使用和配置.pdf》資料免費下載

2023-07-31 10:55:11 0

0 EFSM(event finite state machine,事件驅動型有限狀態機),是一個基于事件驅動的有限狀態機,主要應用于嵌入式設備的軟件系統中。 EFSM的設計原則是:簡單!EFSM的使用者只需要關心:

2023-08-30 09:28:51 448

448

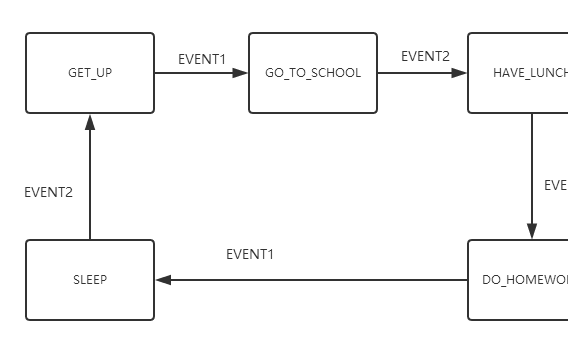

有限狀態機,簡稱狀態機,通俗的說,就是把全部的情況分成幾個場景,這些場景的工作方式明顯不同。簡單來說就是如下所示的狀態轉移圖

2023-08-31 15:30:49 585

585

如果一個對象(系統或機器),由若干個狀態構成,在某種條件下觸發這些狀態,會發生狀態相互轉移的事件,那么此對象稱之為狀態機。

2023-09-17 16:42:34 1513

1513 BGP有限狀態機共有六種狀態,分別是Idle、Connect、Active、OpenSent、OpenConfirm和Established。

2023-10-07 14:56:55 897

897 有限狀態機分割設計,其實質就是一個狀態機分割成多個狀態機

2023-10-09 10:47:06 330

330 狀態機,又稱有限狀態機(Finite State Machine,FSM)或米利狀態機(Mealy Machine),是一種描述系統狀態變化的模型。在芯片設計中,狀態機被廣泛應用于各種場景,如CPU指令集、內存控制器、總線控制器等。

2023-10-19 10:27:55 3396

3396 電子發燒友網站提供《基于有限狀態機的車身防盜報警的實現.pdf》資料免費下載

2023-10-26 09:48:48 0

0 路由表:簡單點說路由表就是路由器用于指導數據包如何轉發的表項,記錄了去往目的IP的下一跳去哪里(如下圖)。

2023-12-04 09:36:36 2073

2073

有限狀態機(Finite State Machine,簡稱FSM)是一種用來進行對象行為建模的工具,其作用主要是描述對象在它的生命周期內所經歷的狀態序列以及如何響應來自外界的各種事件。

2024-02-17 16:09:00 611

611

電子發燒友App

電子發燒友App

評論