傳統的低功耗MCU設計都是以8位MCU為主,因為8位內核閾門相對較少,運行或泄露電流低,售價也相對低廉。但是,許多新興的應用都需要比8 位元內核更大的處理效率。近年智能生活的抬頭、物聯網的建立,手持式消費性電子產品與無線功能需求越來越高、設計越來越復雜,要提高性能的同時又要兼顧低功耗,需要有一高性能低功耗的主控MCU來作為平臺。另一方面,工業上的智能化也在展開,如遠端監控、數位化、網路化等。簡單說來,就是人物之連結(云端應用)、物物之連結(物聯網) 需求越來越多,導致產品功能越來越復雜,運算量越來越高,2009年ARM發表了32位Cortex-M0內核,提供 MCU 廠商一個強而有力的平臺,加上制程微縮技術的進步,嵌入式快閃記憶體制程普及化及降價,主要成本來自記憶體大小及類比周邊和 IO 管腳數量,CPU內核的成本差異已大幅縮短,更促進了高性價比32位元低功耗MCU的快速發展。

MCU功耗來自何處?

在開始討論低功耗 MCU 設計前,必須先探討 MCU功耗的來源,其主要由靜態功耗及運行功耗兩部分組成。考慮實際的應用,最后決定系統功耗性能指標則必須計算平均功耗。

運行功耗

現代 MCU 已整合相當多的的類比周邊,不能單純考量數字電路的動態功耗。MCU運行時的總功耗由類比周邊功耗和數字周邊的動態功耗相加而得。類比電路的功耗通常由工作電壓及其性能要求指標來決定,例如 100 ns傳遞延遲 (Propogation Delay)的比較器工作電流可能約為 40 微安,當允許傳遞延遲規格為 1 μs時,工作電流有機會降到個位數微安。

數字電路的動態功耗主要來自開關頻率、電壓及等效負載電容,其計算公式如下:

PDynamic (動態功耗) ~ f (工作頻率) x CL (等效負載電容) x VDD 2 (工作電壓)

由以上公式可以理解到降低動態功耗最直接的方式為降低工作電壓及工作頻率。但MCU實際應用面通常要求更寬廣的工作電壓及更高的效能。在降低工作電壓方面,可以選擇更新近的制程,并透過 LDO 讓 CPU 內核、數字電路及與管腳輸出入電壓無關的類比周邊在低壓操作,IO 管腳及需要與其他外部電路連接的類比周邊則在較高的系統電壓操作。如此可以兼顧低功耗及寬工作電壓的需求。在降低工作頻率這項參數上,一個設計優良的32位MCU更能突顯其效能優勢,除了直覺的 MIPS 比較之外,32 位元匯流排也代表更高的資料存取頻寬,能以更低的工作頻率達到相同的效能,進而降低整體功耗。另外,如果 MCU 內建與操作頻率相關的類比周邊,例如石英晶體震蕩電路、嵌入式快閃記憶體或電流式 DAC,其電流消耗與轉換頻率成正比,也要納入低功耗 MCU 的動態功耗設計考量。

靜態功耗

傳統靜態功耗的定義是指系統時鐘源關閉時數字電路的漏電流。但是在混合信號低功耗 MCU 的設計中要同時考慮下列多種漏電流來源,包含數字電路漏電流、SRAM 漏電流、待機時已關閉的模擬電路漏電流 (例如 ADC,嵌入式快閃記憶體)、待機時不關閉的模擬電路工作電流 (例如 LDO、BOD) 及 IO 管腳的漏電流。因為時鐘源已關閉,影響靜態功耗的主要參數為制程、電壓及溫度。所以降低靜態功耗必須選擇超低功耗制程,但是低功耗制程通常伴隨較高的 Vt,導致低電壓類比周邊設計困難。另外,以MCU待機電流 1微安的規格,代表數字電路漏電 + RAM 保持電流 + LDO 工作電流 + BOD (降壓偵測或重置電路) 工作電流總和必須小于 1微安,對于 Flash,RAM 越來越大及功能越來越多的低功耗 MCU 設計廠商而言,是十分艱巨的挑戰。

平均功耗

在系統級要兼顧低功耗及高效能,必須考慮實際應用面的需求,例如無線環境感測器可能讓 MCU 主時鐘及 CPU 關閉,只開啟低頻時鐘,定時喚醒周邊電路進行偵測,當符合設定條件的事件發生時快速啟動 CPU 進行處理,即使沒有任何事件發生,也必須定時激活 CPU 維持無線感測器網路的連線。在遙控器的應用中,則可能完全將所有時鐘源都關閉,當使用者按鍵時快速喚醒時鐘源及 CPU 進行處理。另外,許多應用都會加入一個MCU作為主機處理器的輔助處理器,用于監控鍵盤或紅外線輸入、刷新顯示器、控制主處理器電源以及智慧電池管理等任務。此時平均功耗比單純的運行功耗或待機功耗更具指標性意義。

平均功耗由下列主要參數組合而成: 運行功耗及運行時間,靜待功耗及待機時間,不同運行模式之間的切換時間。茲以下圖進行說明:

平均電流 (I AVG)計算:

因為進入待機模式時間很短,忽略此段時間的電流消耗,公式可以簡化為:

![]()

由以上公式觀察到除了降低運行電流及靜態待機電流外,降低運行時間、喚醒時間及高低速運行模式切換時間也是降低整機功耗的重要手段。另外,上圖同時指出,低功耗 MCU 支援動態切換運行時鐘頻率是必要的功能。

低功耗 MCU 設計考量

制程選擇

為了達到低功耗的運作,并能有效地在低耗電待機模式下,達到極低的待機功耗,可以透過對制程的選擇而站上基本的要求門檻。在不強調速度極致的某些制程分類,選擇極低元件截止電流制程(如下圖)進行邏輯閘制作,并進行數位設計是方法之一。選擇這種策略的額外效益是,通常也能在降低動態操作電流上,達到較佳的表現。另外,由于高溫大幅增加靜態電流,當溫度由攝氏25度增加到攝氏 85度時,一個典型比例約增加 10 倍的靜態電流,以非低功耗 0.18 微米制程開發的 32 位元 MCU,邏輯閥門數 200K、4KB SRAM 在核心電壓 1.8V、攝氏25度的靜態耗電約為 5 ~ 10 微安,當溫度升高到攝氏 85度時,靜待電流將會飆高到 50 ~100 微安。而低功耗制程在攝氏85度僅約 10微安靜態電流。

低功耗高效能的 CPU內核

早期低功耗 MCU 受限于成本及制程技術,大都選擇 8 位元 CPU 內核,但隨著工業上的智能化也在展開,如遠端監控,數位化、網路化等。簡單說來,就是人物之連結(云端應用)、物物之連結(物聯網) 需求越來越多,導致產品功能越來越復雜,運算量越來越高,8 位元 MCU 已逐漸無法滿足效能需求。 為了兼顧低功耗高效能,選擇適用的 32 位元 CPU 內核乃大勢所趨。

選擇低功耗CPU 內核,除了單位頻率耗電流外,還需要綜合考量緊湊的低記憶體代碼,相同功能所需的代碼越長,除了增加記憶體成本,也代表更長的運行時間及功耗。另外,由于軟件開發成本在后期將會越來越高,大量的參考代碼及更多的第三方開發商的支持,都可以有效降低軟件的開發時間及成本。所以選擇一款更多人使用的 CPU 內核也是重要的考量之一ARM Cortex-M0閥門數僅 27K,使用的電量在 1.8V,超低泄漏 180ULL (Ultra LowLeakage) 僅約50μA/MHz。M0 內核采用Thumb2指令集架構,產生出非常緊湊的低記憶體代碼,進一步降低了電源需求。ARM自 2009 年發表了32位元Cortex-M0內核以來,包括 NXP、新唐科技、ST、Freescale等多家國內外 MCU 大廠相繼投入Cortex-M0 MCU 開發,不論供貨或者品種的齊全度都已十分成熟,投入Cortex-M0的 MCU 開發商也在持續增加中。

低功耗數位電路

對于一般的同步數位電路設計,要使數位單元有效降低操作電流,透過控制時鐘的頻率或截止不需要的時鐘跳動,也是重要的方法。低功耗MCU通常配備豐富的時鐘控制單元,可對各別的數位周邊單元,依照需求做降頻或升頻的操作調整,在達到運作能力的同時,用最低的頻率來運行。但為了達到更彈性的時鐘源配置,可能導致 CPU 內核和周邊電路時鐘不同步的現象,此時必須仔細考慮電路設計,保證跨時鐘領域資料存取的正確性。

另外為了盡量降低 CPU介入處理時間或降低 CPU 工作頻率而節省下來的功耗,可以提供 DMA 或周邊電路相互觸發電路進行資料的傳遞,例如Timer 定時自動觸發 ADC 或 DAC,并透過 DMA 進行資料由 ADC 到 RAM 或者 RAM 到 DAC 的搬移,同時在 ADC 的輸入可以增加簡單的數字綠波及平滑化電路,如此不須要 CPU 經常介入處理,也不會因為需要即時處理 ADC 或 DAC 事件導致中斷程序占用太多時間,降低系統的實時性及穩定性。

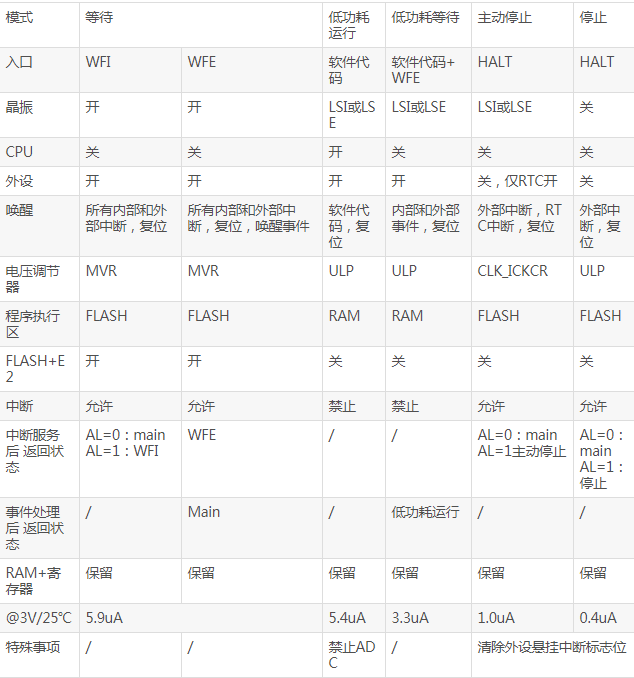

支援多種工作模式

為了配合不同的應用需求,并達到系統平均功耗的最小化,低功耗 MCU需要提供多種操作模式,讓使用者靈活調配應用,常見的操作模式有下列數種:

正常運行模式:CPU 內核及周邊正常工作,能即時改變 CPU 及周邊的工作頻率 (On the Fly) 或關閉不需要的時鐘源以獲得最佳的工作效能。

低頻工作模式:CPU 內核及周邊工作于低頻的時鐘源,例如 32.768K 晶震或內部低頻 10K RC 震蕩器。通常此時最大的耗電來源為嵌入式閃存及 LDO 本身的耗電流。如果此時的執行程序不大,可以考慮將程序運作于 RAM 以降低平均功耗。請注意并不是所有 MCU 都能支援在RAM 執行程序。

Idle 模式:CPU 內核停止,時鐘源和被致能的周邊電路持續工作,直到周邊電路符合設定條件喚醒 CPU 進行資料處理或控制執行流程。通常高頻的運行模式,CPU 及嵌入式快閃記憶體消耗相當大比例的電流,故 Idle 模式能有效降低平均功耗。

待機RAM 保持模式:CPU 內核及所有時鐘源關閉,內建LDO 切換到低耗電模式,但是RAM 及 IO 管腳持續供電,維持進入待機之前的狀態。

RTC 模式:CPU 內核及高頻時鐘源關閉,內建LDO 切換到低耗電模式,由于此時 LDO 供電能力降低,僅能提供低耗電的周邊電路運行,例如 32.768K 晶振、RTC (實時時鐘計數器)、BOD (降壓偵測或重置電路)、TN 單色LCD 直接驅動電路等。

深層待機模式:CPU 內核及所有時鐘源關閉,關閉 RAM 及LDO、BOD 等所有周邊電路的電源,僅IO 管腳(或部分IO管腳)持續供電,由IO管腳或重置 (Reset) 管腳喚醒 CPU。因為此模式下,RAM 的資料已丟失,通常會進行內部電源切割,提供數十個狀態記錄暫存器作為系統重啟時的初始狀態參考源。此模式的優點是更低的靜態電流,通常僅需 100nA ~ 500nA,其缺點是并非所有的應用都可以忍受 RAM 資料丟失及系統重啟。

電源系統的考量

在多電源系統的應用上,必須考慮低功耗 MCU 的內部電源規劃或自動切換,以下以市電/備用電池雙電源系統及內建 USB 介面,但平常由電池供電的行動裝置來舉例說明。

市電/備用電池雙電源系統:MCU 平常由市電經由交直流轉換電路供電,當市電斷電時,經由連接在備用電源的獨立供電管腳進行供電,同時在 MCU 內部進行電源切割,并提供一個可靠的備用電源自動切換開關,確保市電正常供電時備用電池不會持續被消耗。但仔細考慮,其實有兩種狀況可能發生,一種是備用電池僅供電給部分低耗電的周邊電路,例如 32.768K 晶振、RTC 時鐘電路、資料備份寄存器等。當市電來時 MCU 將重新啟動。另外一種狀況是當市電斷電時,有可能 MCU 及部分周邊電路會被喚醒工作,然后再次進入待機模式。智慧型電表就是此類應用的典型代表。在此種應用中,備用電池需要供電給整顆 MCU,所以電源自動切換開關必須能承受更高的電流,相對成本也較高。

內建 USB 介面行動裝置:此類裝置平時由兩節電池供電或鋰電池供電,工作電壓可能為 2.2V 到 3V,當連接到 USB 時,USB介面轉由 VBUS 供電。此類低功耗 MCU 如果沒有內建 5V 轉 3V 的 USB 介面 LDO將會產生下列問題,當連接 USB 時必須由外掛的 LDO 將 USB VBUS 的 5V 電源轉換為 3V 電源同時提供給 MCU VDD及 USB 介面電路,但又必須避免 LDO 輸出的 3V 電源與離線操作時的電池電源發生沖突,將會需要外加電源管理電路,增加系統成本及復雜度。

豐富的喚醒機制及快速喚醒時間

有許多的系統應用場合,需要由外部的單一訊號、鍵盤或甚至串列通訊信號來激發 MCU 啟動整體系統的運作。在未被激發的時候,微控器或甚至大部分的整機需要處于最低耗電的待機狀態,以延長電池的壽命。能夠在各式需求下被喚醒,也成為微控器的重要特征。MCU 能擁有各式不同的喚醒方式,包括各I/O 可作為激發喚醒的通道,或是由I2C、UART、SPI的通道作為被外界元件觸發喚醒,或使用內、外部的超低耗電時鐘源,透過 Timer 來計時喚醒。諸多的喚醒機制,只要運用得當,并配合微控器的低耗電操作切換模式,可以使 MCU 幾乎時時處于極低功耗的狀況。

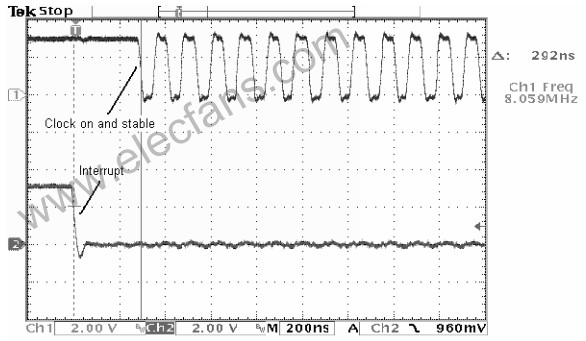

配有快速、高效率內核的 MCU,可以在每次喚醒的當下短暫時間里,完成應有的運作與反應,并再次進入深層的低待機模式,以此達到平均耗能下降的目的。但是,如果喚醒后開始執行微指令的時間因為某些因素而拖延的很長,將會使降低總體耗電的目標大打折扣,甚至達不到系統反應的要求。因此,有些 MCU,配合起振時間的改進,邏輯設計的配合,使得喚醒后執行指令的時間至少降到數個微秒之內。

低功耗類比周邊及存儲器

低功耗 MCU 在運行時除了 CPU 內核及被致能的數字周邊電路在工作外,越來越多被整合到內部的類比周邊電路也是耗電的主要來源。以最簡單的 while (1); 執行序來分析運行功耗,共包含下列耗電來源: CPU 內核、時鐘振蕩器、嵌入式閃存、及LDO 本身的消耗電流。代入以下典型值數據將會更清楚顯示各個部分對耗電的影響:

運行頻率 12MHz,MCU 電壓 3V,LDO 輸出 1.8V 供給 CPU 內核、記憶體及其他數字電路

低功耗Cortex-M0內核:600 μA

嵌入式閃存:1.5 mA

低功耗12MHz 晶震電路:230 μA

LDO本身的靜態消耗電流:70 μA

總和=0.6+2+0.23+0.07=2.4 mA,平均功耗約 200μA/MHz

其中耗電比例最高的是嵌入式閃存。如果要運行在更高頻率,通常會啟動內建的 PLL 提供更高頻率的時鐘源,在 1.8V 供電的典型 PLL,12MHz 輸入輸出 48 MHz工作電流約為 1 ~ 2mA,如果不能有效降低 PLL 耗電,對高頻工作的低功耗 MCU 將是一大電流負擔。

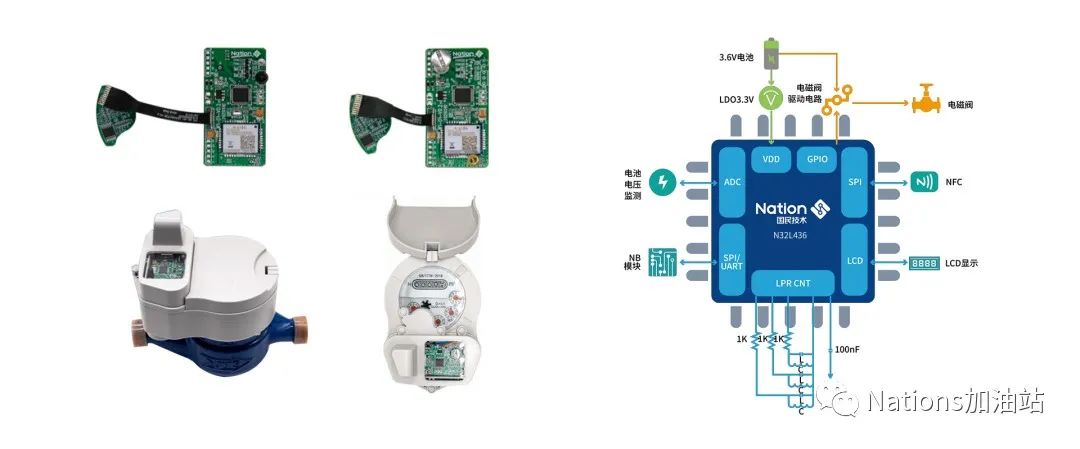

LDO 的最低靜態功耗、32.768 kHz 晶振電路、BOD 及 TN LCD 驅動電路的工作電流,都會大大影響到待機或 RTC 模式的功耗指標。以低功耗應用的熱能表為例,RTC 加 LCD 顯示的功耗要求在 3V/8μA 以下,這代表可以預估分配給下列電路的電流預算為:LDO靜態功耗 0.5μA + 32.768 kHz 晶振及RTC電路 1μA + BOD 1μA + TN LCD 驅動 4μA + LCD 玻璃 1μA + 所有數位電路及類比周邊漏電流 0.5μA。這些類比周邊除了低耗電要求,同時必須兼具要求批量生產及溫度變化時的一致性,這對類比設計人員將是一大挑戰。

快速喚醒這個性能指標也會影響到下列類比周邊的穩定時間。當 MCU 從低耗電的待機模式喚醒時,首先要將 LDO 快速切換到高供電模式,啟動內部高速 RC 震蕩器,使能嵌入式快閃記憶體及 CPU,以上所有電路的穩定時間總和必須在數個微秒內完成,才能符合快速喚醒的需求。

另外一個容易被忽略的設計是周邊電路啟動電流,因為相當多的可攜式裝置采用 CR2032 小型鋰電池,瞬間推動力僅有數 mA,尤其使用一段時間瞬間推動力會更低,當 MCU 被喚醒時果周邊電路啟動電流總和太大時,將會導致 CR2032 輸出電壓驟降而導致 MCU 重置 (Reset) 或工作不正常。為了避免此問題,除了降低周邊電路的啟動電流,另一種方法是分時分段啟動周邊電路,不要集中開啟太多耗電的電路。

平均功耗計算范例

為了讓讀者更具體了解平均功耗的計算,以新唐科技的低功耗 32位元 MCU Nano 系列及血糖計應用為例,進行使用年限的預估。新唐的 Nano 系列低功耗 32位元 MCU 的 CPU 內核為Cortex-M0,具有200uA/MHz低運行功耗、待機電流僅需1uA、7uS快速喚醒、多重時鐘訊號來源及多種工作模式,多達 128KB Flash、16K SRAM 及 12位元 ADC、12位元 DAC、SPI、I2C、I2S、UART、LCD、Touch Key 等豐富周邊,符合低功耗、高性能 MCU 應用需求。

此血糖計范例采用CR2032 230 mAh電池,使用方式、運行功耗及靜態功耗如下表所示。

使用年限的計算方式請參考下表。量測時間比例、顯示時間比例及待機時間比例可由上表求得。例如,量測時間比例為“6 次 x 0.25 分鐘 / (60 x 24) 分鐘 = 0.1%”。其余時間比例依此類推。量測平均電流為“量測時間比例 x (MCU運行耗電流 +外部量測電路耗電流 +待機(含RTC)耗電流 + LCD 耗電流 + CR2032 自放電)”。顯示平均電流為“顯示時間比例 x (待機(含RTC)耗電流 + LCD 耗電流 + CR2032 自放電)”。待機平均電流為“待機時間比例 x (待機(含RTC)耗電流 + CR2032 自放電)”。最后計算出使用年限約為 2.77年。由于待機時間比例高達 99%,故血糖計應用待機電流為延長使用年限最重要的參數。

結論

低功耗MCU設計是一個需要多面向考慮的復雜工作,本文僅闡述基本設計理念。開發低功耗MCU產品時,不只要挑戰電路設計的高困難度,更要由客戶應用的角度考慮性價比,功能最強的不一定是最好的。往往性價比最適合的才能在市場上取得成功。由于智能電網、物聯網、遠端控制、自動化管理等低功耗高效能應用需求量持續增加,在可以預見的未來,32位元低功耗MCU將逐漸取代8/16位元低功耗MCU,成為市場主流。

?

電子發燒友App

電子發燒友App

評論