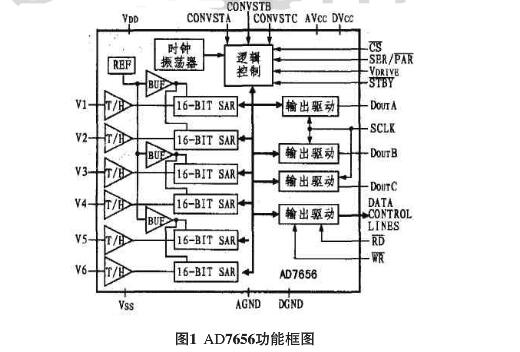

一、AD7656簡介

AD7656具有最大4 LSBS INL和每通道達250kSPS的采樣率,并且在片內包含一個2.5V內部基準電壓源和基準緩沖器。該器件僅有典型值160mW的功耗,比最接近的同類雙極性輸入ADC的功耗降低了60% 。

AD7656包含一個低噪聲、寬帶采樣保持放大器(T/H),以便處理輸入頻率高達8MHz的信號。該AD7656還具有高速并行和串行接口,可以與微處理器(mcu)或數字信號處理器(DSP)連接。AD7656在串行接口方式下,能提供一個菊花鏈連接方式,以便把多個ADC連接到一個串行接口上。

AD7656工作原理:

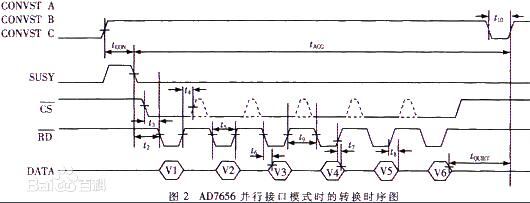

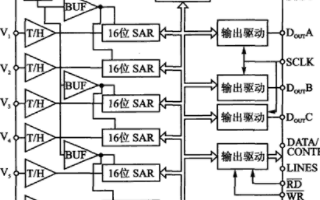

AD7656足具有獨立的六通道逐次逼近型(SAR)的模數轉換器,轉換處理和數據的精度是通過CONVST信號和一個內部晶振控制的。3個CONVST管腳允許3路ADC對獨立同步采樣。當3個CONVST管腳連接到一起時,就可以進行6個通道的同步采樣。 AD7656具有高速的并行和串行接口,允許其與Microprocessors和DSP進行接口。當使用串行接口模式時,AD7656具有的菊花鏈特性允許多個ADC和一個串行接口連接。由于在電力繼電保護產品中以并行接口連接設計為主,所以下面將以并行接口的連接方式介紹其工作原理。

首先,通過MCU或DSP控制CONVST管腳啟動轉換,并保持該信號為高電平。AD7656啟動轉換信號后會自動輸出BUSY信號,BUSY信號下降沿時,代表轉換已經全部完成。

此時,AD7656內部的6個寄存器中已經保存了轉換的數據,然后通過控制片選CS和讀RD信號依次順序讀出6個通道AD轉換值。 讀出AD轉換值后,改變CONVST為低電平信號。注意在設計時,一定要保證AD轉換過程中CONVST管腳保持高電平。

AD7656的應用:

當前,繼電保護產品在不斷地更新換代并改變著設計模式。最初由于工藝和芯片等各方面因素的影響,第一代電力繼電保護產品均采用模擬開關,配合單通道16bit的ADC設計,例如AD976,AD574等AD轉換器產品;后來出現了使用16bit的AD7665和14bit的AD7685配合模擬開關的第二代繼電保護產品,AD7665和AD7865在當前很多電力繼電保護產品中仍有非常成功的應用案例;隨著技術的更新和產品工藝的改進,尤其是其±10V雙極多通道同步輸入等技術特點,使AD7656有望成為電力繼電保護的新一代產品。

二、TMS320C6713簡介

TMS320C6713 DSP是美國TI于1997年推出的C6000系列DSP芯片的一款,它是32位高速浮點型DSP,時鐘最高頻率為300MHz。

TMS320C6713主要特點有:

(1)體系結構采用超長指令字(VLIW)結構,單指令字長為32位,指令包里有8個指令,總字長達到256位。執行指令的功能單元已經在編譯時分配好,程序運行時通過專門的指令分配模塊,可以將每個256位的指令包同時分配到8個處理單元,并由8個單元同時運行。其最大處理能力可以達到2400MIPS。

(2)采用二級緩沖處理,4KByte直接匹配的程序緩沖L1P,4KByte可匹配的數據緩沖L1D,256KByteL2額外匹配內存。32位外部存儲器接口,可無縫連接SRAM、EPROM、Flash、SBSRAM和SDRAM。

(3)豐富的外設,包括DMA,EDMA,支持無需CPU參與可以在允許的地址空間里傳送數據,擴展總線,具有主機口和I/O端口操作等功能,多通道緩沖串口,其通過配置能和多種串行通信接口通信,兩個32位通用定時器等。

三、模擬轉換電路設計

1、模擬轉換電路設計

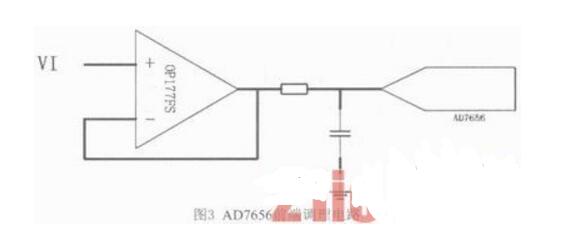

由于在綜合控制計算機采集的信號源與AD7656要求的輸入信號不匹配,所以對信號源的信號進行前端調理電路調整,在AD7656前端調理電路設計主要考慮了如下因素:

(1)阻抗匹配。由于輸入信號的信號源不一定是低阻抗,AD7656的輸入端很可能會對信號源信號分壓,從而影響采集轉換信號的精度。在AD7656前級輸入采用運算放大緩沖器解決該問題,因為運算放大緩沖器具有很高的輸入阻抗,因此不會對信號源分壓,同時它的低輸出阻抗適合驅動AD7656的輸入端;

(2)減小容性負載的影響。AD7656輸入端具有容性負載特性,通常需要一個電阻和電容組成外部補償電路,采用該電路給信號源增加了容性負載。

AD7656前端調理電路設計見圖3所示。AD7656前端調理電路采用的運算放大緩沖器為ADI公司的OP177FS,其具有低輸入失調電壓(25μV),失調電壓時間漂移最大0.1μV/℃,開環增益最小12V/μV,電源電流2.0mA。

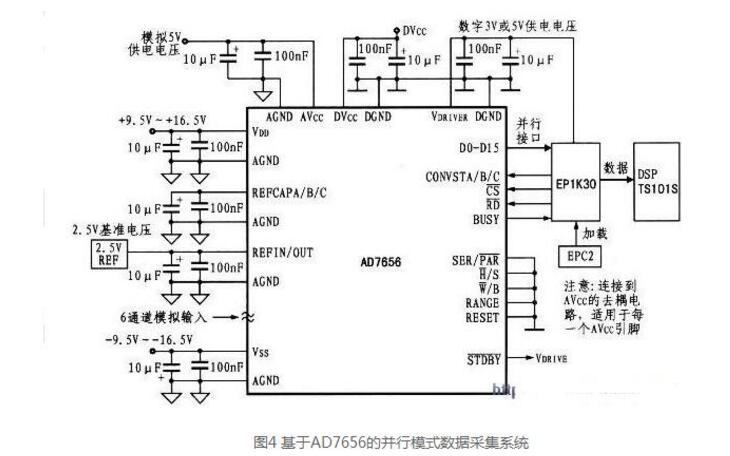

2、AD7656與TMS320C6713B接口電路設計

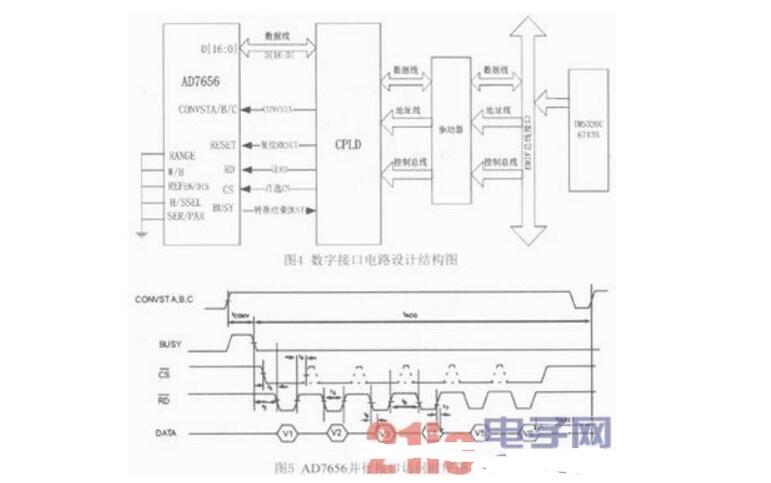

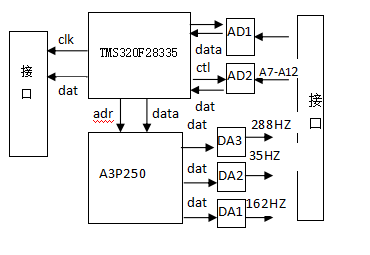

AD7656與TMS320C6713B接口電路采取并行接口設計。在電路設計時將AD7656的“SER/PAR”管腳設置為并行接口方式,“W/B”管腳設置為字方式,“H/SSEL”管腳設置為硬件啟動轉換方式。TMS320C6713B通過外部存儲器接口(EMIF)總線實現對AD7656訪問,啟動對AD7656轉換,讀取轉換結果數據,接口電路結構圖見圖4所示。

TMS320C6713B通過CPLD實現對AD7656控制邏輯譯碼,來滿足AD7656的訪問時信號的邏輯要求,AD7656訪問時序圖見圖5所示。

AD7656包括6通道ADC轉換,可實現6通道ADC同步轉換,減少了多路ADC轉換采樣時間。在CPLD邏輯設計中采用同時控制“CONVSTA”

“CONVSTB”“CONVSTC”管腳輸出有效完成6通道ADC通道同步轉換。

根據圖5所示AD76565通過“CONVSTA,B,C”信號的上升沿啟動ADC轉換,ADC轉換過程中,“BUSY”信號為邏輯“高”標識,ADC正在轉換過程中,ADC轉換時鐘由內部時鐘產生,從“CONVSTA,B,C”信號的上升沿啟動轉換3μs后ADC轉換結束,“BUSY”信號為邏輯“低”表示ADC轉換結束。TMS320C6713B通過EMIF總線接口完成對轉換結果的讀取。對AD7656芯片轉換結果讀取,通過“CS”片選信號和“RD”讀信號控制,6個通道轉換結束后,TMS320C6713B控制“CS”為有效和6個“RD”讀有效信號,完成對模擬量輸入“V1”信號、“V2”信號、“V3”信號、“V4”信號、“V5”信號、“V6”信號轉換結果的讀取。

3、AD7656設計中應注意問題

3.1電壓基準電路設計

由于AD7656轉換的精度與參考電壓基準電壓的精度有很大關系,參考電壓基準輸出電壓值用來確定數據轉換系統的滿量程輸入范圍,同時參考電壓基準電壓的任何誤差都會嚴重影響ADC的線性和無雜散動態范圍。

由于AD7656內部集成的電壓基準參數精度低,一般在對于分辨率大于12位的ADC應用中采用高精密外部電壓基準,本設計采用高精密外部電壓基準AD780BR作為AD7656轉換的電壓基準。通過表2對兩種電壓基準參數比較,看出外部高精密電壓基準精度高,具有更低的溫度系數、熱遲滯和長期漂移。

四、PCB設計

1、數\模區域分割

在高速AD采集電路的設計中,達到高精度與PCB設計是密不可分的,所以進行PCB設計過程中,按照電路實現的功能可以簡單地劃分為數字電路和模擬電路兩部分,將數字區域與模擬區域進行分割,形成每個區域的獨立電源和地,這樣可以有效抑制干涉的傳導和RF能量的輻射。

AD7656芯片在管腳定義時將模擬量和數字量信號按區域定義,有利于PCB設計中數字量和模擬量區域分割,布線時注意模擬信號區域布模擬信號線,數字信號區域布數字信號線,不要將數字信號線和模擬信號線并行布線。

在本系統中模擬地和數字地采用一個電勢參考點,所以模擬地和數字地采用單點共地,共地點盡可能地靠近AD7656。

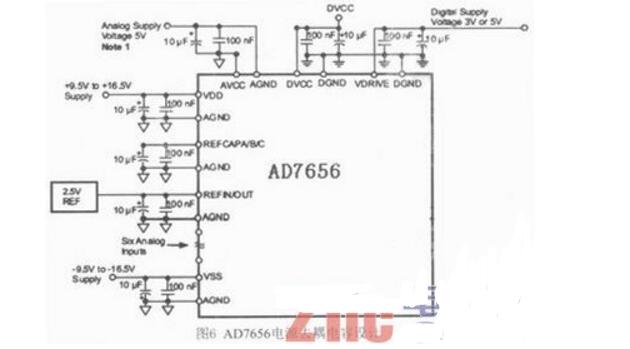

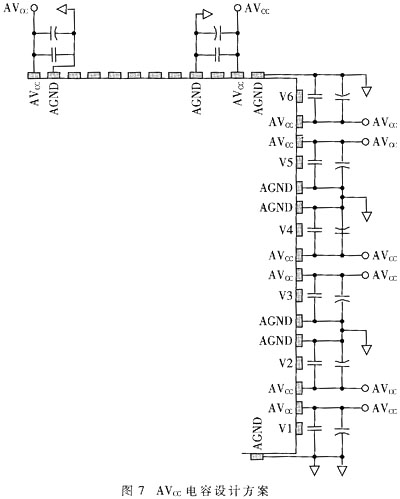

2、電源去耦設計

由于AD7656芯片存在多個電源管腳,在每個電源管腳需要連接去耦電容。去耦電容的設計中采用并聯100nF和10 μF電容。電容選擇時可選用具有小等效串聯電感(ESL)瓷介質電容。AD7656的去耦電容設計見圖6所示。

五、AD采集軟件設計實現

TI公司提供良好的C/C++編譯器,在TMS320C6713B軟件開放過程中支持C/C++語言設計。并且提供的良好的庫函數(DSPLIB),支持TMS320C6713B的數學運算和矢量運行。

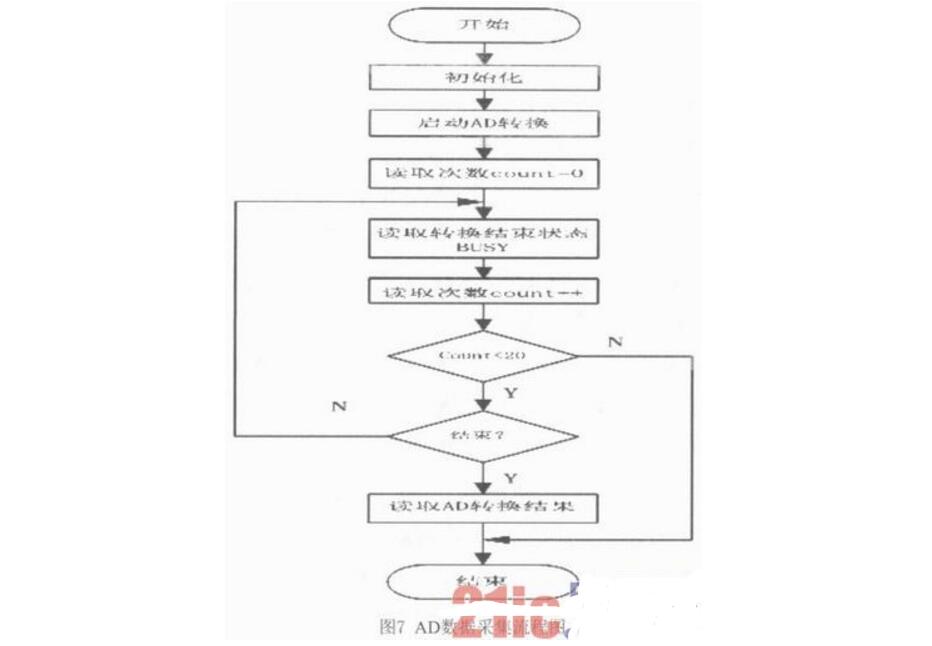

采集軟件設計采用了模塊化設計,主要包括初始化函數、AD7656轉換啟動函數和AD7656轉換結果讀取函數。

初始化函數實現對TMS320C6713B系統時鐘、EMIF總線時鐘配置,EMIF總線接口訪問時序的配置。通過該初始化函數配置,配置CS(片選)RD讀信號相對時序關系,滿足AD7656訪問時序關系。

AD7656轉換啟動函數實現啟動AD7656的AD轉換,該函數控制AD7656轉換啟動信號CONVSTA,B,C為有效狀態,同步6路AD轉換。

AD7656轉換結束標識查詢函數實現對AD7656轉換狀態標識信號BUSY查詢,判斷AD7656內部ADC轉換是否結束。

AD7656轉換結果讀取函數實現檔查詢到AD轉換結束標識后,讀取AD轉換結果。該函數通過連續的6次讀操作,讀取6路AD同步轉換結果。AD采集軟件流程見圖7所示。

六、結束語

針對要求高精度、多路信號監測和實時采集,本設計選用了AD7656和TMS320C6713B相結合作為某控制系統工作狀態實時監控以及故障檢測系統方案,本設計接口電路設計簡單,采集精度高、速度快,可同時完成對多路信號的采集。系統聯試證明,本系統完全滿足某控制系統對工作狀態監控以及故障檢測信號的采集精度和實時性的要求。

電子發燒友App

電子發燒友App

評論